一、实验配置

详细配置请点击测试一链接:

测试一:通过1000M网口pc电脑同fpga进行udp通信,用window自带的任务管理器测网速,测得发送数据速度>200Mbps(一)

测试二为pc机单向发送多线程测试,速度573Mbps左右,详情请点击下面链接。

测试 二:

通过1000M网口pc电脑同fpga进行udp通信,用window自带的任务管理器测网速,测得发送数据速度>573Mbps(二)

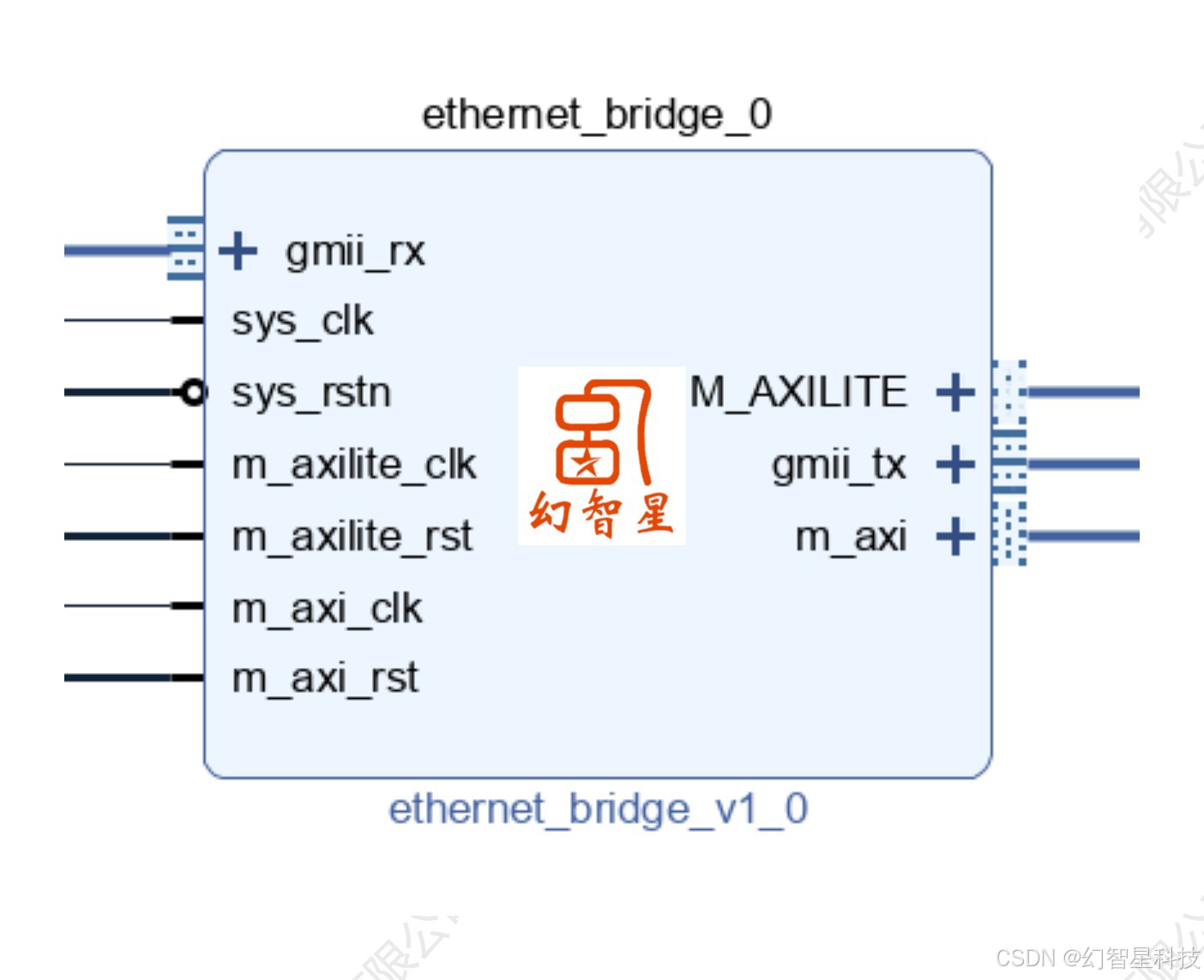

二、 fpga udp 协义ip核(DMA/Bridge Subsystem for Ethernet interface)

udp 协义ip核详情请点击:DMA/Bridge Subsystem for Ethernet interface 慨述

三、pc机多线程测试代码

三、pc机多线程测试代码

/*

公司:杭州幻智星科技有限公司

email: yupc123@qq.com

作者:俞工

*/

void ram_writetest(MstarUdpClient* pdev, uint32_t address, int datlen) {

auto pstr_buf = std::make_unique<uint8_t[]>(datlen);

init_testbuf(pstr_buf.get(), datlen);

//int i = 0;

int ret;

while (1) {

ret = pdev->axi_full_write(address, pstr_buf.get(), datlen);

if (ret < 0)

{

//handleError("axi_full_write fail!");

std::cout << "axi_full_write fail!" << std::endl;

break;

}

}

}

void ram_readtest(MstarUdpClient* pdev, uint32_t address, int datlen) {

auto pstr_buf = std::make_unique<uint8_t[]>(datlen);

int ret;

while (1) {

ret = pdev->axi_full_read(address, pstr_buf.get(), datlen);

if (ret < 0)

{

//handleError("axi_full_write fail!");

std::cout << "axi_full_read fail!" << std::endl;

break;

}

}

}

int main(void)

{

MstarUdpClient Mstar_dev;

if (Mstar_dev.udpClient_Open("192.168.1.10") < 0) { //初初化udp端口

handleError("Open Client fail!");

}

//ram_writetest(Mstar_dev, BROCK_RAM_BASEADDR, 1024*4); //测试一使用的单线程

std::thread pth0= std::thread(ram_writetest2, &Mstar_dev);//写线程一

std::thread pth1 = std::thread(ram_writetest2, &Mstar_dev);//写线程二

std::thread pth2 = std::thread(ram_writetest2, &Mstar_dev);//写线程三

std::thread pth3 = std::thread(ram_writetest2, &Mstar_dev);//写线程四

std::thread pth4 = std::thread(ram_readtest2, &Mstar_dev); //读线程

std::thread pth5 = std::thread(ram_readtest2, &Mstar_dev); //读线程

std::thread pth6 = std::thread(ram_readtest2, &Mstar_dev); //读线程

std::thread pth7 = std::thread(ram_readtest2, &Mstar_dev); //读线程

std::thread pth8 = std::thread(ram_readtest2, &Mstar_dev); //读线程

std::thread pth9 = std::thread(ram_readtest2, &Mstar_dev); //读线程

std::thread pth10 = std::thread(ram_readtest2, &Mstar_dev); //读线程

std::thread pth11 = std::thread(ram_readtest2, &Mstar_dev); //读线程

pth0.join();

pth1.join();

pth2.join();

pth3.join();

pth4.join();

pth5.join();

pth6.join();

pth7.join();

pth8.join();

pth9.join();

pth10.join();

pth11.join();

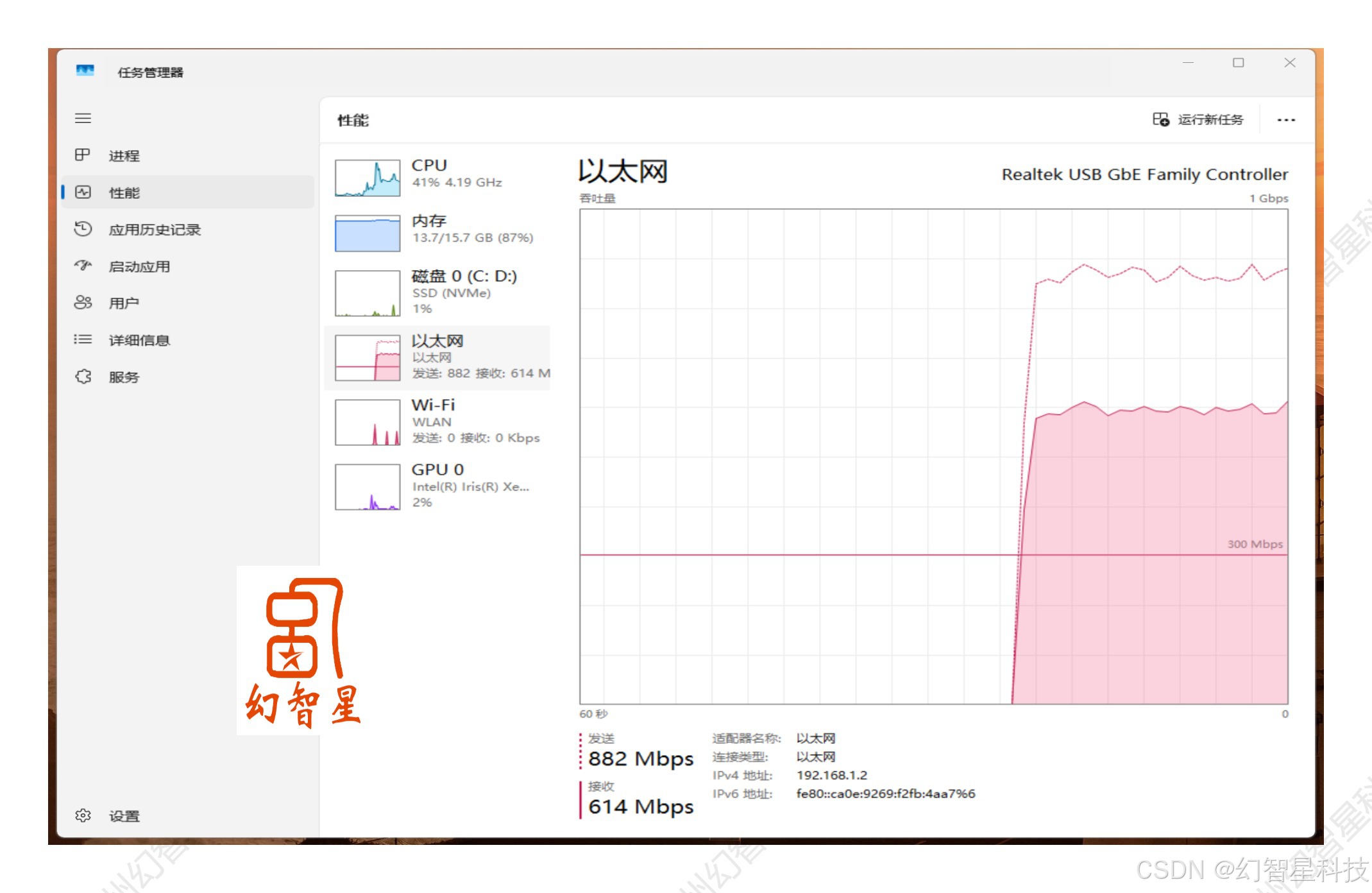

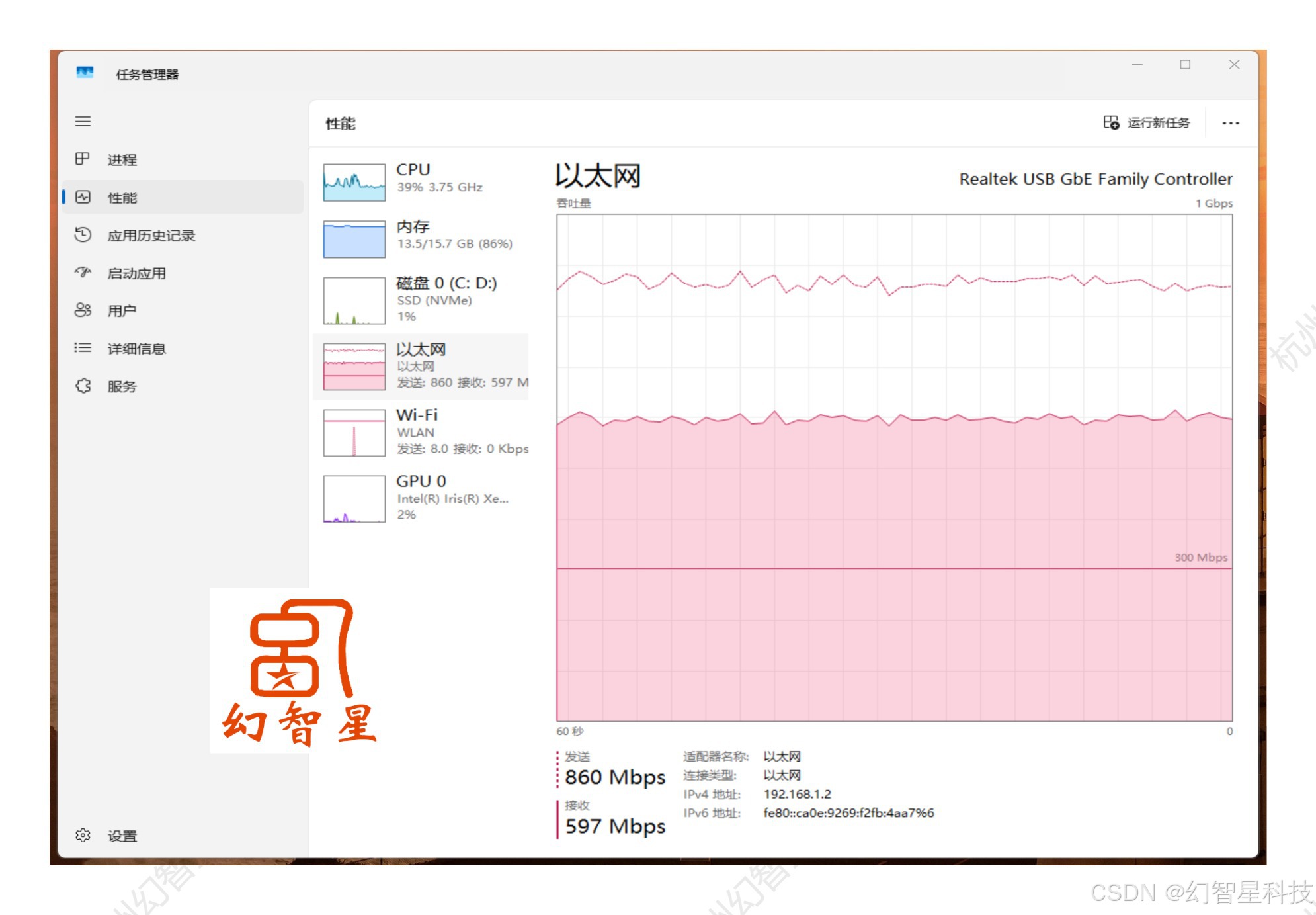

}四、测试结果

window 任务管理器测试结果如下:

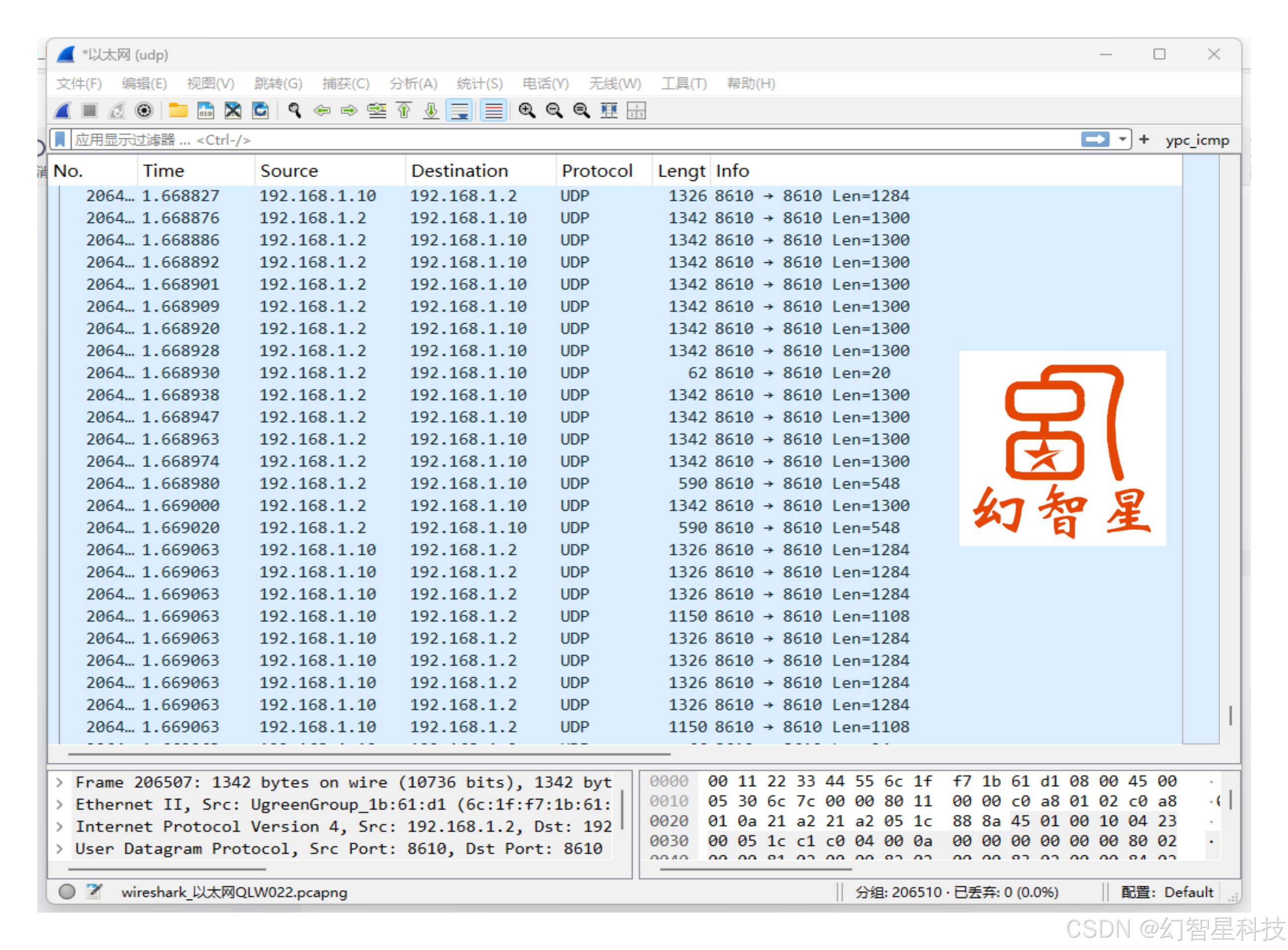

用wireshark软进行验证如下图:

五、三次实验总结

| 序号 | 数据方向 | pcs机线程数 | 速度 |

| 测试一 | 只写 | 单线程写 | 200Mbps |

| 测试二 | 只写 | 4线程写 | 573Mbps |

| 测试三 | 读写 | 8线程读4线程写 | 882Mbps |

单线程慢很多,通过wireshark软件分析确认,fpga返回的确认包有几ms的延时,虽说pc机同fpga是直联,这个延时对速度的影响很大。但是不明白测试二同测试三,pc机发送数据的速度为什么相差这么大?

六、实验问题

1、为什么只有发送数据线程,测得速度只有573Mbps?反而双向测试时速度能达882Mbps

3198

3198

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?