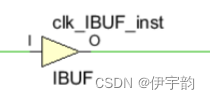

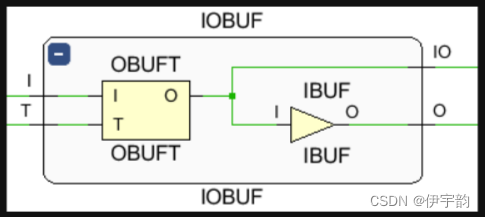

1、IBUF : FPGA上所有的输入信号必须进过IBUF,vivado会自动给所有输入信号分配IBUF

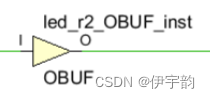

OBUF:FPGA上所有的输入信号必须进过IBUF,vivado会自动给所有输入信号分配OBUF

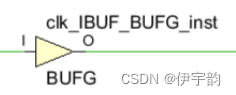

BUFG:专用时钟的资源,目的是减少时钟抖动、增强时钟的驱动能力,vivado不会给信号自动分配BUFG

在vivado如何调用呢?

如下图

IBUFG: IBUFG = IBUF + BUFG;

BUFH:即为水平时钟缓冲器,它相当于一个功能受限的BUFG很少使用。优点就是功耗低

BUFGCE:CE为时钟使能信号,相当于在BUFG上面添加了使能在CE有效的时候,才输出时钟BUFHCE:CE为时钟使能信号,相当于在BUFH上面添加了使能在CE有效的时候,才输出时钟

2、一般外部晶振的时钟走专用时钟管脚,进入FPGA, FPGA内部将这个时钟送入PLL,可以分频得到更多不同频率的时钟

3、一些外设提供给FPGA的时钟,比如摄像头提供给FPGA的像素时钟pix_clk,在设计时候,很大可能走的不是专用时钟管脚。如果走的不是专用时钟管脚,建议这个时钟过一个BUFG。

4,当时钟级联时,前一时钟已经经过了一个BUFG,那么后一时钟就选择 NO Buffer。

2543

2543

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?