复位

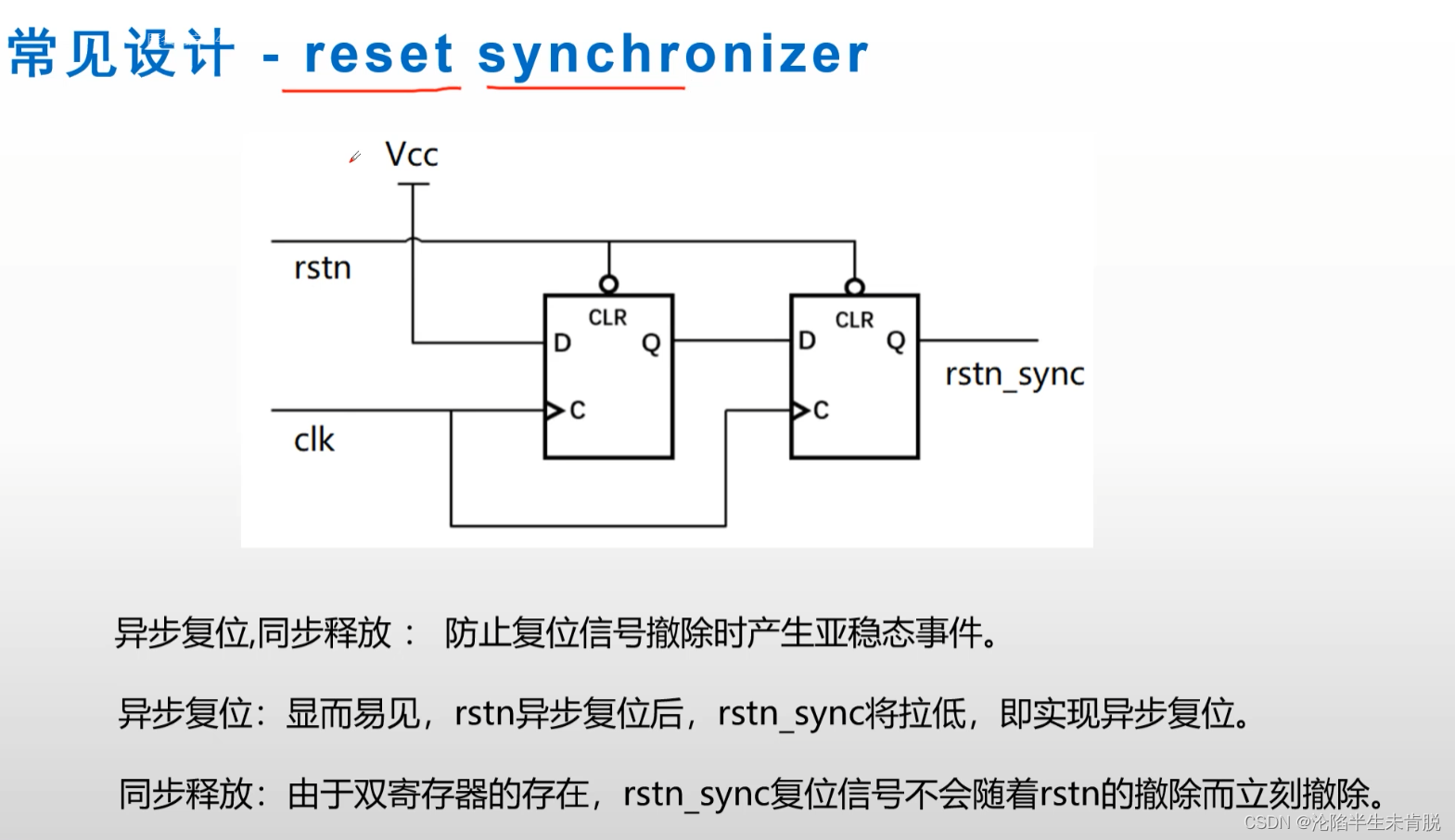

异步复位信号来时与时钟状态无关,直接复位,撤除复位信号时候,等待下个时钟沿同步撤除,防止产生亚稳态。

rstn:复位信号

rstn_sync:同步后的复位信号

异步复位,同步释放:当复位信号有效时,立即复位,与时钟边沿无关;当撤去复位信号时,同步释放可防止产生亚稳态事件。 信号名:rstn_sync

异步复位:rstn异步复位后,rstn_sync(同步过后的复位信号)拉低,实现异步复位

同步释放:由于双寄存器存在,rstn_sync复位信号不会随着rstn的撤除而立刻撤除

激励代码

initial

begin

#2

rstn = 0 ;

clk = 0 ;

#50

rstn = 1 ;

#48

rstn = 0;

#150

rstn = 1;

#200 $finish;

end

parameter CLK_FREQ = 100 ;//Mhz

always # ( 1000/CLK_FREQ/2 ) clk = ~clk ;

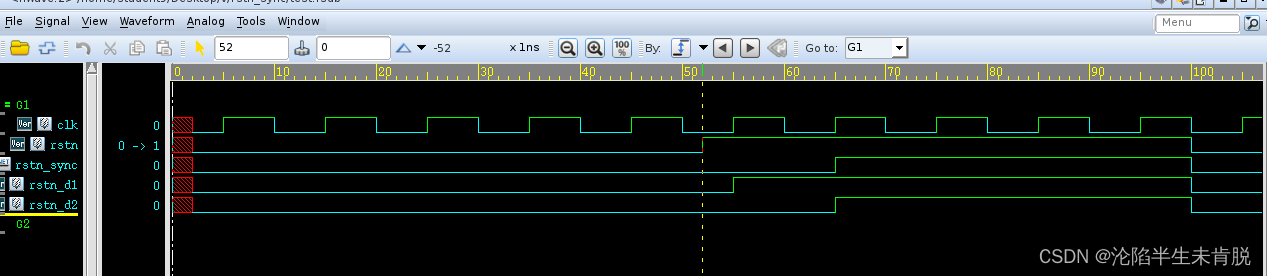

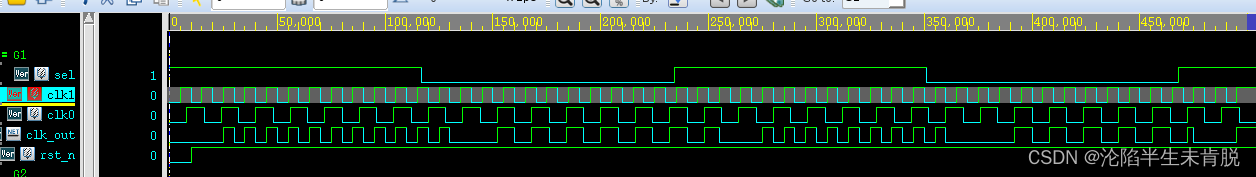

仿真图

rst_n:异步复位信号,与时钟沿无关

rstn_sync:异步复位,同步释放,撤除时与时钟上升沿同步

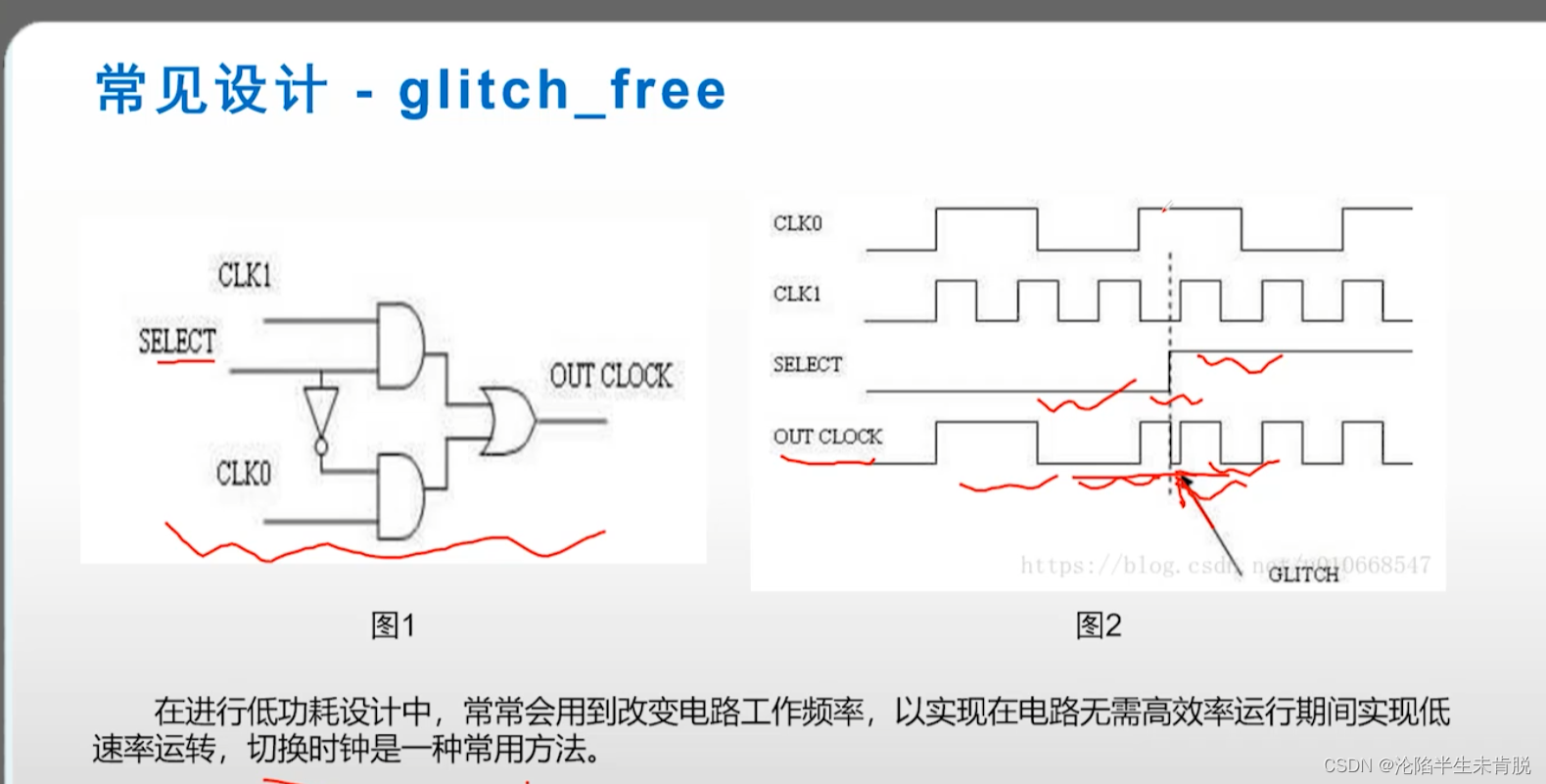

时钟无毛刺切换电路

在进行低功耗设计中,常常用到改变电路工作频率,以实现电路无需高效率运行期间实现低速率运转,其中切换时钟是一种常用方法。

当select从0切换到1时,时钟就从clk0切换到clk1,切换时间不对,会引起一个短暂的脉冲尖峰,出现了输出时钟不完整的情况,这个毛刺很可能驱动电路,或者产生其他亚稳态影响。

解决思路:当两个时钟都为低电平时再切换时钟。

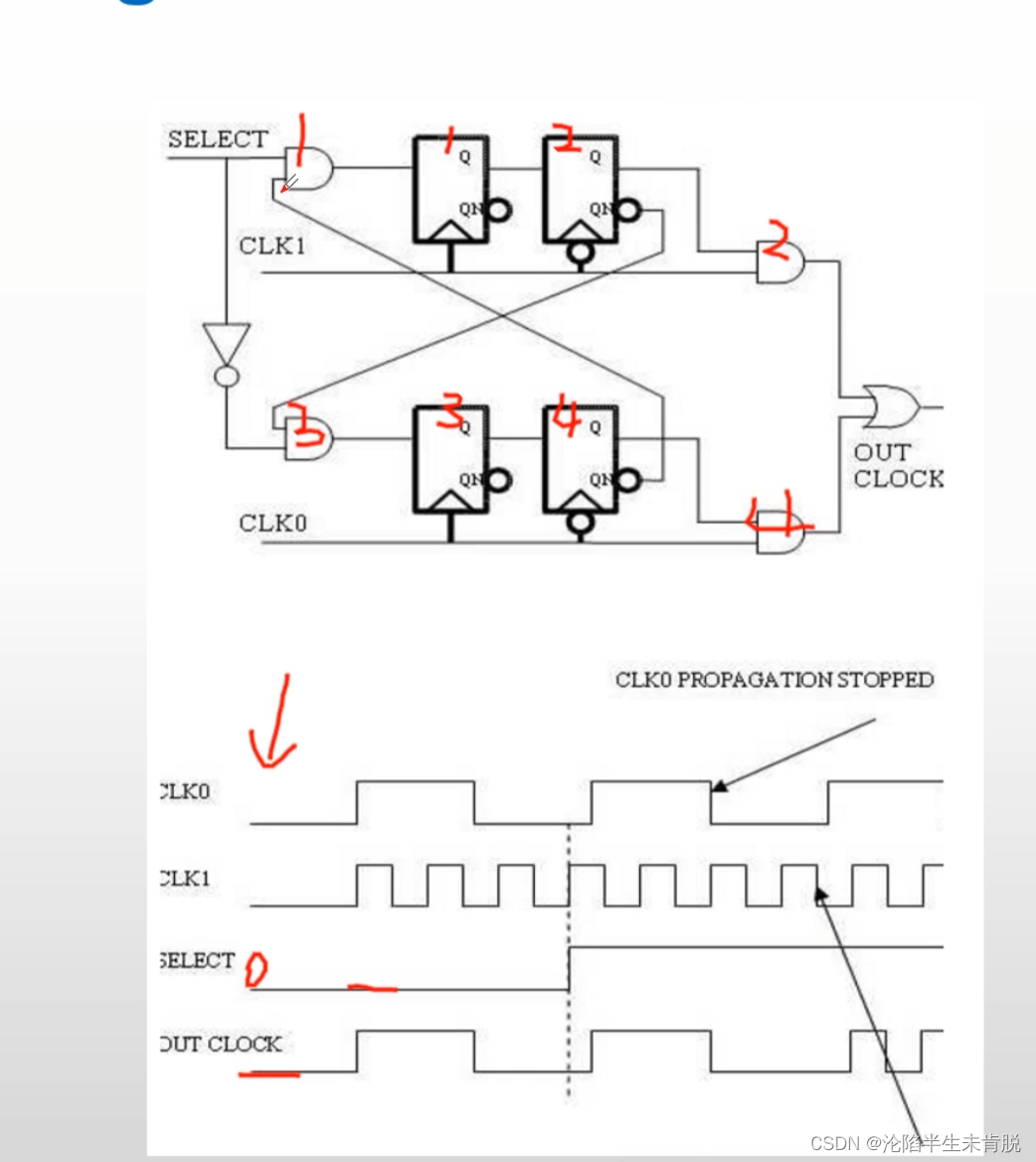

逻辑原理分析

四个触发器d1d2d3d4,以及四个与门。触发器12由clk1边沿触发,触发器34由clk0边沿触发。一开始电路全复位状态都为低电平。

- 当clk01开始工作后,sel=0低电平,此时与门1输出为0,则触发器12分别在ckl1的边沿输出Q的值,即与门1的输出0;此时,与门3由!sel和!and2逻辑值为1,故与门4输出1与clk0的逻辑值,说明电路此时工作频率为clk0;

sel=1时,与上述相反 - 逻辑关系

d0 = sel & !d3;

d1 = d0;

d2 = !sel & !d1;

d3 = d2;

clk_out = (d1 & clk1 ) | (d3 & clk0)

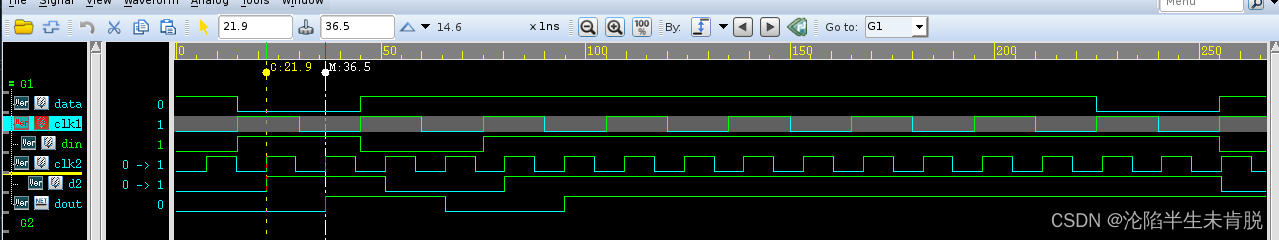

仿真图

当sel=1时,clk_out为clk1,sel=0时,clk_out=0。实现了无毛刺切换频率。

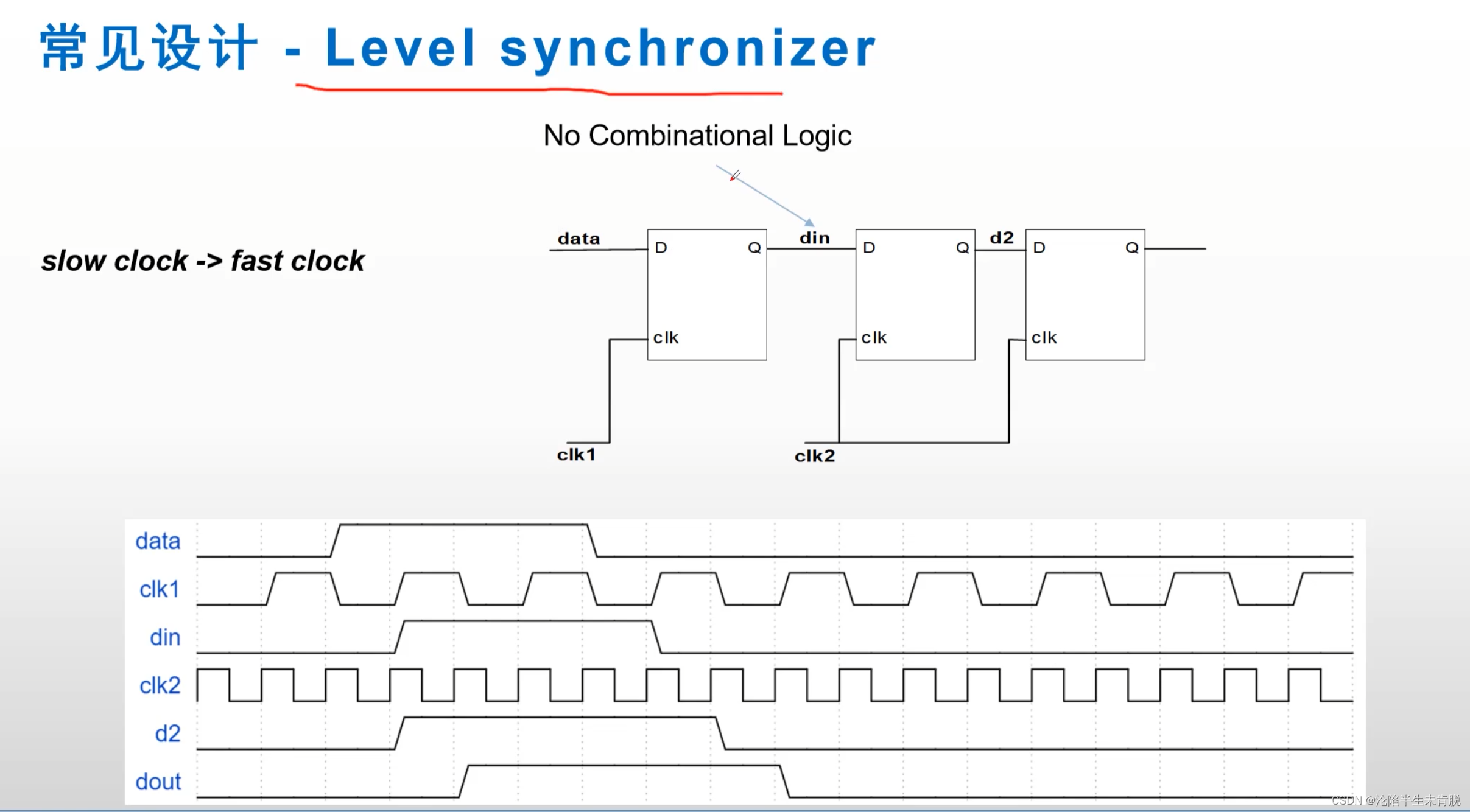

电平同步器(跨时钟域问题)

当一个设计中有多个异步时钟时,即有工作在两个时钟下的不同模块交互数据时,由于时钟的相位关系,容易对建立/保持事件产生影响。

要求输入数据时间大于要交互的另一个时钟周期加建立时间,即数据要长,实现慢时钟域到快时钟域的同步。

clk2采集din的第一个电平时,很容易产生亚稳态;dout接受d2的数据时已经稳定,d2不会产生亚稳态;

逻辑原理分析

三个触发器dind2d3,当clk1和clk2分别作用时

din <= data;

d2 <= din;

dout <= d3;

q = dout;

写激励时用到的系统函数

{$random}%2; 从0:[2-1]产生随机数;写在always块内,每次上升沿来随机给data赋初值1位bit的01。

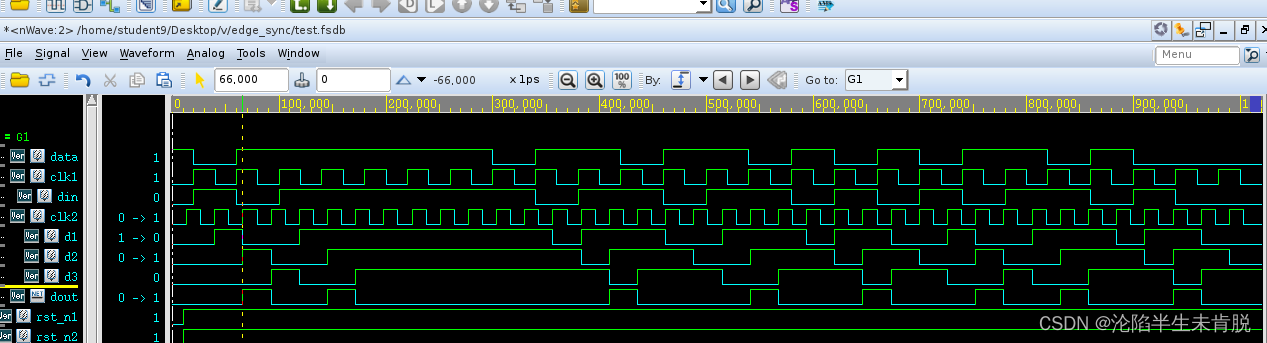

仿真图

d2与dout相差一个clk2的周期 7.3*2 = 14.6秒

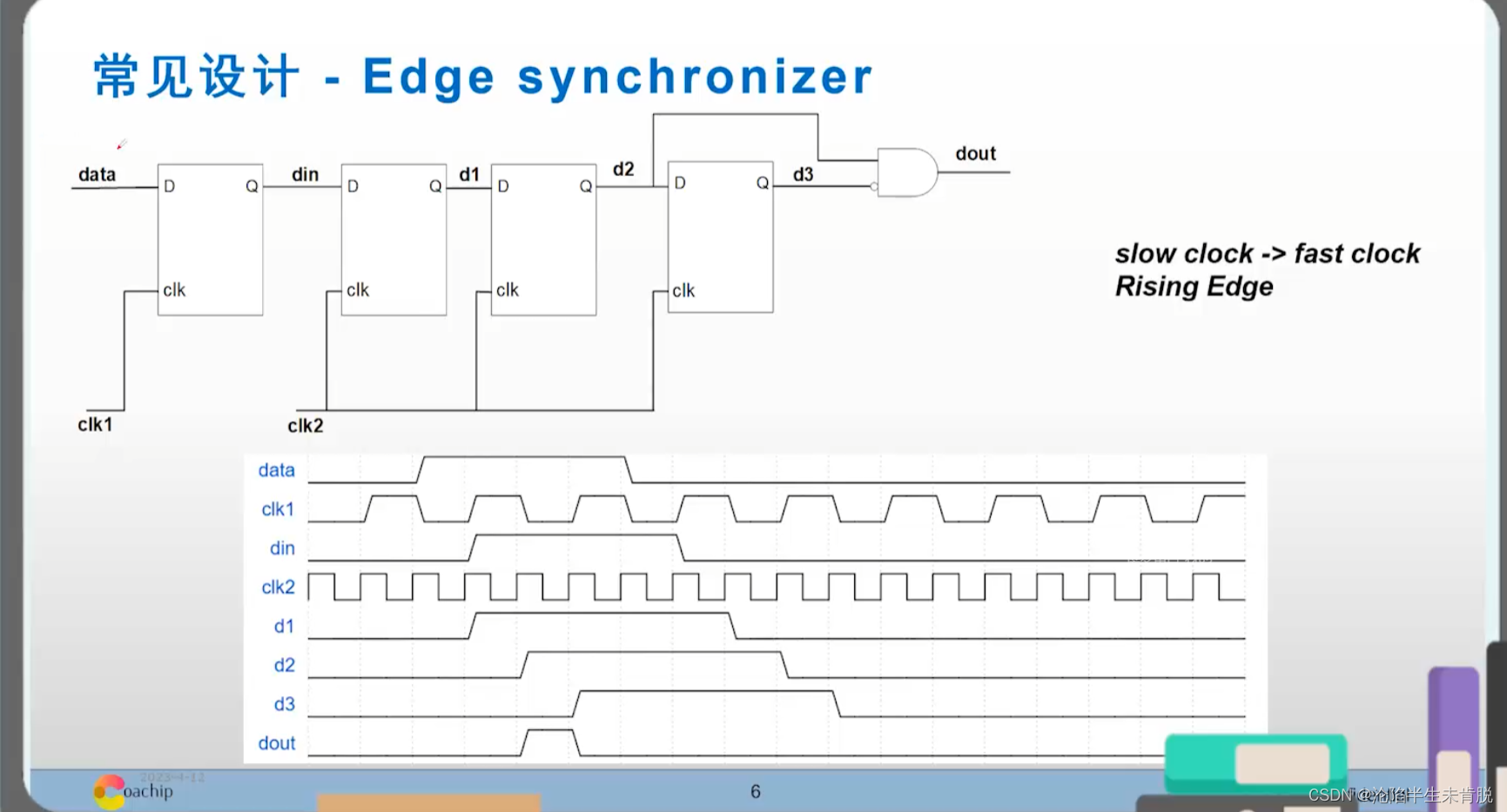

边沿同步器

同步过来的信号有严格的边沿要求,用边沿同步器,也是适用于慢时钟到快时钟域。

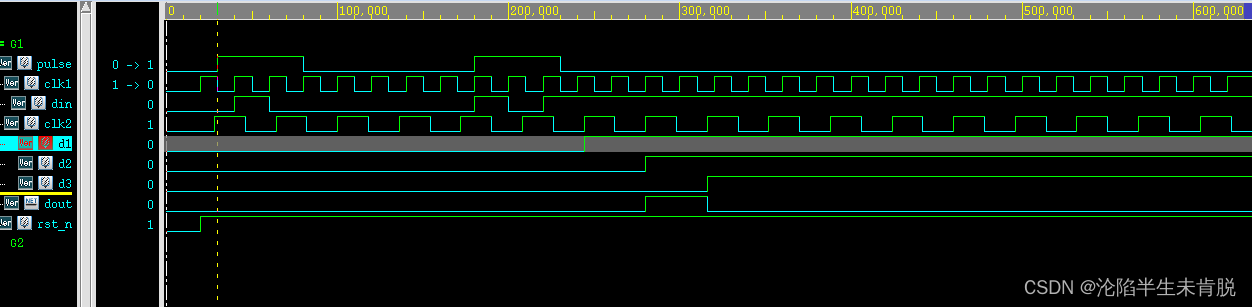

dout前的与门,输入为d2和d3非,其中d3非落后与d2一个时钟周期,即d2发生上升沿跳变后,d3还处于低电平状态,此时玉门的逻辑值dout为1,即检测到上升沿;若要检测低电平,与门的输入为d2非和d3。边沿信号有效时,在传输d2,电平同步的输出值。

逻辑分析

前三个触发器与电平同步一样,最后一级dout = d2 & !d3;

仿真截图

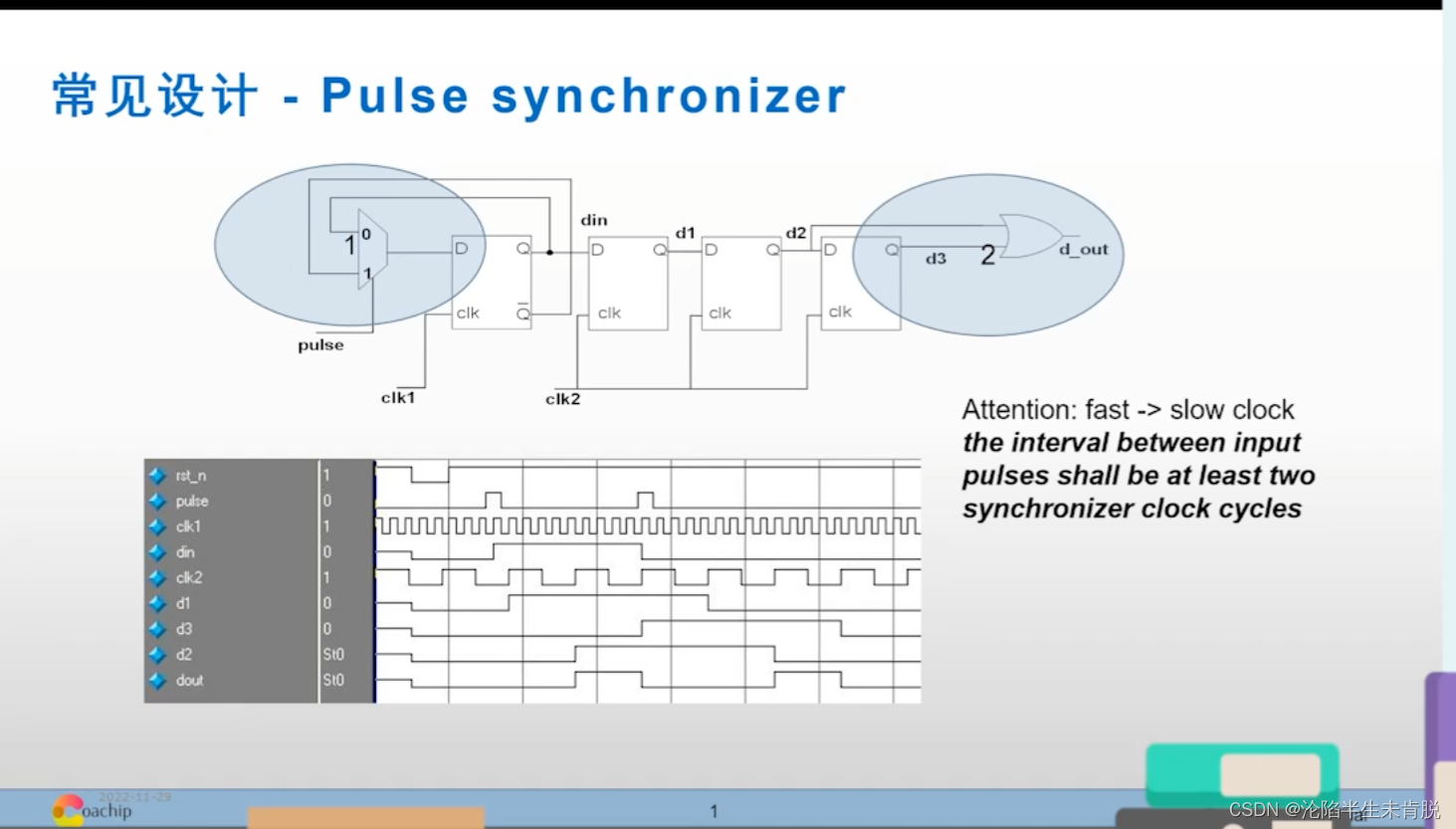

脉冲同步器

由快时钟域传数据到慢时钟域的用法。

脉冲同步器的输入是一个单时钟宽度的脉冲信号。简单来说,每来一次pulse的上升沿,反转dout。

脉冲同步器对脉冲的间隔有严格要求。输入脉冲的最小间隔必须等于大于新的时钟周期。

仿真图

仿真激励

initial begin

#0 pulse = 0;

#20

#10 pulse = 1;

#50 pulse = 0;

#100 pulse = 1;

#50 pulse = 0;

#400 $finish;

end

pulse持续时间要50ns,40ns触发器数都为0。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?