一、含义解释

“海力士DDR4颗粒编码一共14位。前4位基本是固定的,不用看,我们看后10位——AG8NMJRVKC(第5-第14位)。第5、6、7位表示颗粒容量参数,这里AG8表示颗粒16GbX8。第8位,表示Die的封装方式,这里N表示非TSV高密度封装。第9位,表示DIE的批次,这里是M,表示1st,第一等级/批次。第10位,表示封装类型,这里J,表示倒装。第11位,表示封装材料,这里R表示,无铅无卤符合ROHS标准。第12、13位,表示速度,这里VK表示DDR4-2666 19-19-19。第14位,表示工作温度和能源消耗,这里C,表示适合工作环境0-85摄氏度(消费级颗粒),能源消耗正常。”

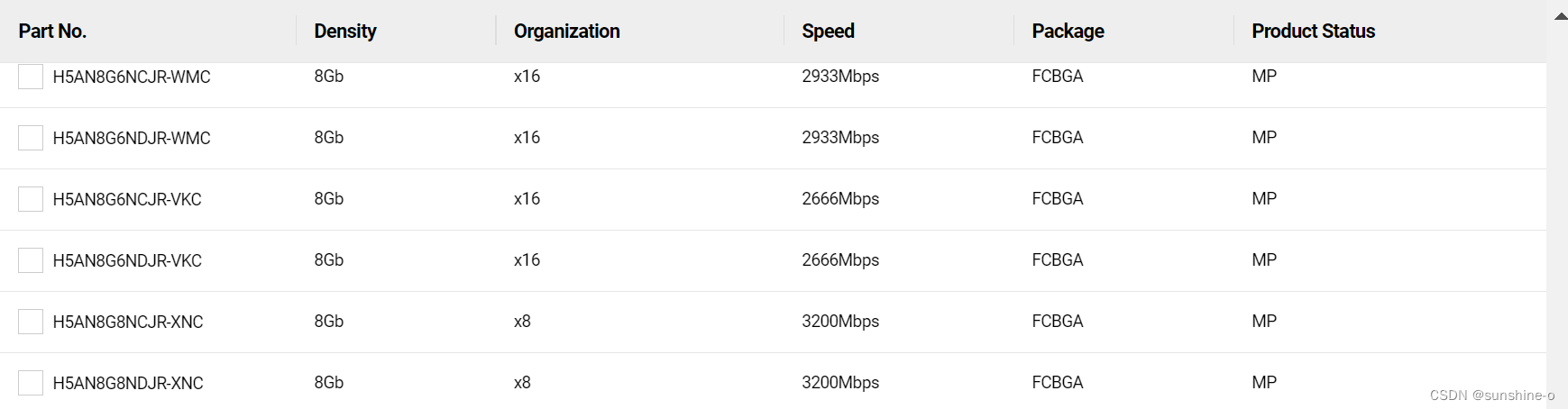

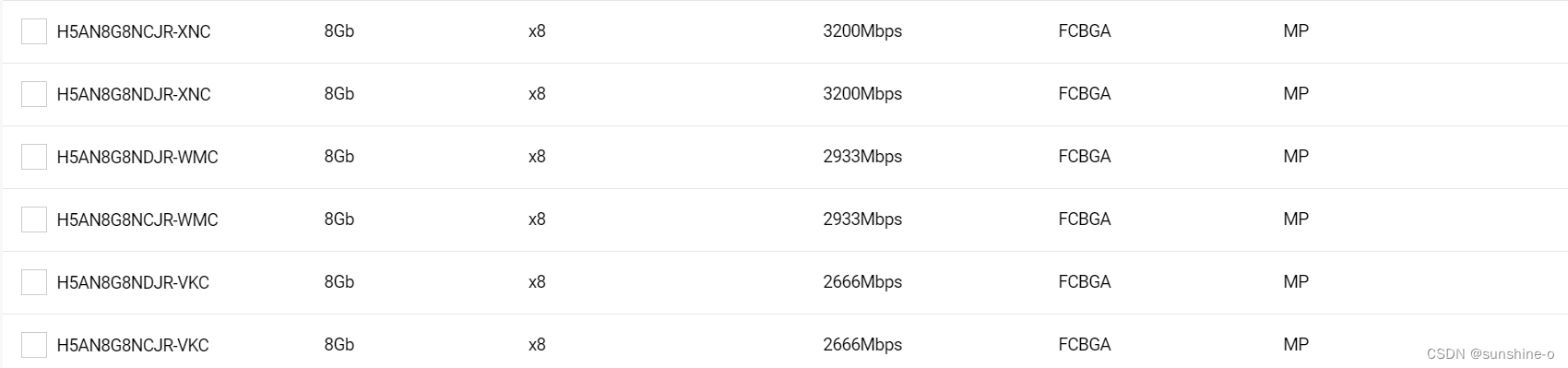

二、官网截图

路径:海力士–PRODUCTS–DRAM–DDR–DDR4

本文详细解析了海力士DDR4内存颗粒的14位编码规则,包括容量、封装、批次、速度和温度/能耗指标,以帮助用户理解和辨识不同规格的颗粒。

本文详细解析了海力士DDR4内存颗粒的14位编码规则,包括容量、封装、批次、速度和温度/能耗指标,以帮助用户理解和辨识不同规格的颗粒。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?