6.实验内容及步骤

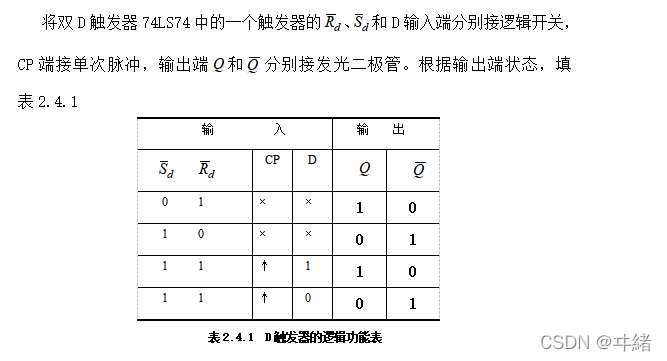

(1)D触发器逻辑功能测试。

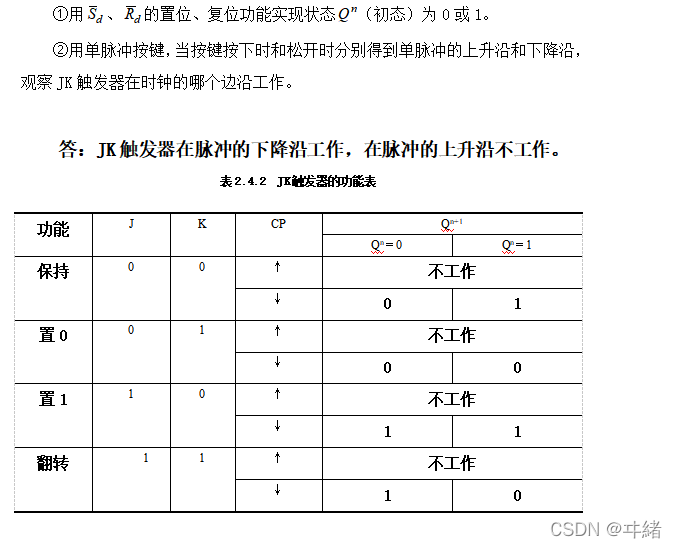

(2)JK触发器逻辑功能测试。

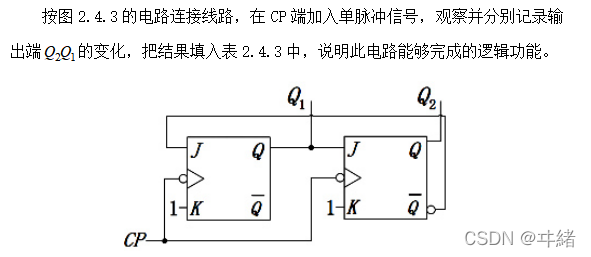

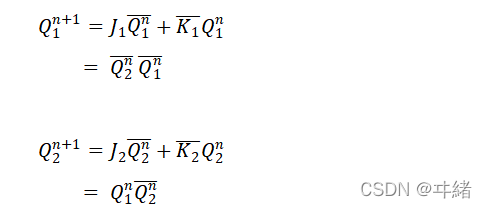

(3)时序逻辑电路搭设及测试。

状态方程组:

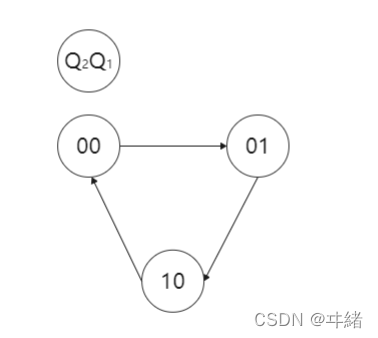

状态转换图:

| CP | Q2 | Q1 |

| 0 | 0 | 0 |

| 1 | 0 | 1 |

| 2 | 1 | 0 |

| 3 | 0 | 0 |

表2.4.3 时序逻辑电路状态

(4)D触发器的应用 (74LS74-2D触发器、74LS174-6D触发器)。

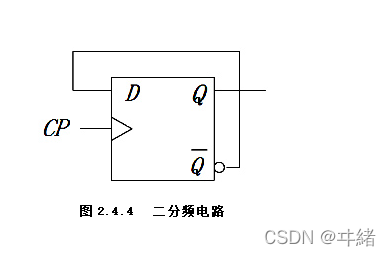

①图2.4.4是用D触发器组成的二分频电路,在CP端加入1kHz连续脉冲信号,用双踪示波器同时观察输入脉冲和输出端Q端的波形。记录两个波形图。

答:绿色为输入的1KHz连续脉冲信号的波形,红色的为D触发器的Q输出端的输出信号波形。

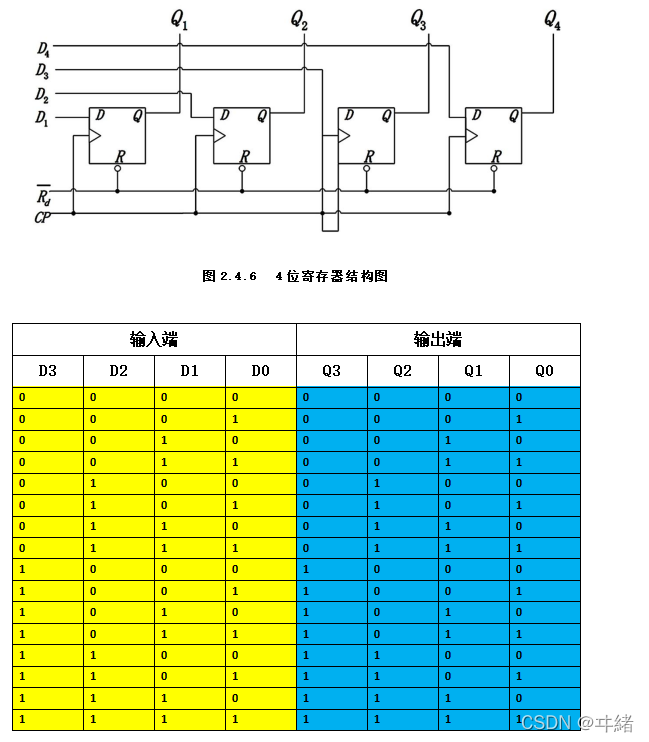

②用4个D触发器组成4位并行寄存器如图2.4.6所示(使用74LS174-6D触发器构成电路)。清零后给数据输入端输入D1D2D3D4数据,在CP端加单脉冲,观察输出端Q1Q2Q3Q4的变化。制表记录几组数据。

答:根据电路图和真值表可以看出,这个逻辑电路是可以实现并行输入的功能。

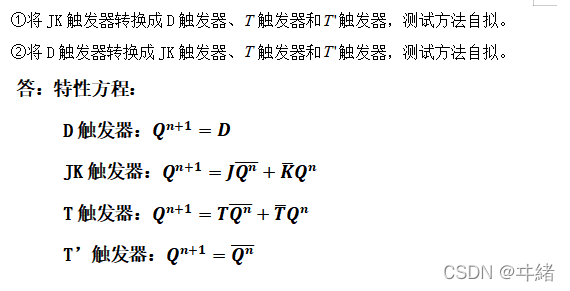

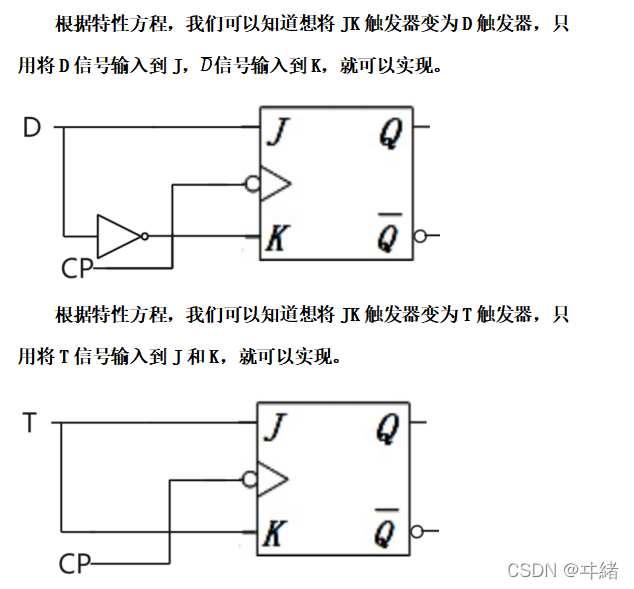

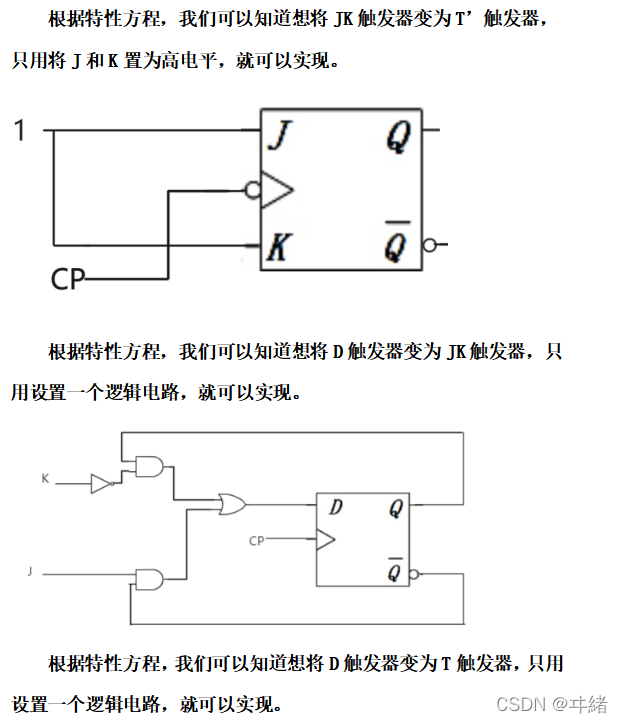

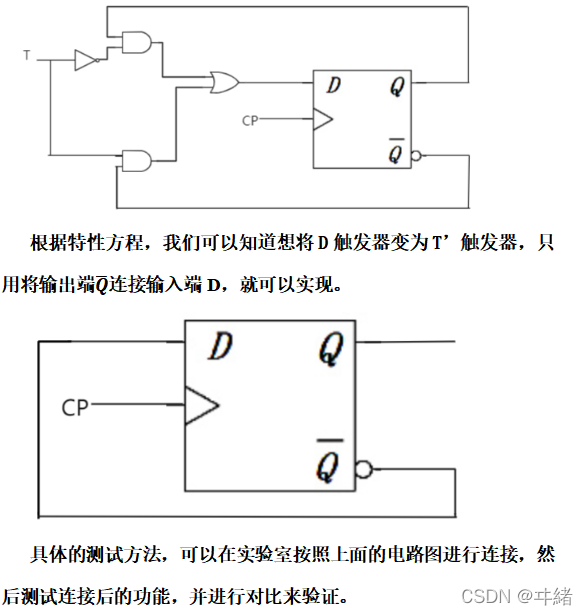

(5)触发器逻辑功能的转换。

-

-

- 思考题

-

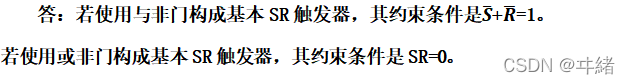

(1)用与非门构成的基本RS触发器的约束条件是什么?如果改用或非门构成的基本RS触发器,约束条件又是什么?

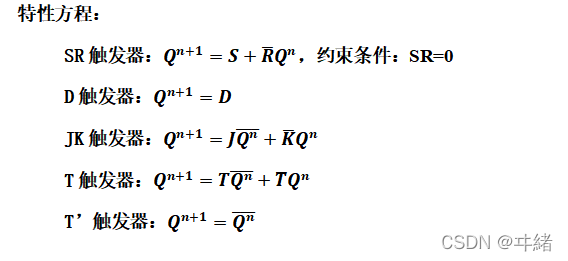

(2)总结各类触发器的特点。

答:D触发器和JK触发器具有较完善的功能,有很多独立的中、小规模集成电路产品。T触发器和SR触发器主要出现于集成电路的内部结构。主从结构的D触发器所需门电路和连线最少,占用面积最小,适用于大规模CMOS集成电路。可将D触发器转换成其它功能触发器。

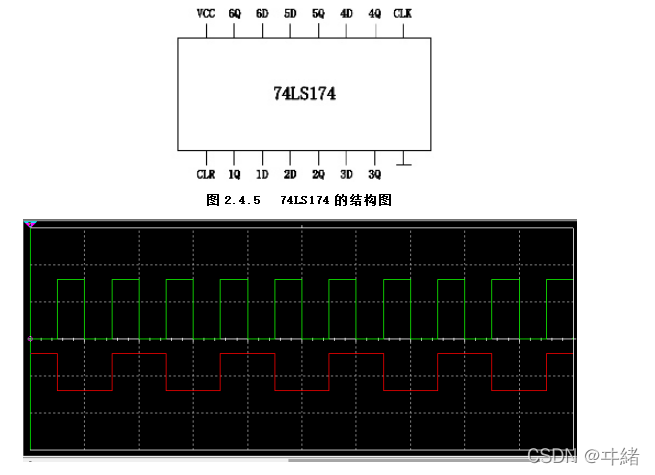

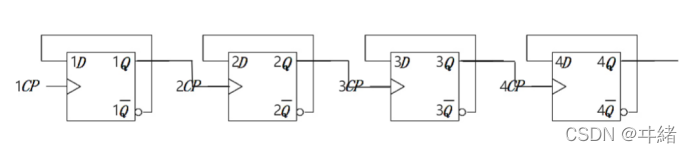

(3)根据本次实验的经验设计一个16分频电路。

答:初始信号加在1CP端,输出端为4Q端。

电路图:

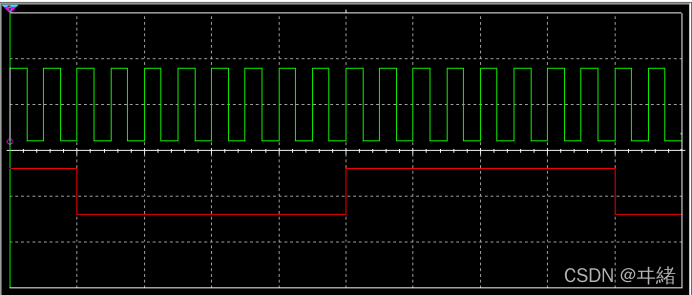

仿真波形:

绿色为输入的1KHz连续脉冲信号的波形,红色的为D触发器的Q输出端的输出信号波形。

(4)总结本次实验的心得。

配套仿真文件:

1993

1993

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?