1、同步概念

频率同步也称为时钟同步。频率同步指两个信号的变化频率相同或保持固定的比例,信号之间保持恒定的相位差。

相位同步是指信号之间的频率和相位都保持一致,即信号之间相位差恒定为零。相位同步的前提是频率同步,所以,相位同步也称为时间同步。

2、LMK04832 SYNC概述

2.1SYNC原理和详图

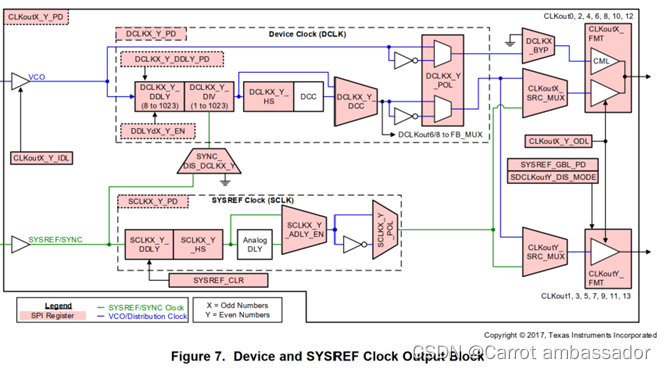

下图显示了包含SYNC电路的时钟输出模块的详细图。SYNC/SYSREF信号能够通过清零DCLKX_Y分频器的计数器来实现DCLKX_Y和SYNC/SYSREF的同步;

注:偶数分频器的实现简单,用计数器在上升沿或者下降沿计数,当计数器的值等于分频系数的一半或等于分频系数时,信号翻转。参见博客--------锁相环(PLL),倍频器、分频器原理_pll分频器原理_不要辣油的博客-CSDN博客

2.2互联和寄存器

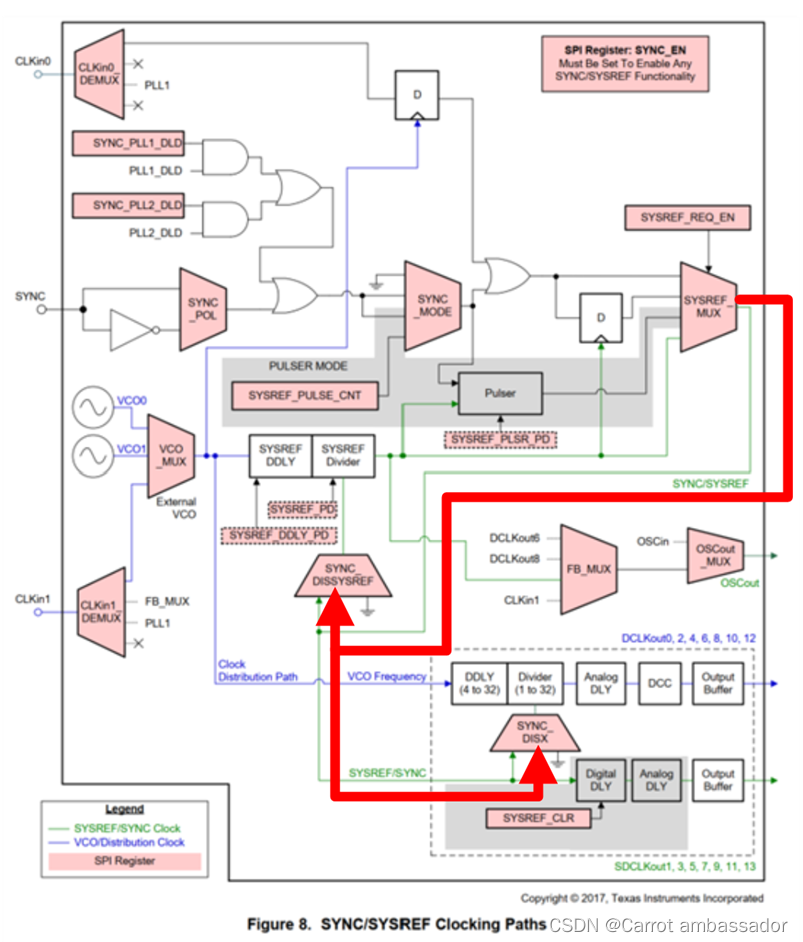

下图说明了互连,并突出显示了用于控制设备以实现SYNc/sYSREF目的的一些重要寄存器。不管是多板同步还是单个device的输出Sysref和Dclk输出同步,最终实现的都是将SYNC或Sysref信号通过下图所示红色路径复位对应分频器(sysref divider和dclk divider),使得对应计数器能在同一时间清零。

2.3前提条件

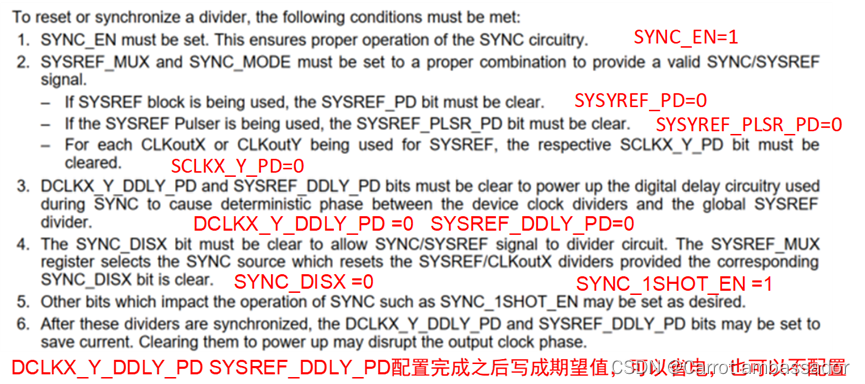

要重置或同步分频器,必须满足以下条件:

2.4常见配置

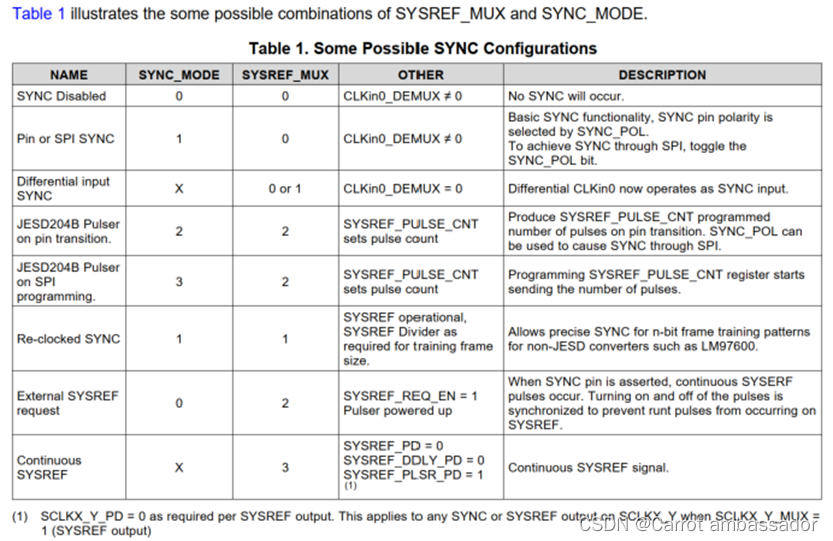

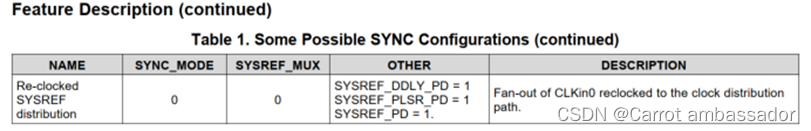

常用配置如下:

- 通过PIN或者SPI寄存器SYNC:SYNC_MODE对应的是1(0x143寄存器),Sysref_mux选择0(0x139寄存器,normal SYNC);CLKin0_DEMUX不能设置成0(0x147寄存器,SYSREF_MUX)。

- 差分输入SYNC: SYNC_MODE随意值都可以(0x143寄存器),Sysref_mux选择0或者1(0x139寄存器,normal SYNC或者re-locked); CLKin0_DEMUX设置成0(0x147寄存器,SYSREF_MUX)。

- 连续SYSREF : SYNC_MODE无所谓(0x143寄存器),Sysref_mux选择3(0x139寄存器,SYSREF Continuous); SYSREF_PD = 0/SYSREF_DDLY_PD = 0/SYSREF_PLSR_PD = 1。

下表中写描述了可能使用的配置。

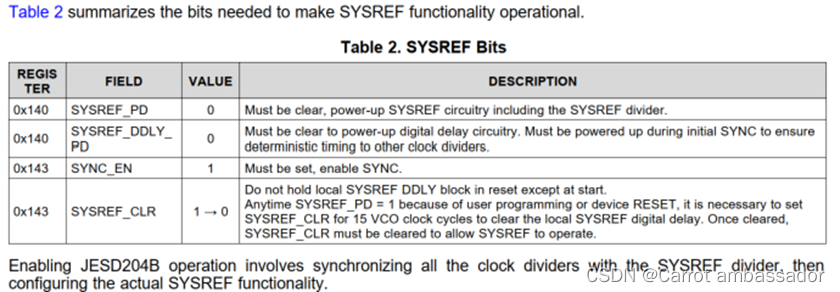

2.5SYSREF配置

需要正常产SYSREF,需要配置以下寄存器:

- 首先PD和DDLY_PD(数字延时)都应该清除,保证SYSREF和DDLY正常运行。

- SYNC_EN必须使能。

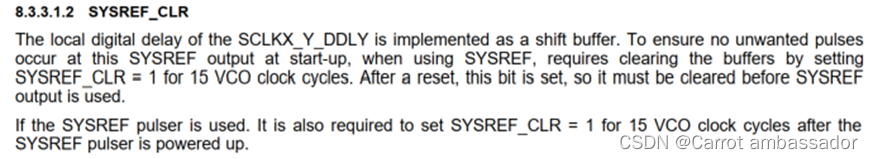

- SYSREF_CLR:对于SYSREF来说,有必要将SYSREF_CLR置位15个VCO时钟周期,用来清除固有的SYSREF 数字延时。一旦延时被清除,必须将SYSREF_CLR复位,来保证SYSREF的正常运行。

3、示例

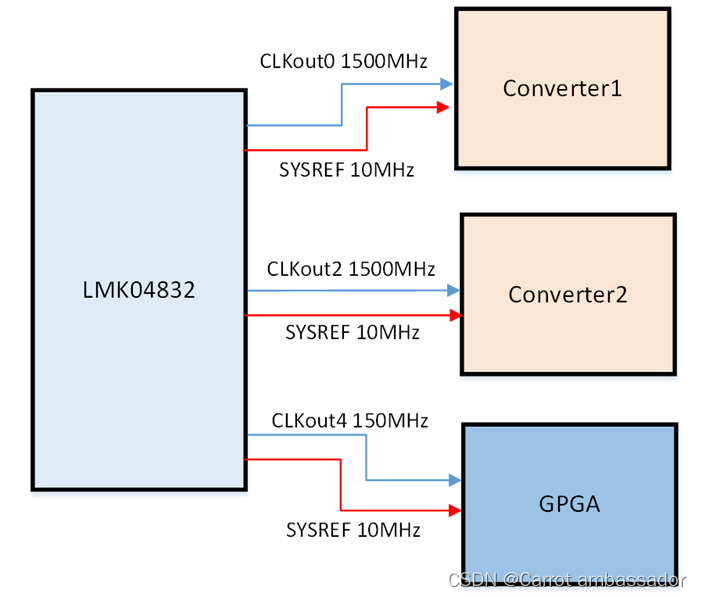

3.1示例概述

LMK04832手册中举了一个例子,VCO频率给3000MHz,CLKout0/2给1500MHz的时钟到Converters,CLKout4给150MHz的时钟到FPGA,用10MHz的SYSREF来同步Converters和FPGA,大概配置如下。

3.2配置步骤

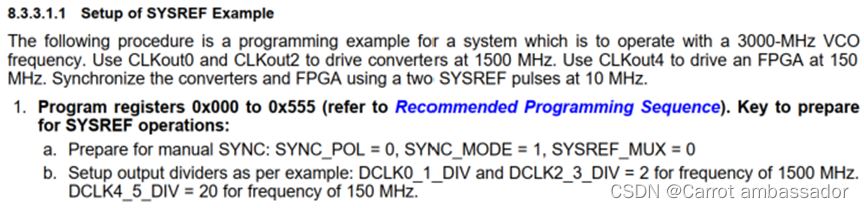

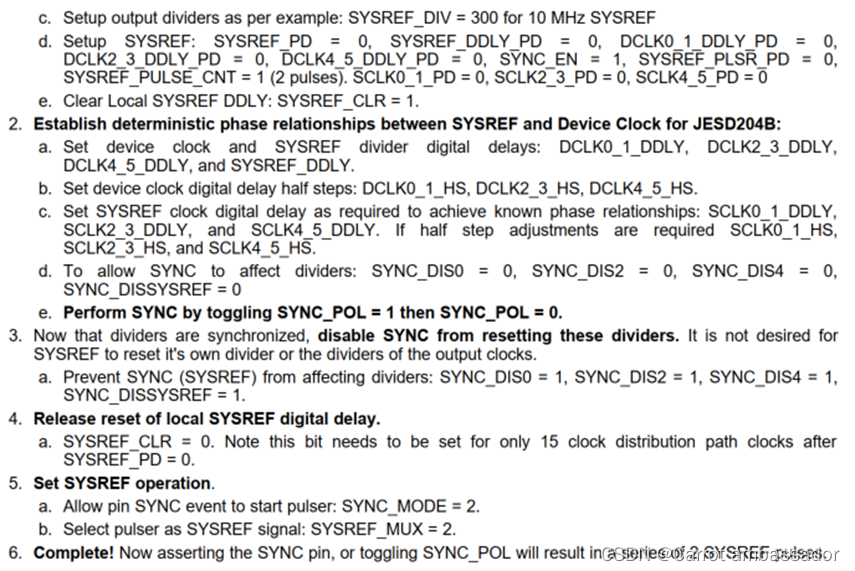

其配置步骤如下:

1、正常配置寄存器0x000-0x555(参考配置顺序),其中需要注意几点,来保证SYSREF的正常运行:

a.准备手动SYNC: SYNC_POL = 0, SYNC_MODE = 1, SYSREF_MUX = 0;

b.设置好正确的分频值;

c.将SYSREF的分频值设置成300;

d.设置SYSREF: SYSREF_PD = 0,

SYSREF_DDLY_PD = 0,

DCLKx_y_DDLY_PD = 0,

SYNC_EN = 1,

SYSREF_PLSR_PD = 0,

SYSREF_PULSE_CNT = 1 (2 pulses).

SCLKx_y_PD = 0

注:前面所有的寄存器,均可以在常规顺序配置中完成。

2、建立SYSREF和J204B DCLK之间的固定相位关系:

a.设置dclk和sysref之间的数字延时:DCLKx_y_DDLY and SYSREF_DDLY;

b.设置DCLK的half steps数字延时:DCLKx_y_HS;

c.设置SYSREF的要求数字延时,以达到固定的相位关系:SCLKx_y_DDLY;

d.为了达到SYNC,需要将SYNC_DISx均置0;注:寄存器0x144 需要在顺序配置中配成0x80;

e.通过翻转SYNC_POL实现SYNC:先SYNC_POL = 1,然后SYNC_POL = 0;注:这一步在完成常规顺序配置之后进行

也即在顺序写完所有寄存器之后按照以下顺序配置: 0x143 0XF1

0x143 0xD1

3、完成上述步骤,已经实现了分频器同步,需要disable SYNC来复位这些分频器。不要求SYSREF来复位它自身的分频器或者输出时钟。

a.关闭SYNC(SYSREF)功能避免影响输出分频器:SYNC_DISx=1;SYNC_DISSYREF=1;

注:完成2中e步骤之后,紧接着写寄存器0x144 0xFF(已经使用1SHOT方式,并通过SPI控制寄存器完成了SYNC,将SYNC触发通道关闭,避免后续的1SHOT关闭之后进入到了held状态)

4、释放SYSREF固有延时清除复位:

a.SYSREF_CLR=0,需要注意的是,在SYSREF_PD之后,只需要将器置为15个时钟分配周期就行;

注:紧接3中配置步骤,写寄存器0x143 0x11(这一步中同时将1SHOT模式关闭。实测如果需要continuous模式的sysref输出,需要将1SHOT关闭,与LMK04821略有差异)。

5、设置SYSREF运行:

a.允许SYNC事件产生作为起始脉冲:SYNC_MODE=2;

注:紧接4中配置步骤,写寄存器0x143 0x12;

b.选择pulser作为SYSREF信号:SYSREF_MUX=2;

注:写寄存器0x139 0x02(如果需要continous sysref输出配置为0x139 0x03)

3.3示例寄存器总结

0x000-0x555按照要求的寄存器顺序正常写入,注意0x144 写值0x80

接上 0x143 0xF1

0x143 0xD1

0x144 0xFF

0x143 0x11

0x143 0x12

0x139 0x03

4、SYSREF_CLR特别说明

SCLKX_Y的Local数字延时作为一个动态的buffer,为了使用SYSREF时不引入非预期的延时,需要通过SYSREF_CLR寄存器先将buffer中的中清零。这个对于pulser和continuous SYSREF的要求一致。

5、多板SYNC

如下图对于多板的应用,正常需要采用红色标注的路径来实现多板同步;也即需要从SYNC/SYSREF PIN或者CLKin0引入同步信号给到系统中的所有时钟芯片来实现同步。

对于寄存器的配置与TI手册中描述的用例基本一致,差异为,0x144寄存器最初配置时需要将SYNC_DISSYSREF也置0,使用PIN给的EVENT实现1SHOT。,需要注意SYNC_DISSYSREF和SYNC_DISx的时间。

本文介绍了频率同步和相位同步的概念,重点讲解了LMK04832时钟输出模块的SYNC功能,包括SYNC电路原理、互联与寄存器控制、配置步骤以及多板同步的应用。文中提供了详细的寄存器配置示例,以确保SYSREF信号的正确同步。

本文介绍了频率同步和相位同步的概念,重点讲解了LMK04832时钟输出模块的SYNC功能,包括SYNC电路原理、互联与寄存器控制、配置步骤以及多板同步的应用。文中提供了详细的寄存器配置示例,以确保SYSREF信号的正确同步。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?