1、前言

在相控阵雷达、分布式天线阵列和医学成像设备中,每个系统中的接收和发送通道数量都在增加,并且需要每个通道之间实现同步,以实现在发送和接收期间提供精准的信号相位控制。大多数需要多个同步信号链路的系统,基本上都要求实现模数转换器(ADC)和数模转换器(DAC)的同步。用于高速ADC和DAC的串行接口JESD204B简化了同步过程,缩减板卡尺寸的同时还减少了器件引脚数量和布线密度。

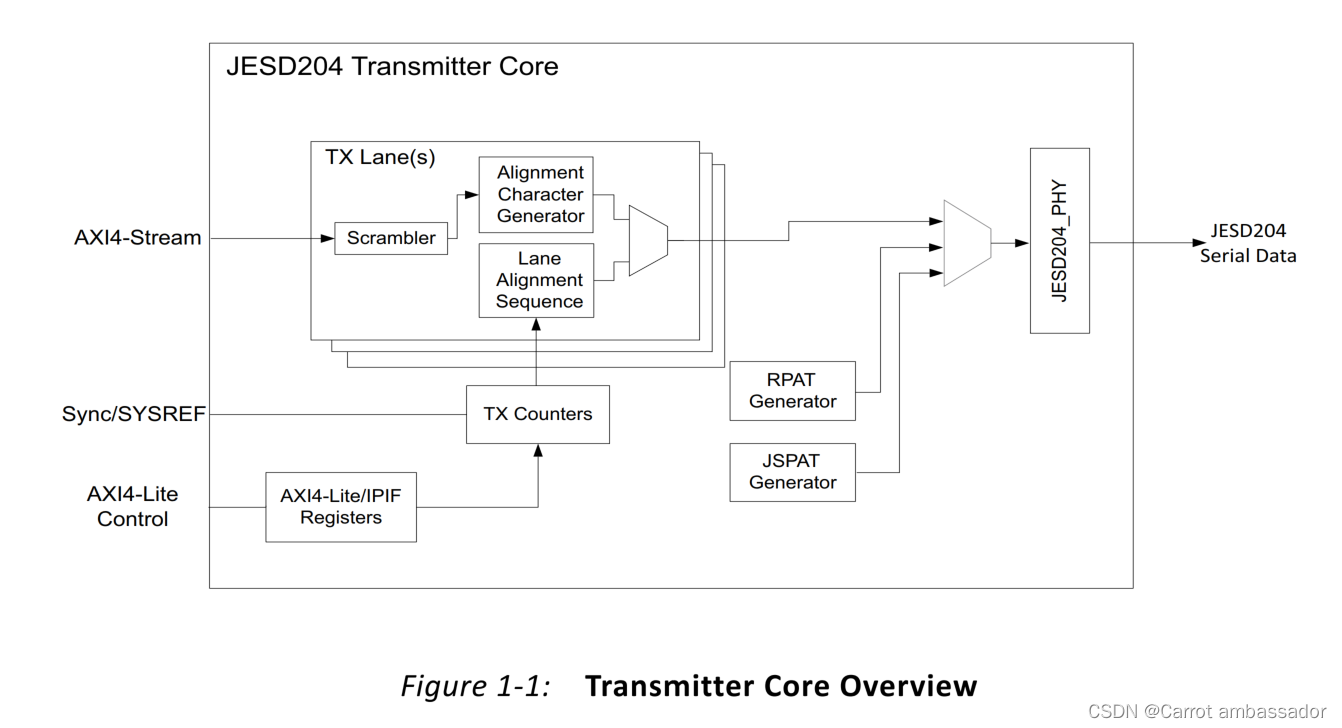

如下图所示为xlinx fpga中jedsd204的发送核内部结构。

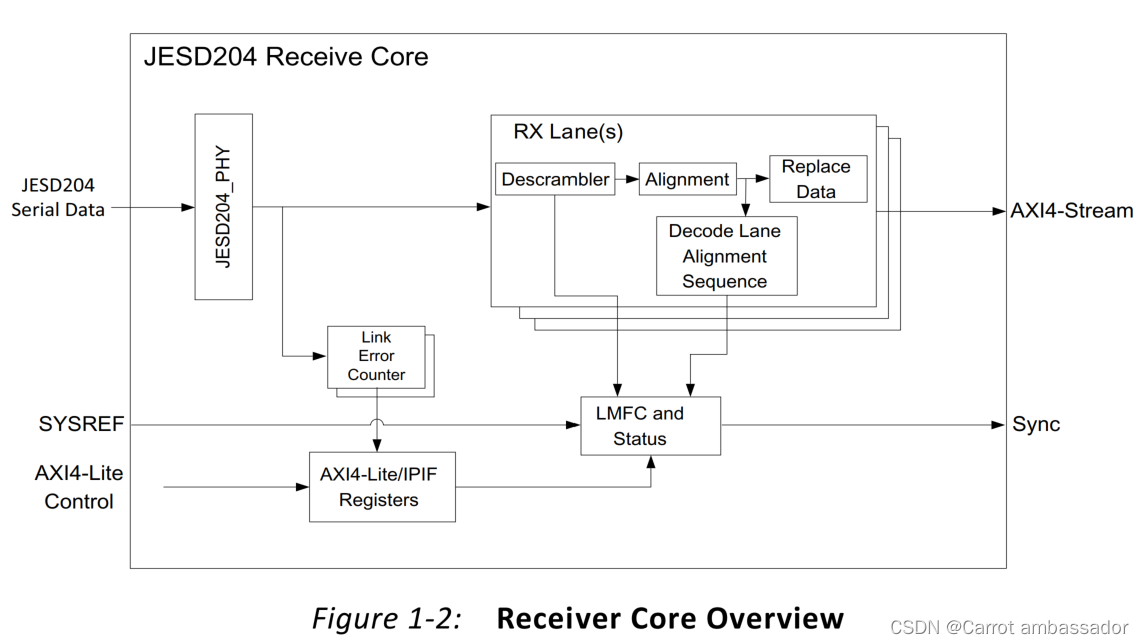

如下图所示为xlinx fpga中jedsd204的接收核内部结构。

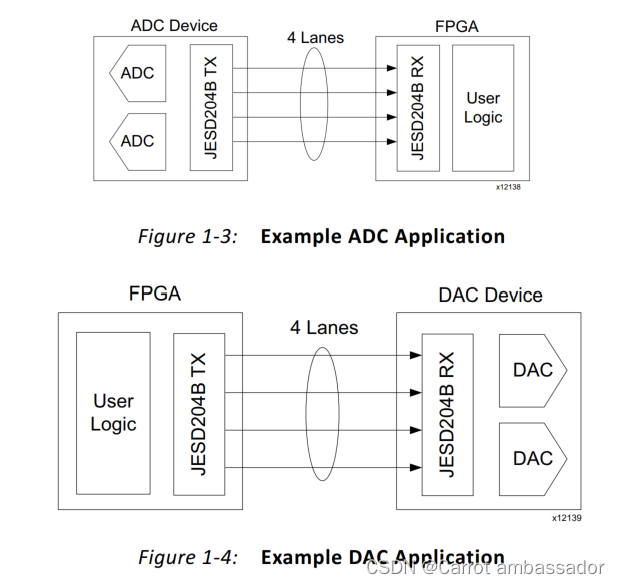

常规条件下的JESD204B应用如下。

2、基本概念介绍

device clock:器件采样时钟;

Sysref:系统同步参考信号。分接收参考(rx_sysref),与发送参考(tx_sysref)。 Rx_sysref与tx_sysref可以来自外部给的同步参考。当然若外部没有输入同步参考,只有一个模块,则这个信号可以自己产生。

Sync:同步信号。分接收同步(rx_sync),与发送同步(tx_sync)。由接收端给发送端,当接收端各lane对齐完成之后,SYNC信号由接收端给到发送端,表明可以接收ILA数据和正常数据了。 Rx_sync:是由jesd204b的接收IP核产生,输出给AD芯片。Tx_sync:是由DA芯片产生,输入给jesd204b的发送模块。

同步:是指JESD204B的每根线的数据同步。即需要调整到每根线同时发送同一多帧中的同一帧的第一个数据。在调节完成前,一直发送的是K码即逗号位。

subclass 1速率高达12.5Gbps,主要通过SYSREF信号实现TX和RX设备之间LMFC的对齐,SYSREF信号必须被分配到所有的转换设备(ADC/DAC)和逻辑设备(FPGA)。通过使用高准确度的device clock和SYSREF信号,可以最小化延时的不确定度。规范建议所有TX和RX设备的SYSREF信号都来自于同一个芯片。

由于SYSREF有多种格式,比如周期的、单脉冲和多个脉冲,并不是所有器件都支持这三种模式。为了使SYSREF在设备正常工作时关闭,subclass 1设备需要满足以下要求。

- RX端的逻辑设备(如接收ADC数据的FPGA)应该具备发送generate SYSREF请求的能力,

- 该请求使时钟发生器为系统中的所有设备产生一个或多个SYSREF 脉冲。任何时间,只要一个link通过SYNC接口发送重同步请求,RX端的逻辑设备都可以发送generate SYSREF请求,该功能是否使能可以由用户决定。

- TX端的逻辑设备(如向DAC发送数据的FPGA)应该具备发送generate SYSREF请求的能力,该请求使时钟发生器为系统中的所有设备产生一个或多个SYSREF 脉冲。任何时间,只要一个link通过SYNC接口发送重同步请求,RX端的逻辑设备都可以发送generate SYSREF请求,该功能是否使能可以由用户决定。

TX和RX设备能够决定是否响应第一个SYSREF之后的其他SYSREF脉冲,并根据该脉冲对本地帧和多帧时钟进行相位对齐。根据规范,TX和RX设备一般会提供以下选项。

- 检测每一个SYSREF脉冲,如果当前LMFC和frame clock需要进行相位调整,则进行相应的相位调整。

- 通过一个输入管脚,或者通过配置接口发送配置命令来控制设备,使其在接收到后续SYSREF时对LMFC和frame clock进行强制相位对齐。

- 通过一个输入管脚,或者通过配置接口发送配置命令来控制设备,使其忽略后续的所有SYSREF。

上述情况只有在设备已经完成初始化并发送了重同步请求,或者link发现错误并发送了重同步请求的情况下才会发生。此外,subclass 1设备应该给出以下时序参数:

- 从采样到SYSREF脉冲的Device clock的上升沿,到LMFC上升沿之间的延迟。

发射时,lanes信号的同步是指:在SYNC信号没有拉高之前会缓存到一个类似寄存器的缓存器中,且当SYNC拉高后根据缓存情况(所有线的多帧的第一个帧开头都缓存下来后),在确定性延时结束后且,在SYNC拉高后的第一个LMFC时一起发送数据(从多帧的一个帧的帧头开始往外发)。

接收时,lanes信号的同步是指:在SYNC信号没有拉高之前会缓存到一个类似寄存器的缓存器中,且当SYNC拉高后根据缓存情况(所有线的多帧的第一个帧开头都缓存下来后),在确定性延时时间满了后在LMFC时接收到第一个多帧的第一个帧的帧头开始算是有效数据。

3、同步要求

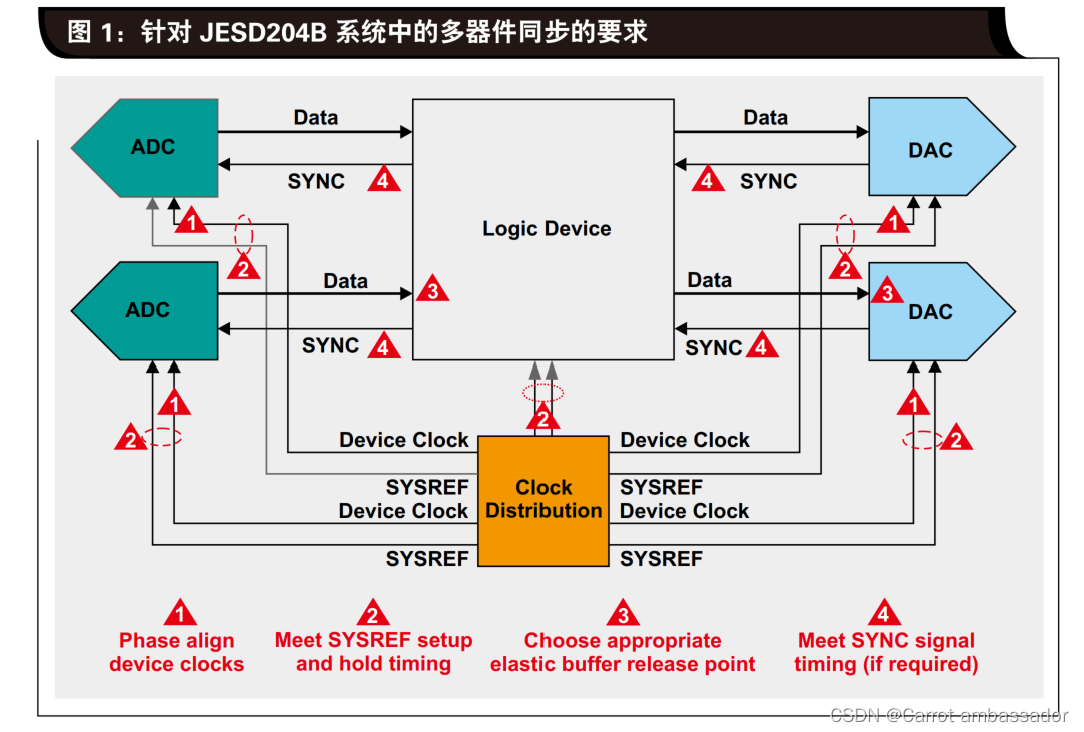

在JESD204B系统中实现数据转换器的同步可以分解位四项基本要求,下图中描绘了这些要求。

1)在每个数据转换器上实现器件的时钟相位对准;

2)在每个数据转换器和逻辑元件上满足SYSREF的建立和保持时间(相对于器件时钟);

3)在JESD204B接收器中选择适当的弹性缓冲器释放点(elsstic buffer release points),以保证确定的延时;

4)满足SYNC信号定时要求(如果需要的话)。

4、器件时钟的相位对齐

在JESD204B系统中,器件时钟被用作转换器的采样时钟(带或者不带分频器),或者用作锁相环(PLL)的基准时钟(PLL负责产生采样时钟)。因此,每个转换器上的器件时钟相位对齐对于保持每个转换器中的采样实例对准是极为重要的(保证采样时刻一致)。器件时钟的对齐取决于时钟分配路径上的传播延时控制情况,包括整个温度变化范围内对齐保持的状态的好坏。

5、SYSREF要求

对于实现可以重复的系统延时和同步而言,SYSREF信号是最重要的。针对SYSREF信号的两个要求是:满足相对于器件时钟的建立及保持(setup-and-hold)时间,并且以一个适当的频率运行。值得注意的是SYSREF可以以单个脉冲的方式实现,从而可以取消频率要求;但是这需要对SYSREF信号进行DC耦合,很多器件由于SYSREF的电平要求,对共模电压有要求,不能使用DC耦合。

对SYSREF最具挑战的是建立和保持定时。针对较低速度的流水线型ADC和基带DAC(<1GSPS)的应用来说,建立及保持定时要求没那么困难,然而对于速度较快的器件(比如千兆采样ADC和RF采样DAC)而言,高速器件时钟速率减小了用于SYSREF的建立及保持窗口,而且很有可能需要进行动态延时调节来实现在所有条件下维持正确的定时。

JESD204B在数据转换器的计时方法上提供了灵活性。例如:有些器件包含了一个集成型的PLL,因而允许使用一个频率较低的device clock,经过PLL倍频创建采样时钟,device clock仍然捕捉SYSREF,但是相比较而言较低的器件时钟频率,极大的降低了建立和保持的要求。此外,器件可能还包含了辅助满足定时要求或者放宽要求的特性。如果不能满足正确的定时,则很可能需要采用外部校准程序来实现同步。

6、SYSREF频率选择

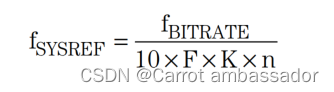

对于连续或者间隙周期的SYSREF频率有一个限制(但是这不适用于单脉冲的方案)。主要要求是SYSREF信号必须以一个等于本地多帧时钟(LMFC)频率或者以一个本地多帧频率整数分频频率来运行。公式如下:

上述公式中fBITRATE为通道速率,F为每帧数据的字节数,K为每个多帧的帧数,10是因为JESD204B是8B/10B编码,n是随意整数。

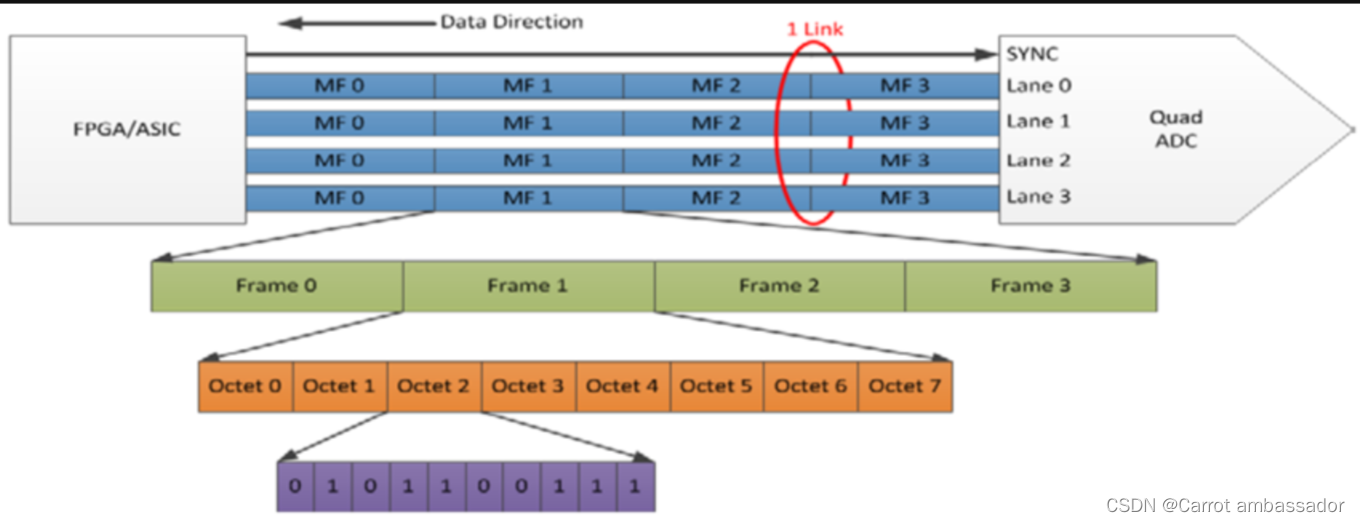

如下图所示,JESD204B为4X,假设每lane上的数据传输速率为10Gbps,如图每个MF(多帧)中有4帧(Frame),也即K=4;每帧中有8个字节(Octec),也即F=8;每个字节由于经过了8B/10B编码总共有10bit的数据。按照公式可以算出多帧频率为10Gbps/4/8/10=31.25M,那么SYSREF可以是任意整数,所以fsysref=31.25/n(MHz)。

通常可以通过调整SYSREF频率来调整K值,基本上除了JESD204B标准中规定的17<FxK<1024这条规定之外,每个器件对于K值基本都有自身的限制。

假如器件采用内部时钟分频器或者SYSREF来实现其他数字功能的同步,那么对SYSREF频率还会有其他要求。例如:某个器件采用一个是内部时钟分频器来生成采样时钟,则需要保证内部时钟分频器的同步,来保证采样时钟的相位一致(分频器实际都是计数器,同步实际就是保证每个分频器在复位之后同时释放)。这个要求就给SYSREF频率设定了一个额外的限制,因为它必须是LMFC频率和最低内部生成频率的一个公约数。

7、弹性缓冲器释放点

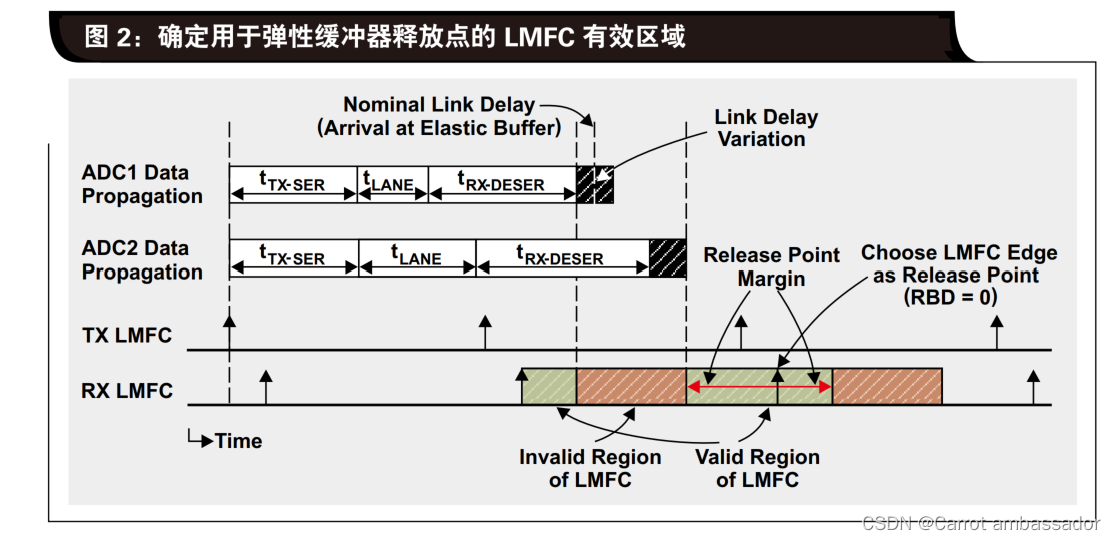

针对于同步的第三项要求是在JESD204B接收器中选择一个正确的 elastic buffer的释放点,以实现确定性的延迟。 elastic buffer是实现确定性延时的关键部件,它能够吸收数据在204B链路中的传播延时。正确的释放点对于传输延时可以提供充足的裕量,错误的释放点则会产生一个多帧周期的延时变化。

选择正确的释放点,需要了解数据在 elastic buffer上的平均到达时间(相对于多帧周期的边沿)以及所有器件的总预计延时变化。利用这个信息可以确定多帧周期内的无效释放点区域,从而保证涉及人员能在所有lane上数据到达之后再释放。如下图所示,ADC2的延时较长。其中ADC1和ADC2通道中黑色方块表示多帧中数据到达的时间;TX LFMC对应的箭头表示多帧发送的时间点;RX LFMC中箭头表示elastic buffer释放点,绿色部分表示有效的释放点,红色表示的是无效的释放点。

8、SYNC信号

由于转换器的采样速率增加了,因此对于保持低接口速率的期望也提高了,这个通常是通过DAC中的DUC(数字上变频)和ADC中的DDC(数字下变频)实现的。DDC和DUC通常是使用转换器中的NCO来实现的,因此在使用该功能时,也必须保证所有器件中的NCO同步来保证系统整体同步。在DAC中,最常用的办法就是通过LFMC的上升沿和elastic buffer的释放点来同步NCO。在ADC中,则是采用SYNC信号被解除有效状态之后出现的第一个LMFC边沿来对实现NCO的同步。

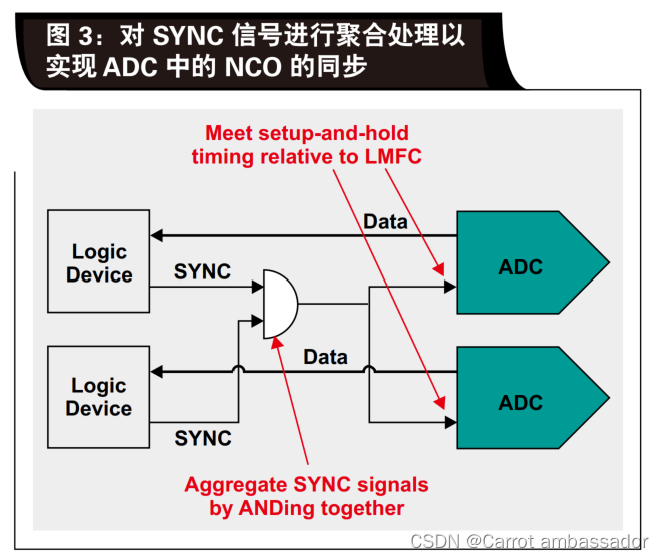

为了保证使用了NCO功能的多个ADC和DAC同步,对于SYNC信号有两个要求。第一个是SYNC信号必须位于相同多帧周期边沿上的所有接收器来释放SYNC;第二个是要在同一个多帧周期的发送器上接收。

满足第一个要求方法比较简单,只要将所有接收器的SYNC信号进行“与”操作,然后把该信号分配给每个发送器就可以,如下图所示。这就对SYNC信号设定了一个要求,就是必须满足相对于发送器件中的多帧周期边沿建立保持时间。

如果ADC和DAC中没有用到DDC和DUC则对SYNC信号没有要求,每个器件可以在各自独立的时间启动,并且仍然能够实现同步。

对于SYNC信号实现ADC中的NCO同步,时钟设计最困难的是满足SYSREF和device clock的时钟定时关系,为了解决这个问题,提供两个典型的JESD204B时钟设计方案:

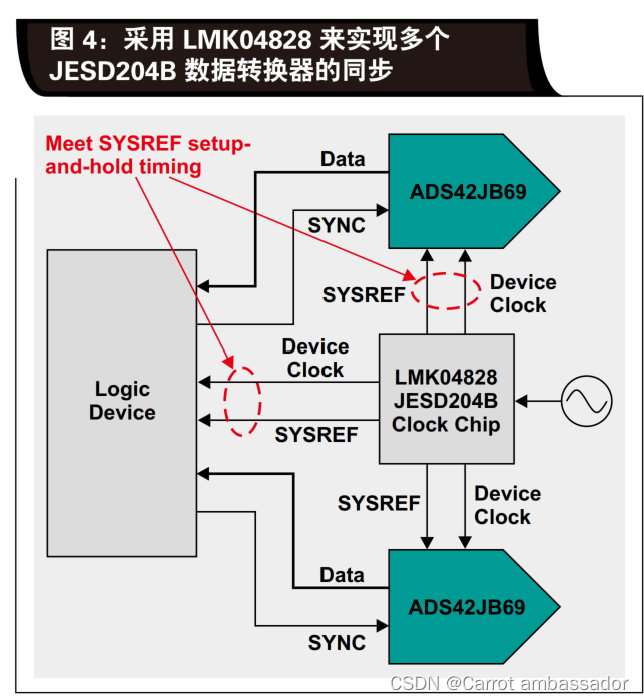

方案一:对于保证正确的SYSREF建立和保持时间而言,最简单的方法就是使用同一时钟芯片给device clock和SYSREF。由于这类器件的具有匹配输出,能保证在所有条件下device clock和SYSREF的相位对齐。如下图为TI的LMK04828,有7对时钟输出。 该方案可以应用于地采样速率转换器或者内部具有PLL的高采样率转换器。

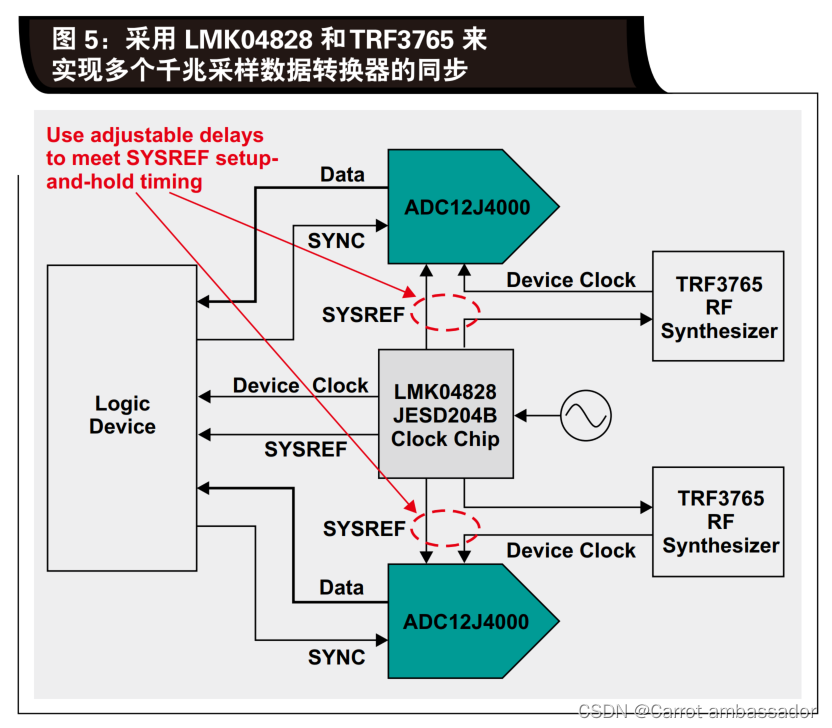

方案二:当一个高采样率器件不具备内部PLL或者PLL被旁路来保证性能时。以ADC12J4000为例,其采样率高达4GSPS,设计时需要一个4GHz的时钟,但是普通的JESD204B时钟不满足该要求,因此提供以下设计方案,在LMK04828的device clock上增加了TRF3765RF倍频实现4GHz的时钟(倍频不会造成不同步,分频才会)。设计时可利用时钟器件中的抖动清除器和可编程延时调整满足建立和保持时间。

--内容来源TI和《pg066-jesd204》

8万+

8万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?