文章目录

- Analog-to-Digital Converter (ADC)

- 用于内部供应监控的ANAMUX

- BCTU接口

- 硬件触发

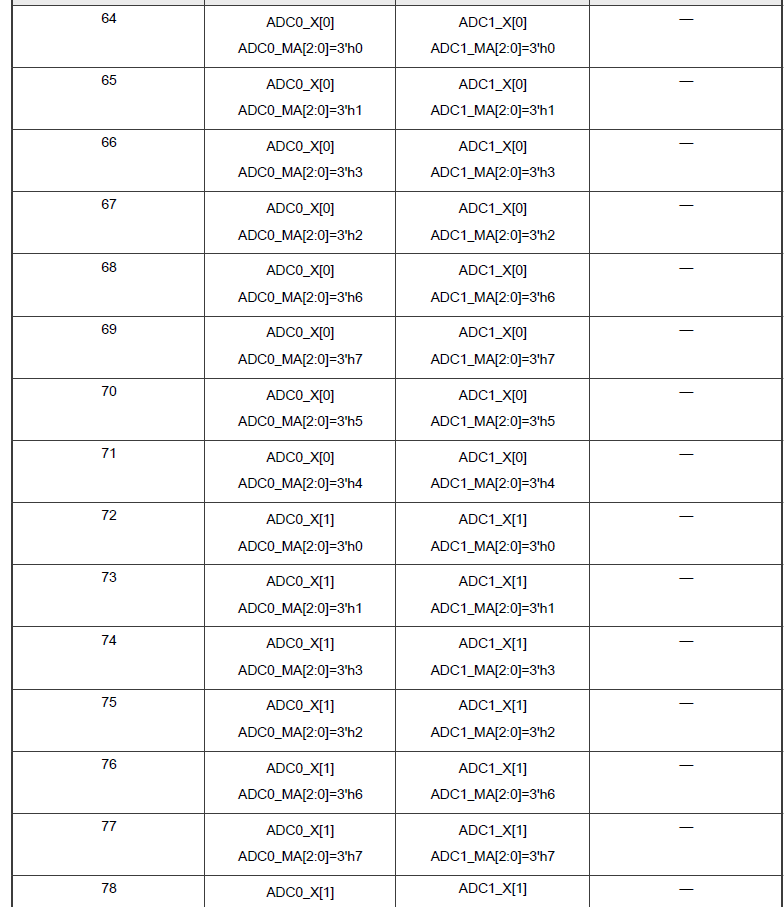

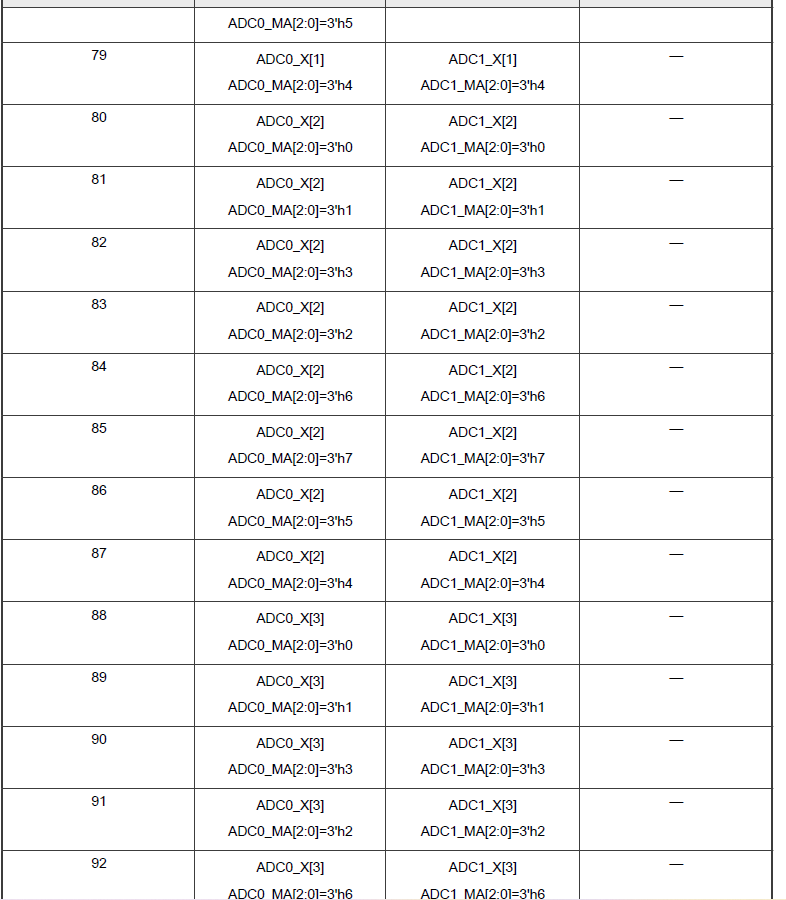

- ADC多路模式通道

- 功能框图

- 特点

- 功能描述

- Clock frequency

- Memory map and register definition

- Main Configuration (MCR)

- Main Status (MSR)

- Interrupt Status (ISR)

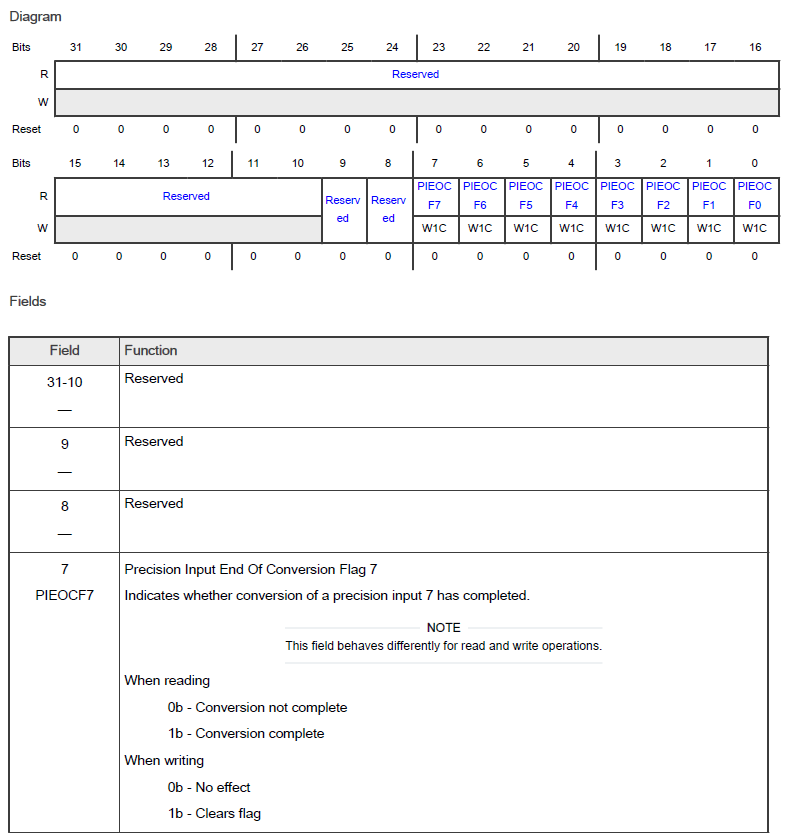

- Channel End Of Conversion Flag For Precision Inputs (CEOCFR0)

- Channel End Of Conversion Flag For Standard Inputs(CEOCFR1)

- Channel End Of Conversion Flag For External Inputs (CEOCFR2)

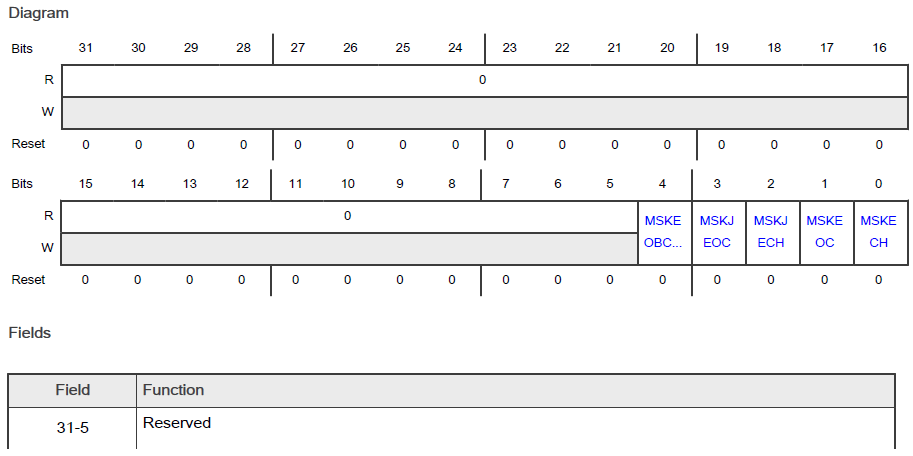

- Interrupt Mask (IMR)

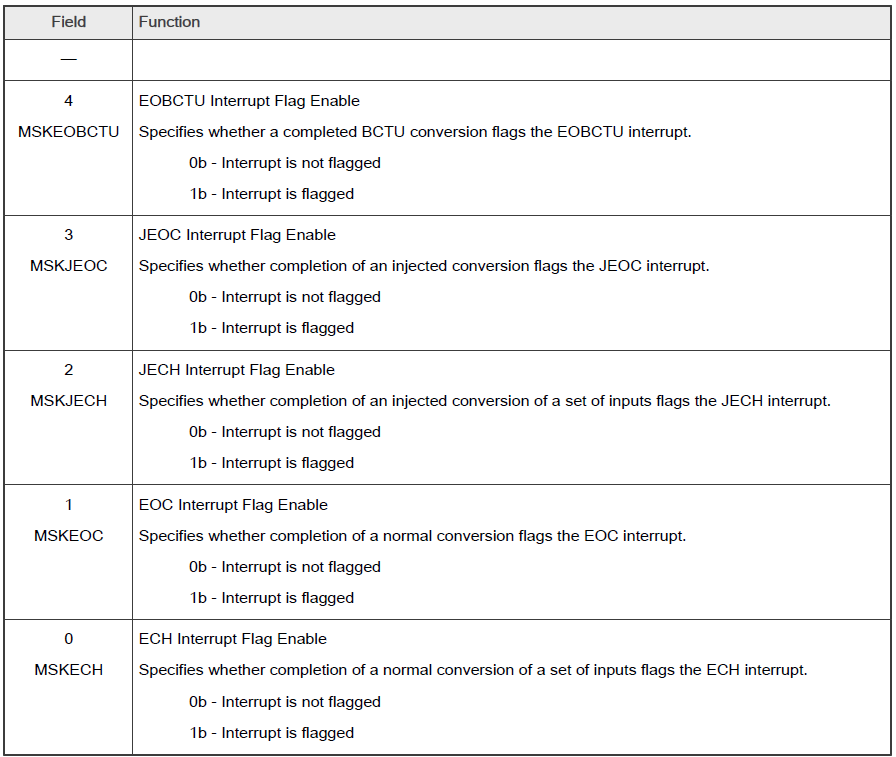

- Analog Watchdog Threshold Interrupt Status (WTISR)

- Analog Watchdog Threshold Interrupt Enable (WTIMR)

- Direct Memory Access Configuration (DMAE)

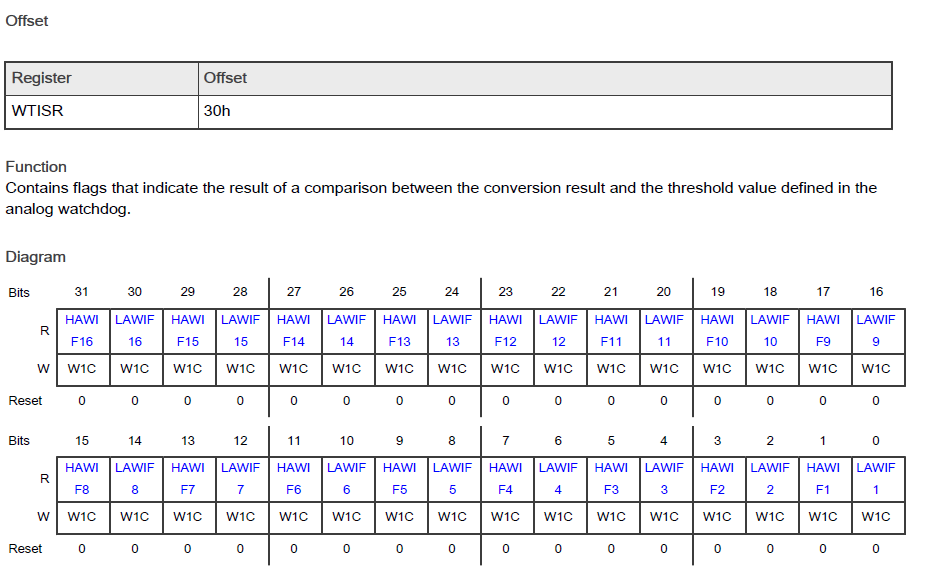

- DMA Request Enable For Precision Inputs (DMAR0)

- Analog Watchdog Threshold Values (THRHLR0 - THRHLR3)

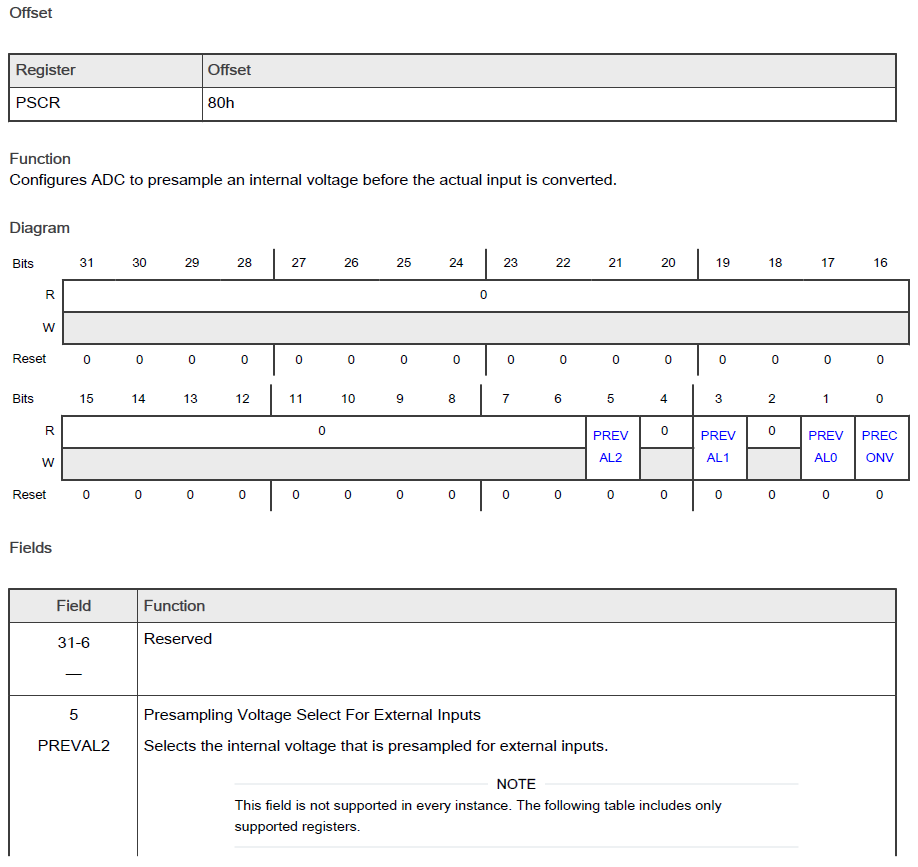

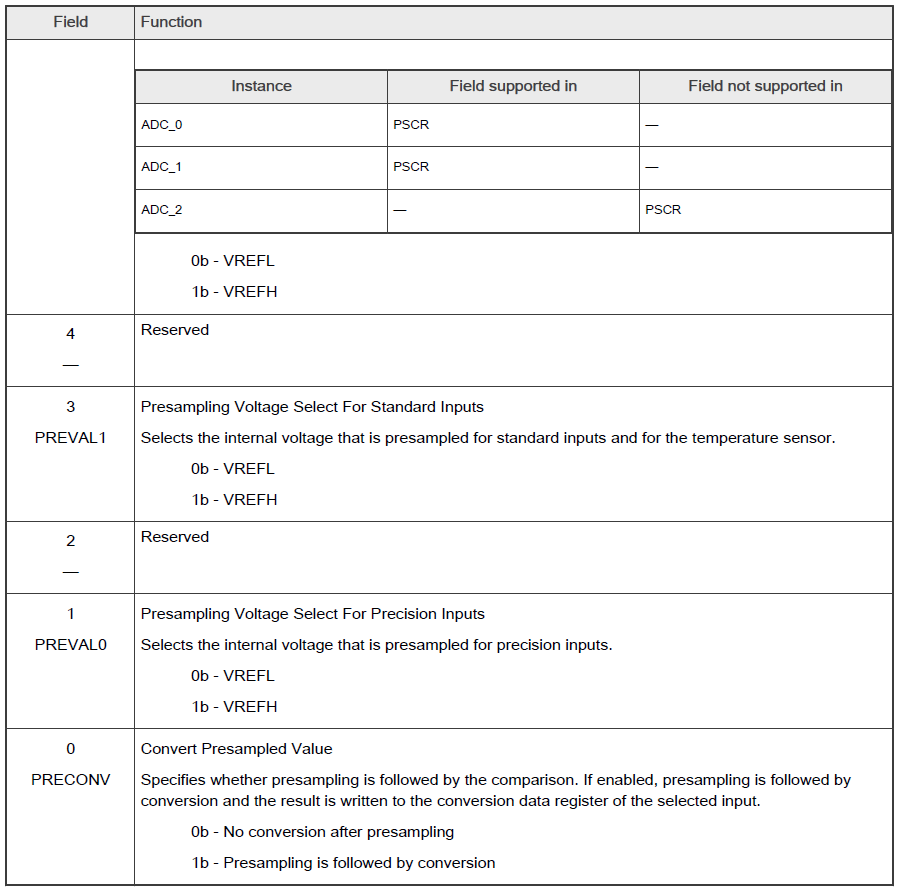

- Presampling Control (PSCR)

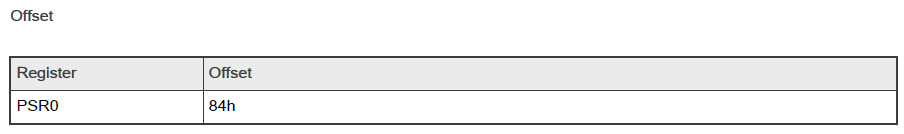

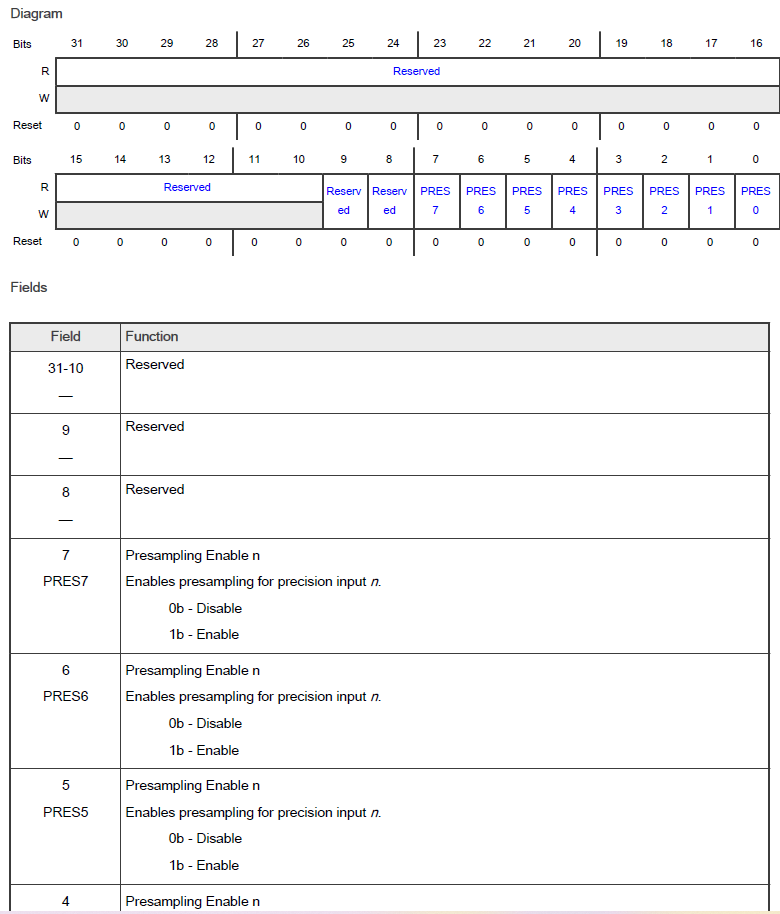

- Presampling Enable For Precision Inputs (PSR0)

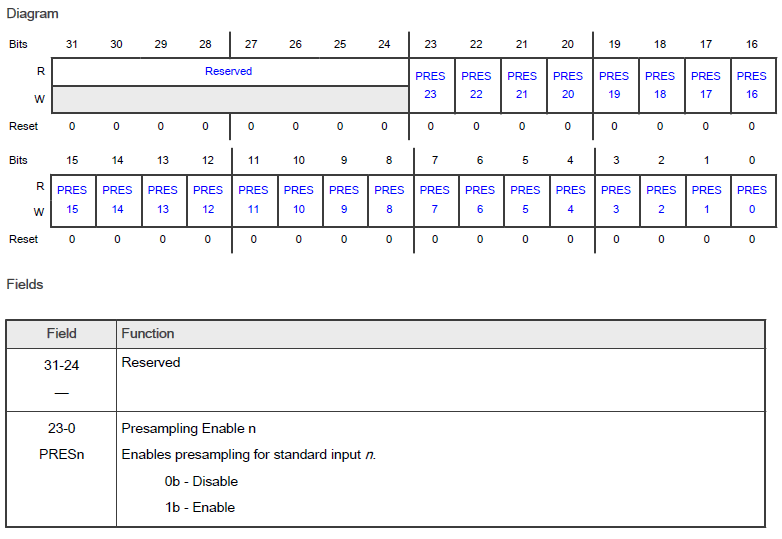

- Presampling Enable For Standard Inputs (PSR1)

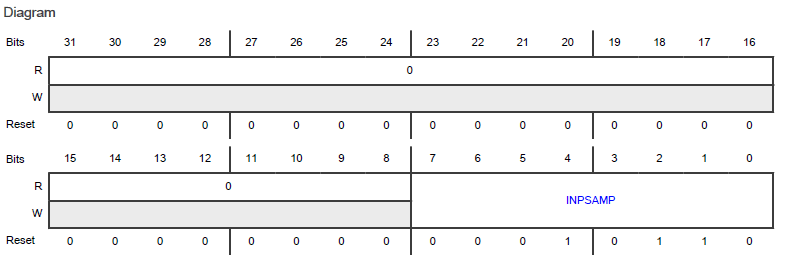

- Conversion Timing For Precision Inputs (CTR0)

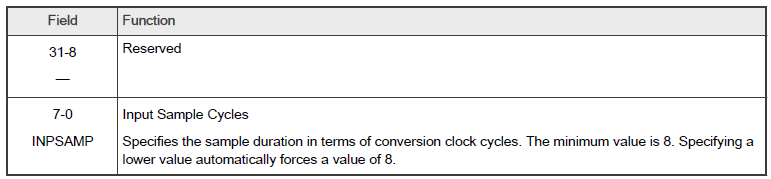

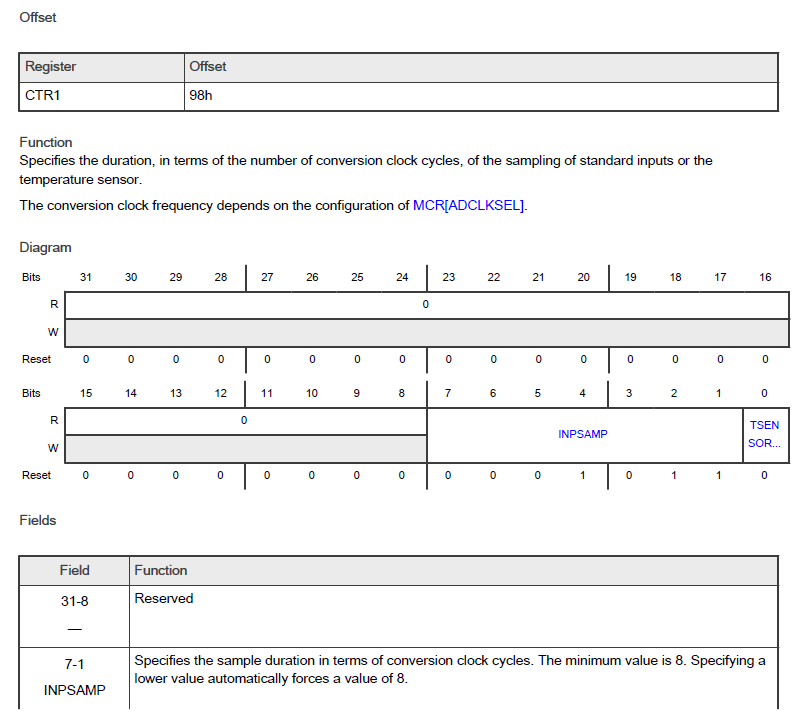

- Conversion Timing For Standard Inputs (CTR1)

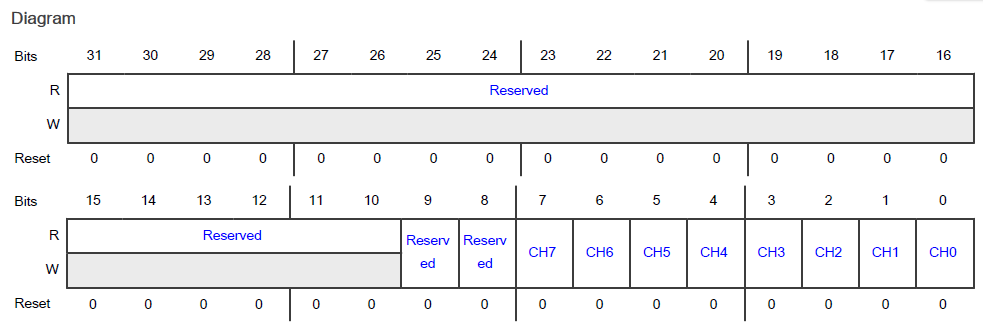

- Normal Conversion Enable For Precision Inputs (NCMR0)

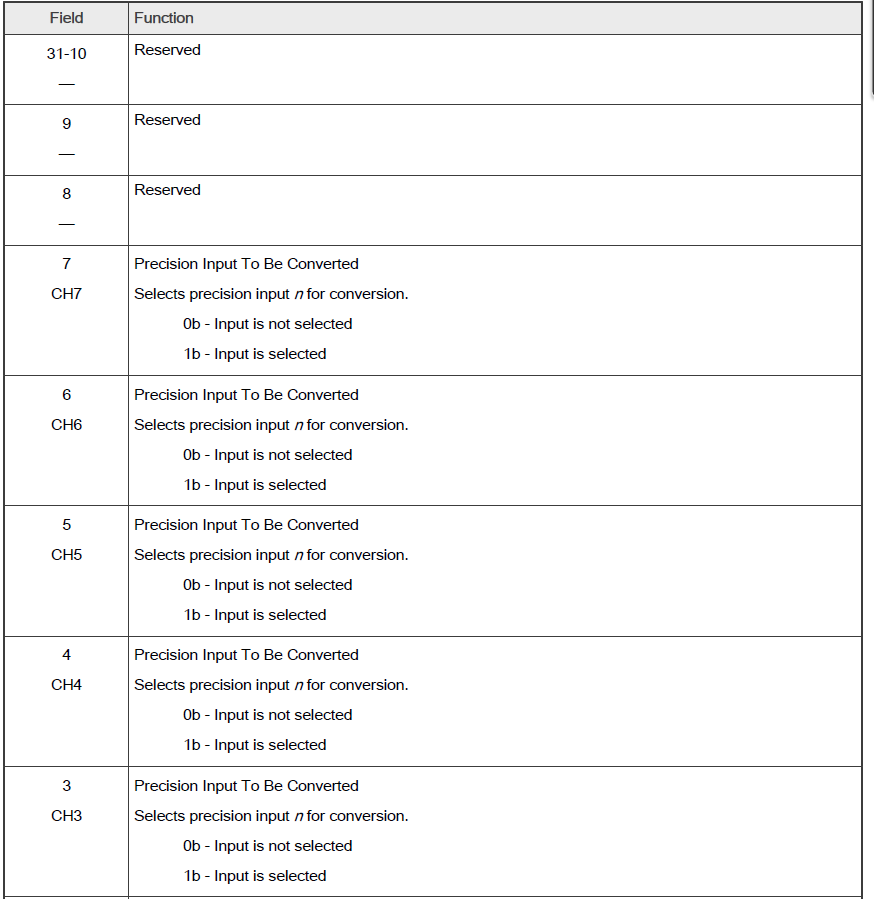

- Injected Conversion Enable For Precision Inputs (JCMR0)

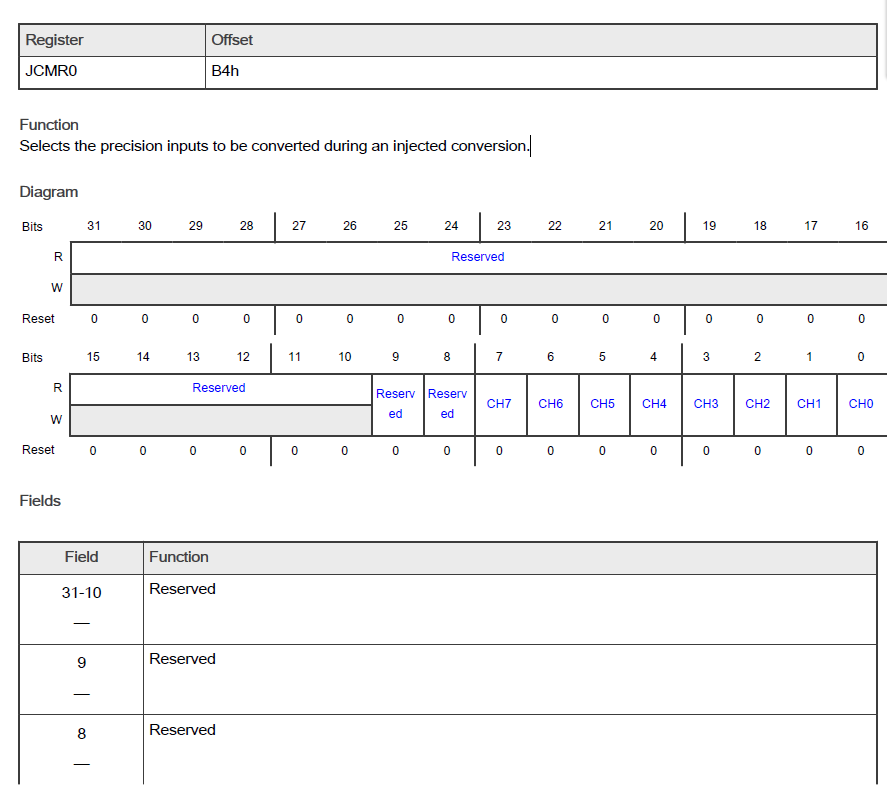

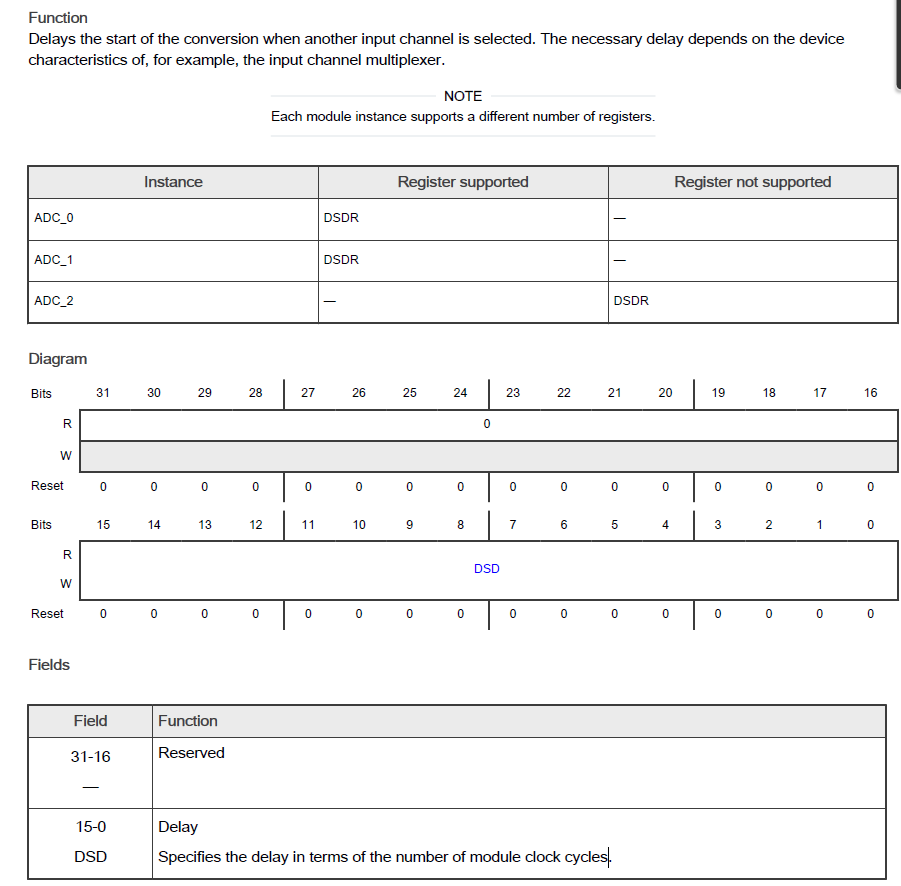

- Delay Start Of Data Conversion (DSDR)

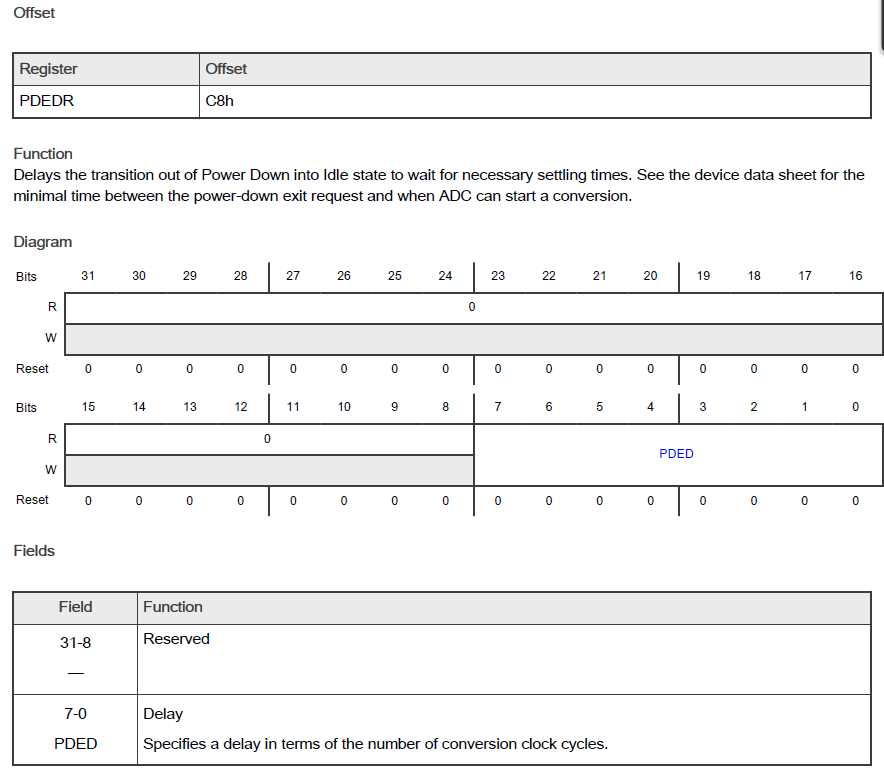

- Power Down Exit Delay (PDEDR)

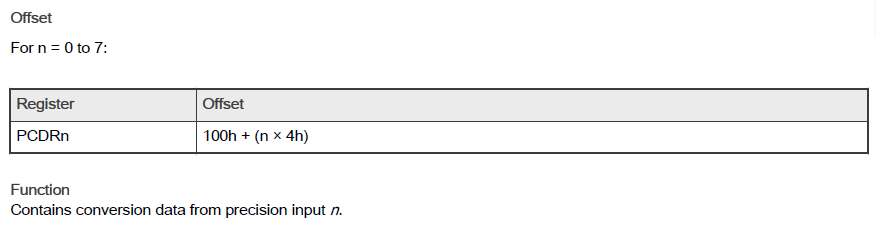

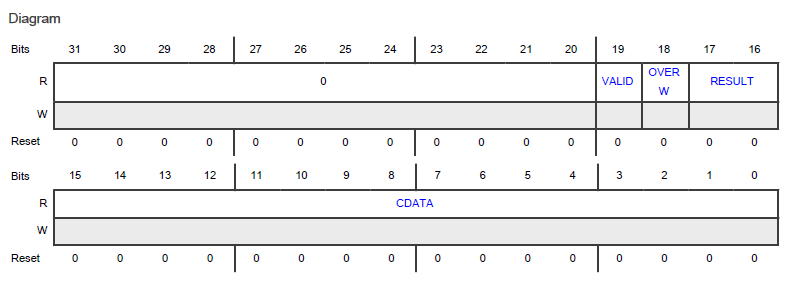

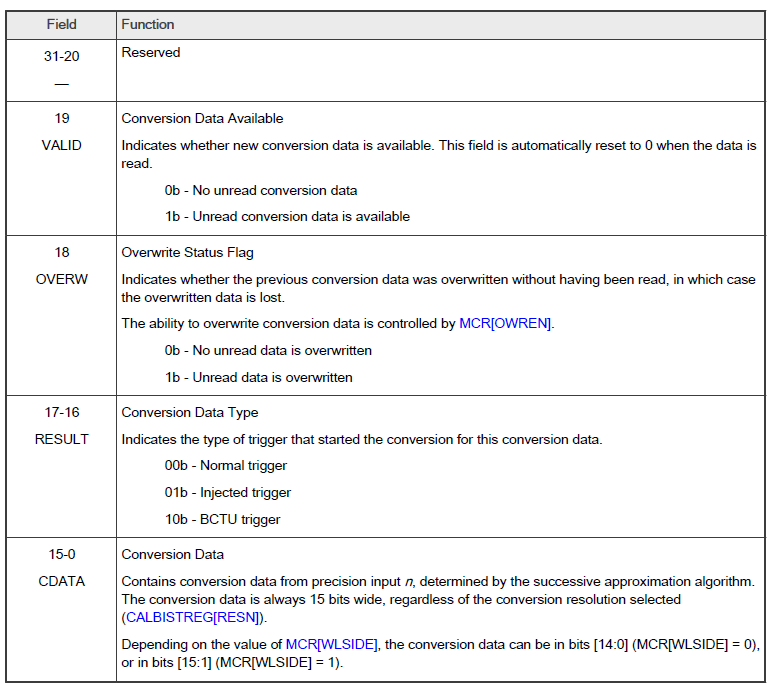

- Precision Input n Conversion Data (PCDR0 - PCDR7)

- Standard Input n Conversion Data (ICDR0 - ICDR23)

- External Input n Conversion Data (ECDR0 - ECDR31)

- Channel Analog Watchdog Select For Precision Inputs (CWSELRPI0)

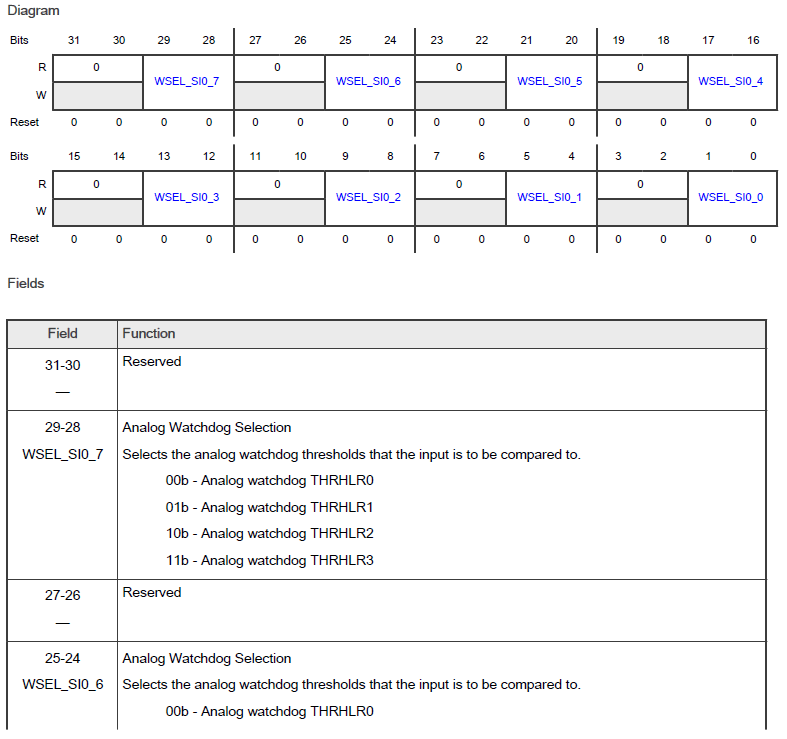

- Channel Analog Watchdog Select For Standard Inputs (CWSELRSI0)

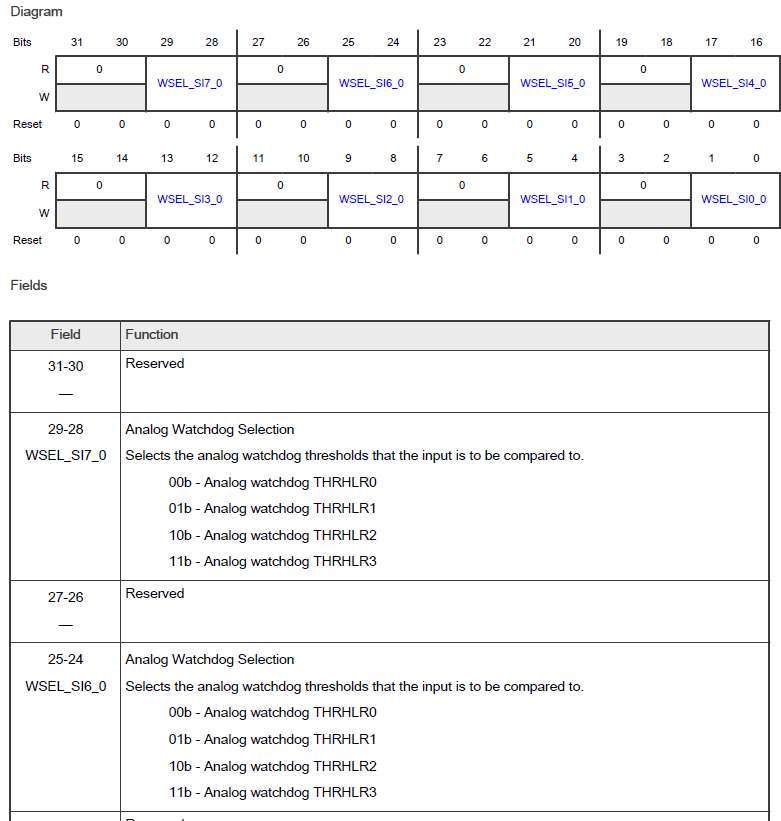

- Channel Analog Watchdog Select For Standard Inputs (CWSELRSI1)

- Channel Analog Watchdog Select For Standard Inputs (CWSELRSI2)

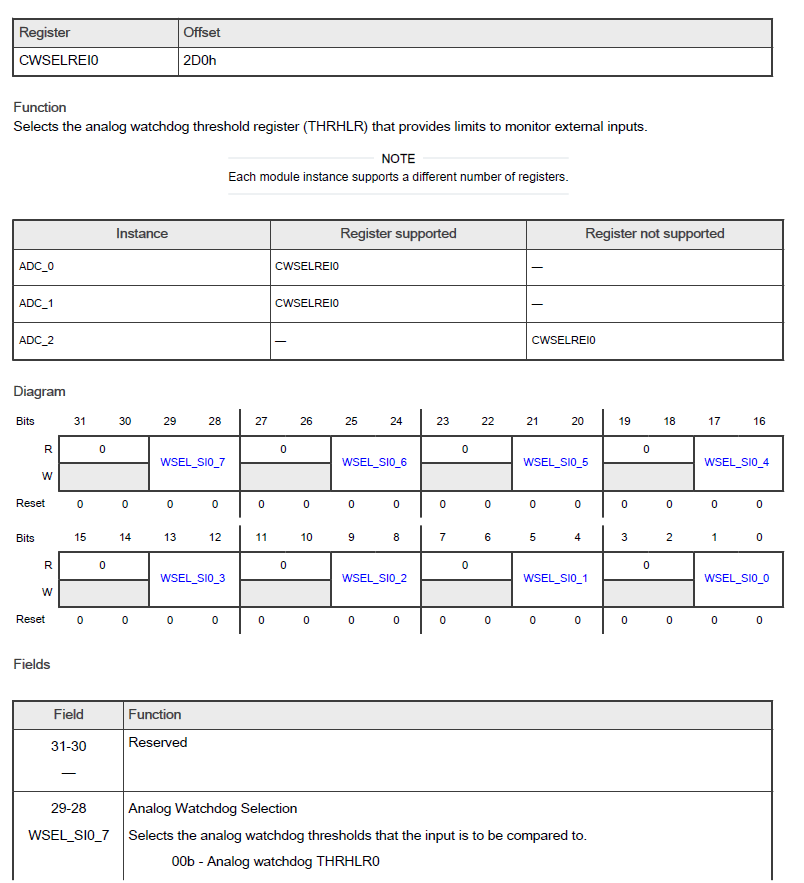

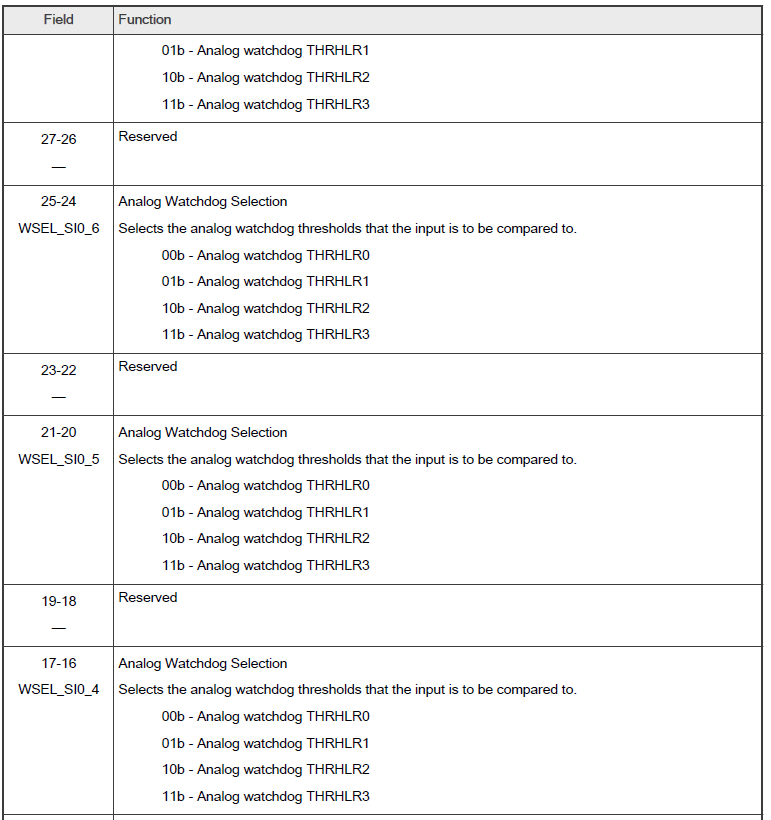

- Channel Analog Watchdog Select For External inputs (CWSELREI0)

- Channel Analog Watchdog Select For External inputs (CWSELREI1)

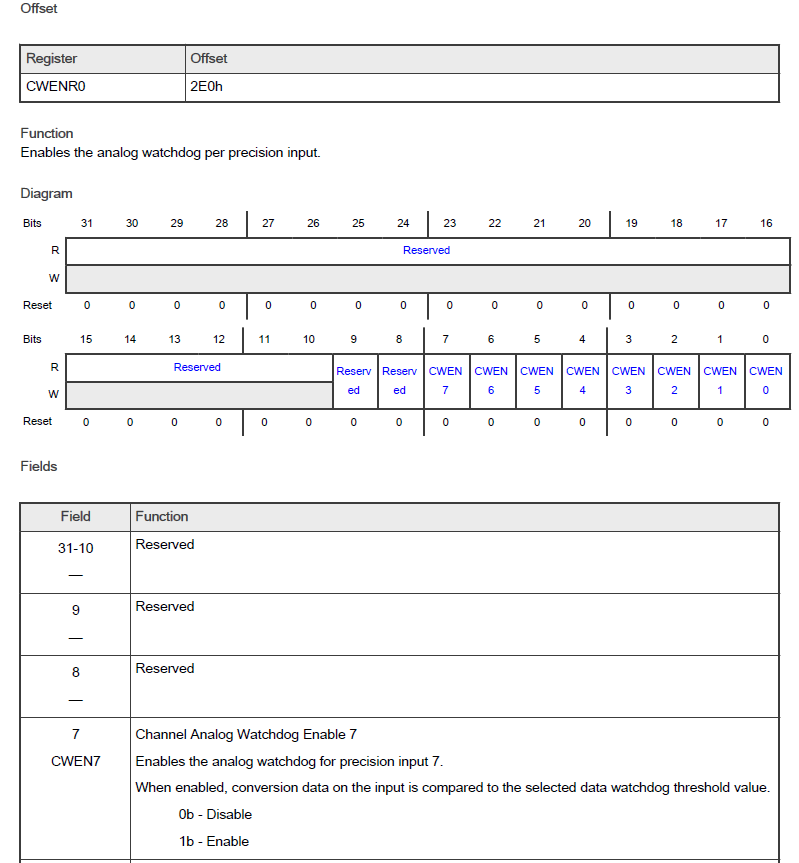

- Channel Watchdog Enable For Precision Inputs (CWENR0)

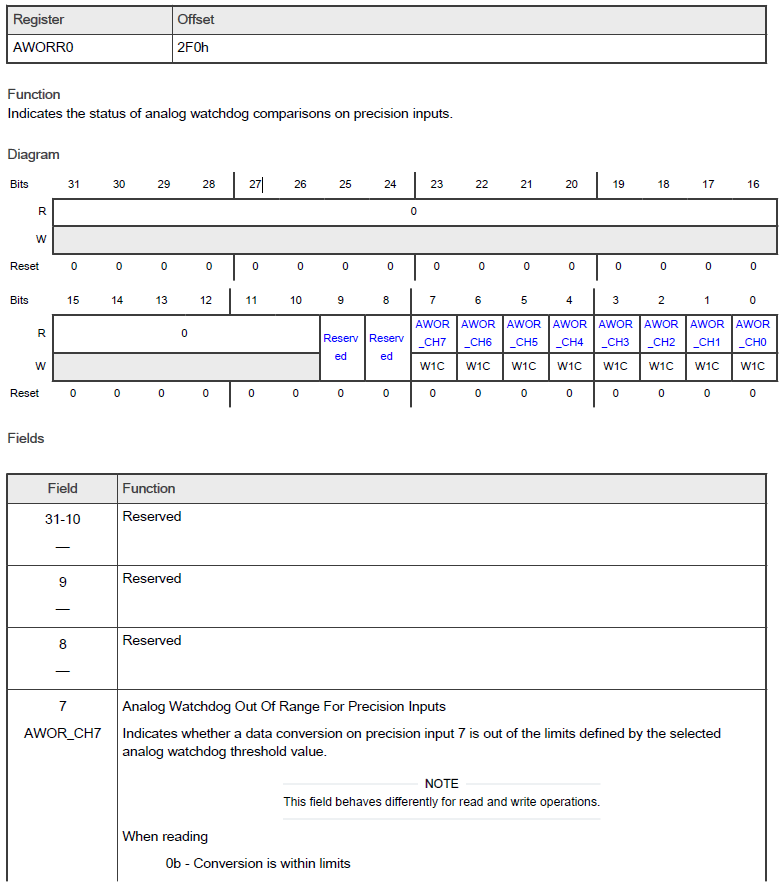

- Analog Watchdog Out Of Range For Precision Inputs (AWORR0)

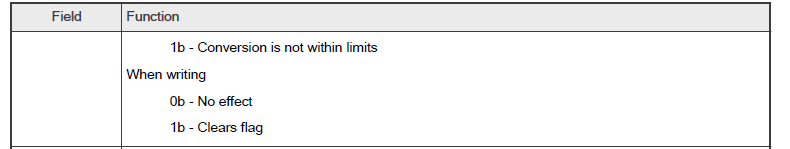

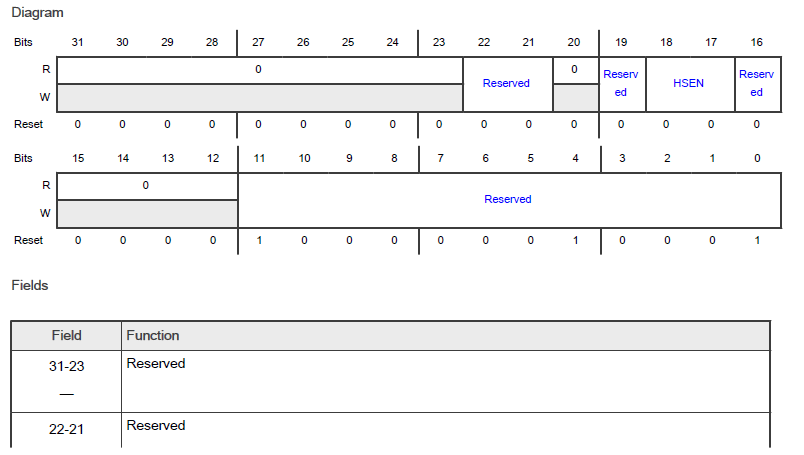

- Analog Miscellaneous In/Out register (AMSIO)

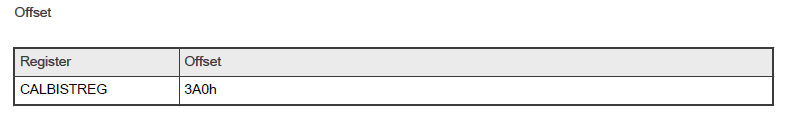

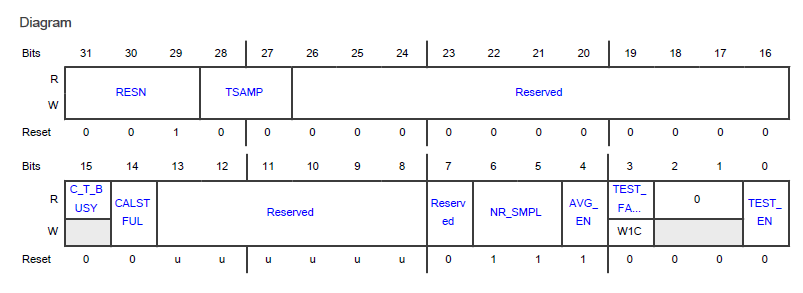

- Control And Calibration Status (CALBISTREG)

- Offset And Gain User (OFSGNUSR)

- Calibration Value 2 (CAL2)

Analog-to-Digital Converter (ADC)

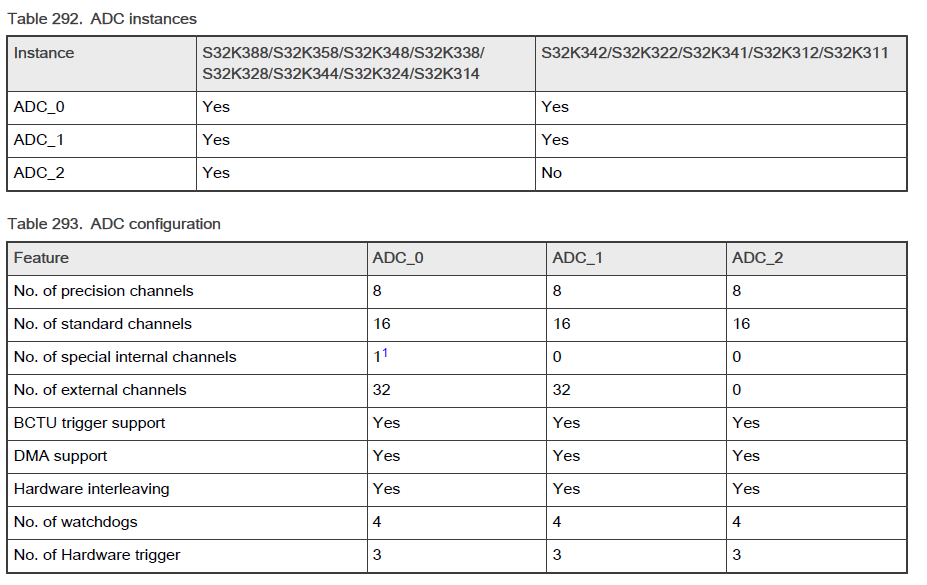

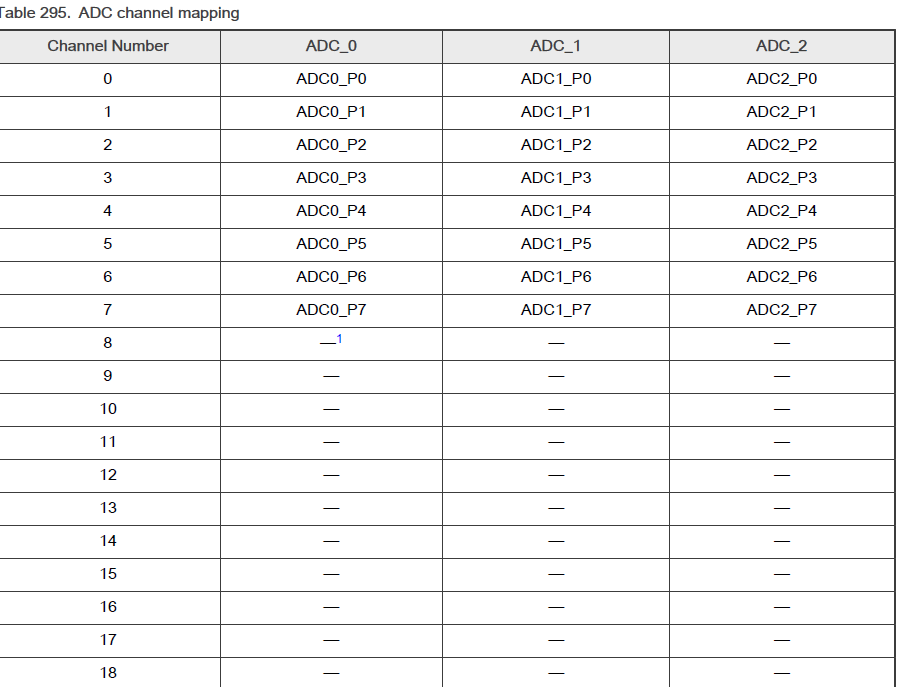

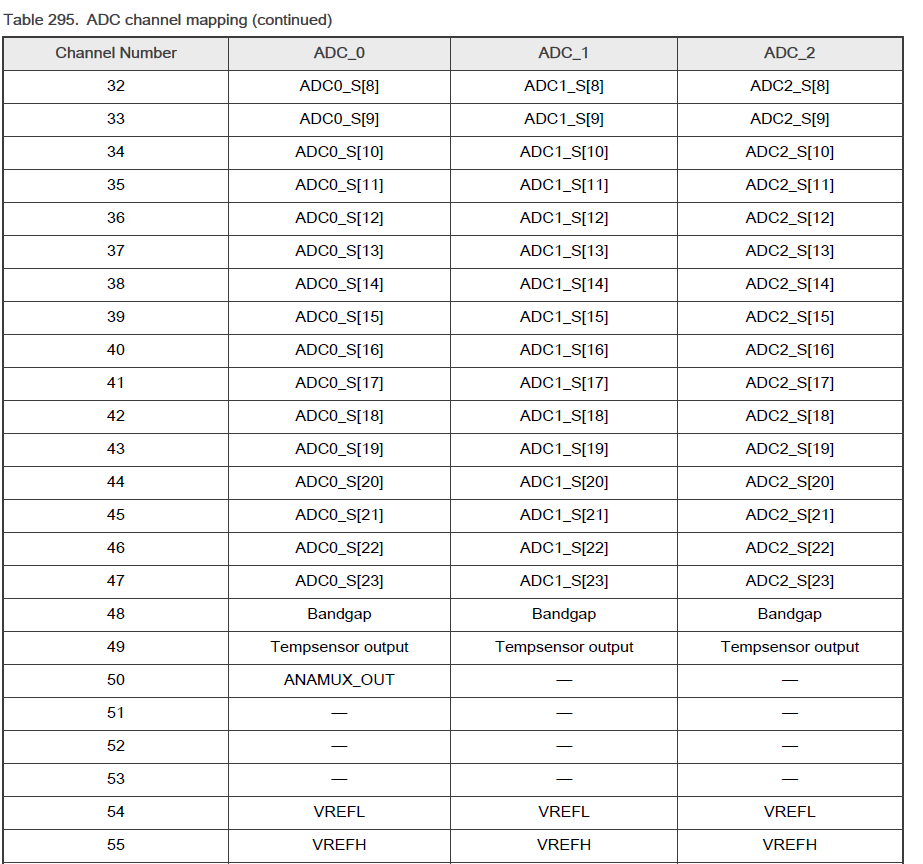

该芯片最多有3个ADC实例。ADC通道分为3组-精密,标准和扩展(每个具有独立的配置设置和不同的精度/性能水平)。ADC配置如下表所示:

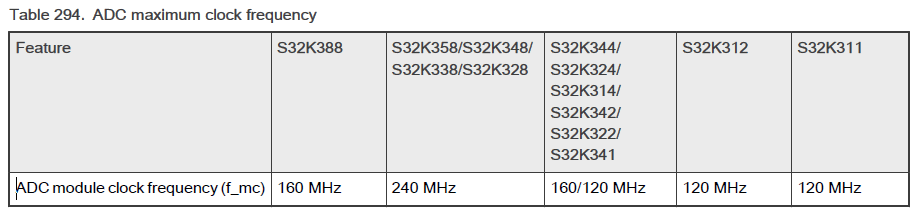

本章中提到的模块时钟为该芯片的CORE_CLK。

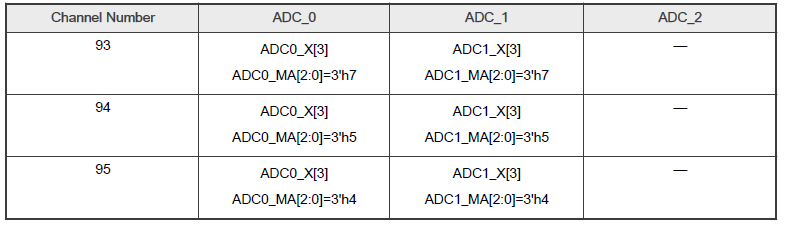

用于内部供应监控的ANAMUX

对应的通道为ADC0-NUM50

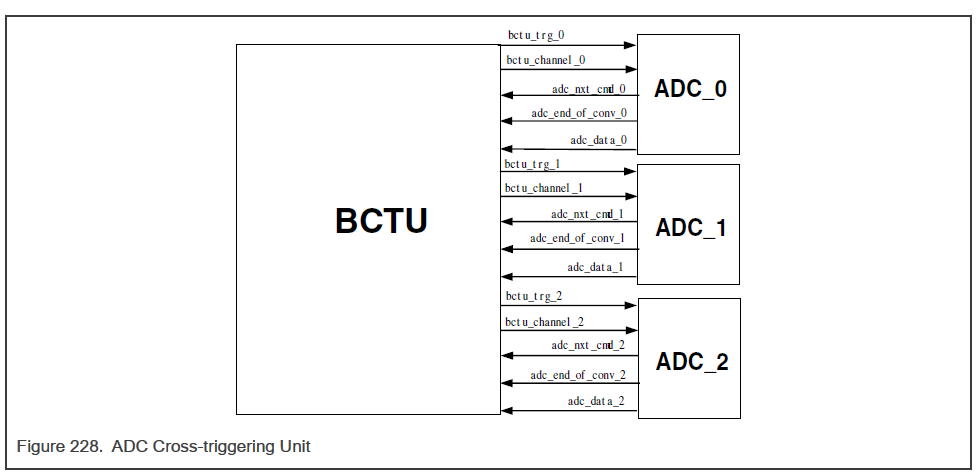

BCTU接口

所有3个ADC实例都从BCTU触发。BCTU为ADC提供通道转换命令(包括通道号信息)。此外,ADC还将转换结果反馈给BCTU

BCTU向ADC的所有72个通道发出触发脉冲,根据BCTU通道号发起转换。

BCTU-ADC结果寄存器

ADC结果寄存器(ADCx_PCDRn[CDATA], ADCx_ICDRn[CDATA]和ADCx_ECDRn[CDATA])存储15位转换数据。BCTU ADC寄存器存储15位转换数据(BCTU_ADC0DR[ADC0_DATA], BCTU_ADC1DR[ADC1_DATA]和BCTU_ADC2DR[ADC2_DATA])。

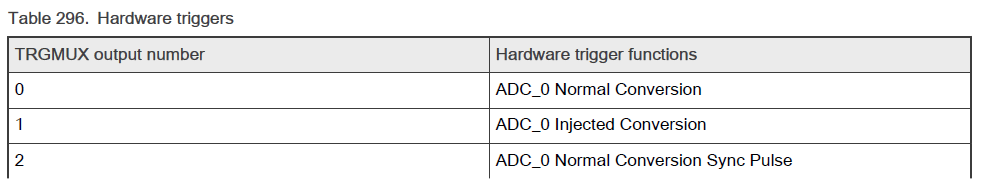

硬件触发

在该芯片中,硬件触发信号可以由TRGMUX输出提供。该特性允许两个独立的ADC实例并行同步转换。如果ADC处于Idle状态(即没有转换阶段正在进行,并且MCR[PWDN]和MCR[ACKO]字段为0),并且设置了MCR[XSTRTEN],则外部启动信号上的事件会导致ADC开始正常或注入转换操作。自动设置MCR[NSTART]/MCR[JSTART]字段。正常转换同步脉冲与正常转换触发器一起使用,以同步正常转换的开始时间

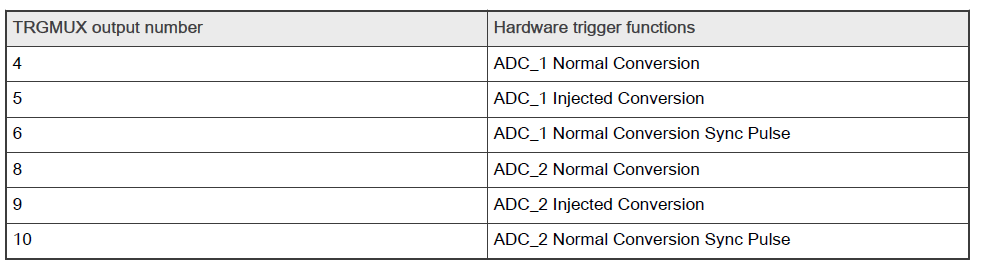

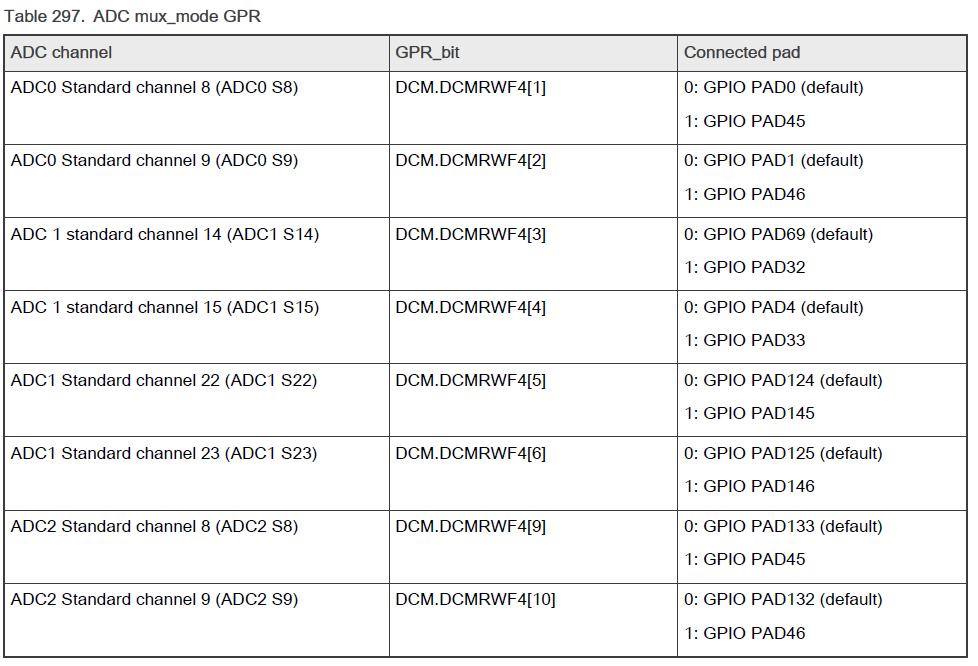

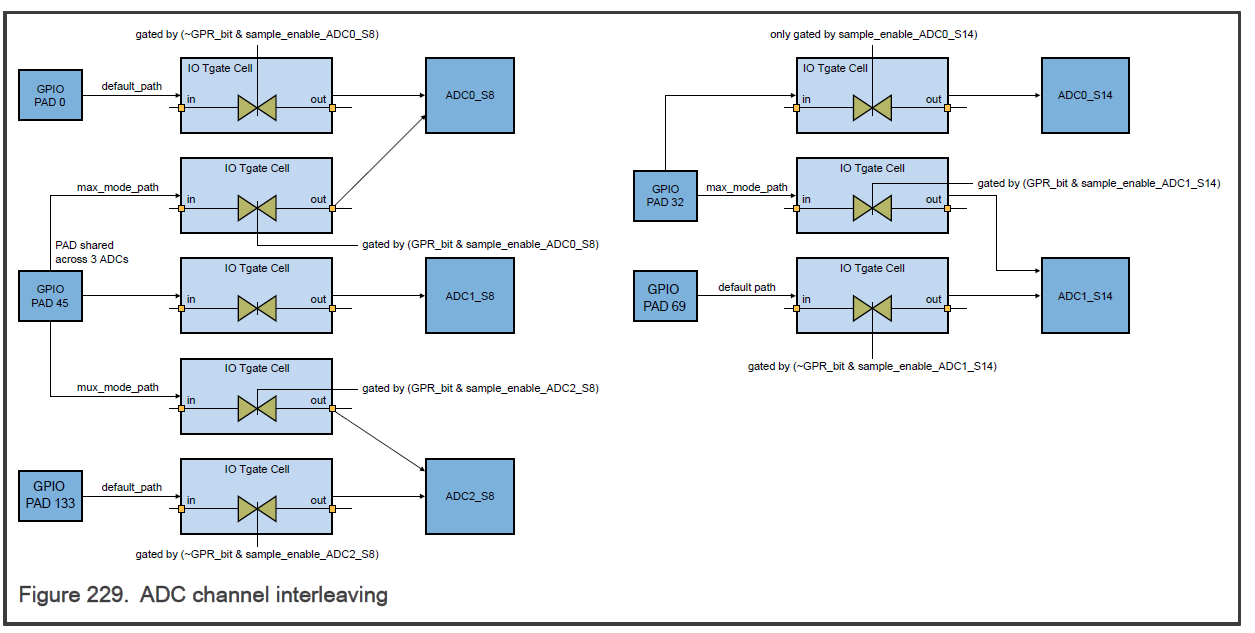

ADC多路模式通道

ADC中有一些通道是由多个pad驱动的。为此,来自DCM的GPR位用于定义哪个pad连接到特定的ADC通道。

例如如下所示,其中ADC0 S8由GPIO_PAD0(默认)和GPIO_PAD45 (mux_mode)驱动。ADC2 S8由GPIO_PAD133(默认)和GPIO_PAD45 (mux_mode)驱动。

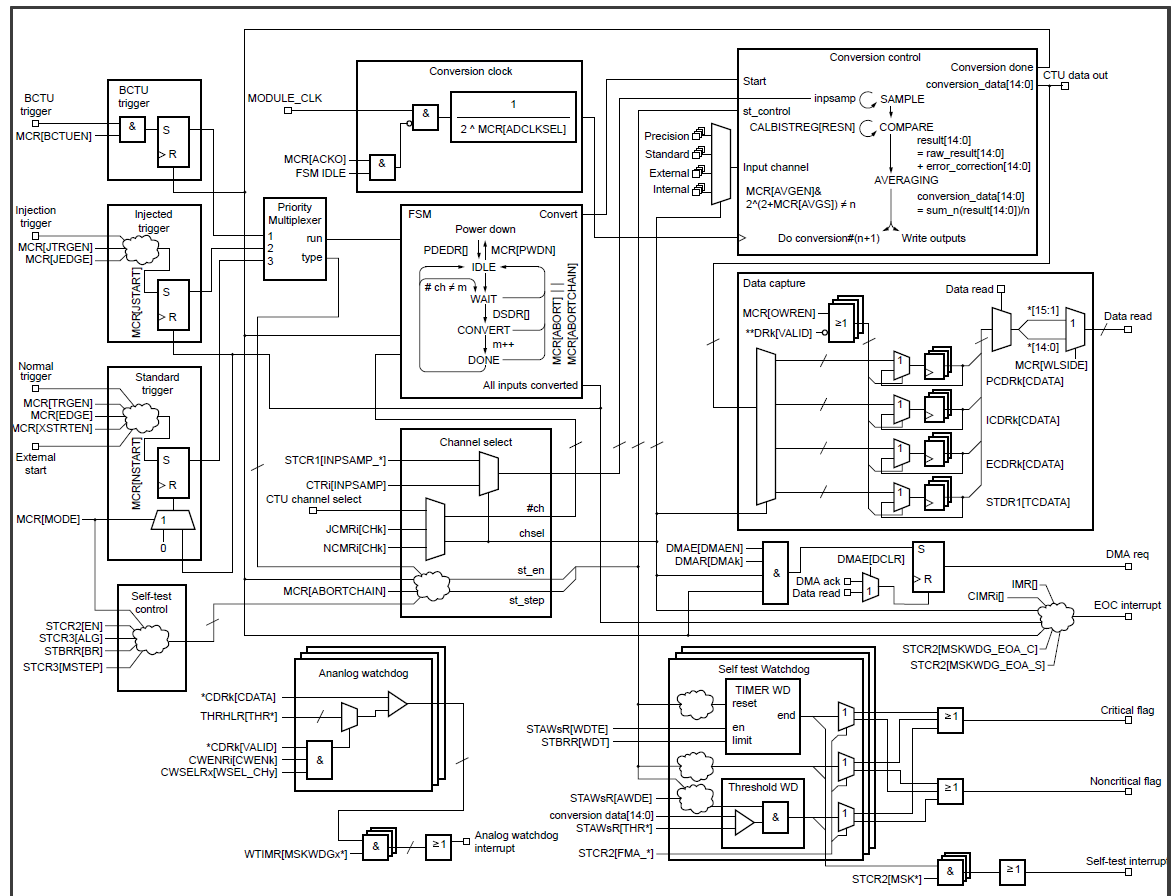

功能框图

解释:

•图中的信号流从左到右:模块的输入在左边,输出在右边。

•寄存器名称是大写的,后面是括号中的字段名(例如“MCR[NSTART]”)。小写字母表示索引。星号是字母(通配符)的占位符。框图中的寄存器名称映射到ADC寄存器描述中的名称。

•所有显示的数字信号都是同步信号。ADC的异步输入是内部同步的(未显示同步器)。

方框图从左到右,从上到下依次显示了信号流经ADC的过程:

1.当ADC接收到三种不同类型的触发器(BCTU、注入或正常)之一时,优先级多路复用器启动转换。

2.根据触发器类型和自检配置,在Channel Select子块中选择要转换的输入。

3.状态机(FSM)由Idle状态转为Convert状态。如果要转换的通道自上次转换以来发生了更改,并且这个新通道是一个外部通道,则转换在DSDR[DSD]配置的延迟之后开始。

4.转换开始后,转换控制块将内部电容网络CDAC保持在采样阶段,时间由CTRi[INPSAMP]定义。

5.在比较阶段,CALBISTREG[RESN]定义用于执行逐次逼近算法的步数。在校准过程中确定的error_correction值被添加到原始结果中。如果启用了平均(MCR[AVGEN] = 1),将对最多32个(通过MCR[AVGS]指定)转换结果进行平均以获得结果。

6.当转换完成并且所有平均步骤都完成时:

a.转换完成信号表示完成。

b.Conversion_data[14:0]被写入Data Capture子块中的结果寄存器。

c.FSM状态变为“Done”

7.Channel Select块中的下一个输入被选中,下一个转换由FSM转换到Convert状态开始。这一直持续到所有选定的输入都转换完毕。

8.如果开启模拟看门狗,转换结果与配置的阈值进行比较。如果超过限制,就会触发中断。

9.自检可以检查ADC的完整性,可以与正常转换交替进行,也可以作为独立的检查。

10.如果正在进行的转换被中止(将1写入MCR[ABORT]),或者正在进行的一组输入通道的转换被中止(将1写入MCR[ABORTCHAIN]), FSM将进入Idle状态。如果MCR[ABORT]被写入1,则转换控制块停止当前转换;如果MCR[ABORTCHAIN]被写入1,则完成当前转换。在这两种情况下,转换控制块的转换完成输出信号被设置为1。

部分细节未在框图中显示:

•在ADC进行有意义的转换之前,必须执行校准以确定error_correction值(参见校准)。

•输入端可以对内部低或高参考电压进行预采样,以避免由于之前的转换而在比较中可能出现的记忆效应(参见预采样)。

•通过状态标志监视ADC状态。

特点

•可选择的分辨率(8-,10-,12-,14位)。注意转换结果总是15位宽,即使选择的分辨率较小(参见CALBISTREG[RESN])

•在每个输入通道的单独寄存器中捕获的转换数据。

•选择通过平均来提高准确性,通过平均多达32个转换的数据来计算转换数据。

•转换触发:

- 普通转换触发器转换许多输入通道,每次触发器转换一次或连续转换。

- 注入转换触发器中断正在进行的正常转换并转换另一组输入通道。

- BCTU转换触发器中断正在进行的转换并转换一个输入通道,其中选择输入并通过BCTU开始转换。

•模拟看门狗可选地监控每个输入通道的转换数据,并在转换数据低于或高于可配置限制时发出中断。

•DMA功能将转换数据传输到其他模块。

•当一个或一组输入通道的转换完成时,可编程中断可选地发出中断。

•自检函数在功能操作期间验证ADC结构的完整性,并在任何发现时生成不同严重程度的事件。

•转换时钟(AD_clk)控制可以通过使用内部时钟分压器在具有更高时钟频率的系统中使用ADC。

•当ADC空闲时自动关闭转换时钟

功能描述

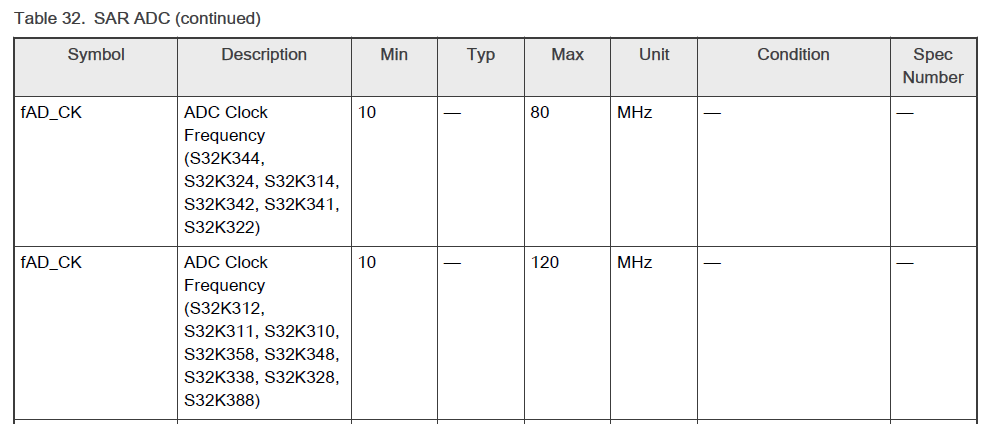

时钟

ADC由一个时钟信号控制,即模块时钟。在内部,转换电路由转换时钟控制,转换时钟来源于模块时钟。

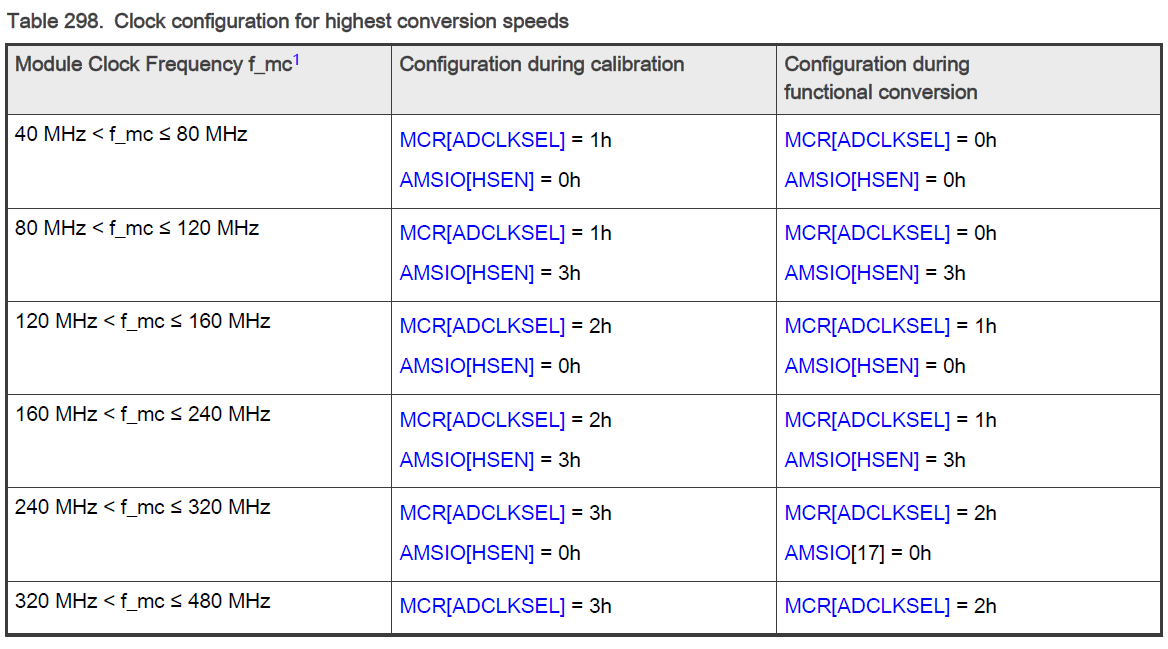

转换时钟的频率必须在数据表中定义的范围内。如果模块时钟频率高于功能转换或校准期间允许的转换时钟的最大频率(参见芯片数据表),则必须配置ADC转换时钟分频器(MCR[ADCLKSEL]),以便转换时钟的频率在允许的范围内。对于某些转换时钟频率,必须将3d写入AMSIO[HSEN]。见表298

转换

ADC测量信号的电压-它将模拟输入值转换为数字表示。读取转换结果时,必须将此转换结果除以codes(由CALBISTREG[RESN]中所选转换分辨率定义),并将其与参考电压值相乘。这个计算提供了转换信号的电压值

要将模拟输入电压转换为数字表示,ADC:

1.接收一个信号,称为触发器,表示它要执行转换。

2.在称为采样的过程中通过内部电容捕获信号的电压。

3.使用SAR算法将电压与参考电压进行比较。

在执行转换之前,您必须选择:

•要使用的触发器源(在芯片级上)

•需要转换的输入通道(NCMR0-2, JCMR0-2)

此外,您可以通过更改默认配置来定制转换以满足您的需求。例如,你可以:

•将ADC配置为只转换一次所选输入通道或在循环中连续转换(MCR[MODE])。

•指定ADC对输入信号采样的持续时间(CTR0/1/2)。

•通过选择位数(CALBISTREG[RESN])指定转换结果的分辨率。

•使能模拟看门狗在转换结果超出指定范围时产生中断(参见模拟看门狗功能)。

•允许DMA接口发送请求和接收确认(请参阅DMA功能)。

•通过运行自检(参见自检)来检查ADC的操作完整性。

上电或功能复位后,ADC保持在下电状态,直到将0写入MCR[PWDN]使能。系统上电后,必须运行校准(参见校准),然后才能使用ADC进行有意义的转换。

某些配置字段(下面列出)仅在下电状态下可写。如果您打算写入,则必须在退出断电状态之前这样做。

•选择转换时钟频率,使其处于允许的转换限制范围内。

正常触发

通过配置“NCMR0”、“NCMR1”和“NCMR2”字段,选择需要转换的输入通道。

这些寄存器必须在转换开始之前编程。在完成所有所选通道的转换之前,不能重新配置它们。该序列总是按以下顺序转换所选的输入通道:

1.从精度输入通道中最低的输入通道开始。

2.按升序进行标准输入通道。

3.以外部输入通道中最高的输入通道结束。

转换模式:

•One-Shot mode-单次转换

•Scan mode-连续转换

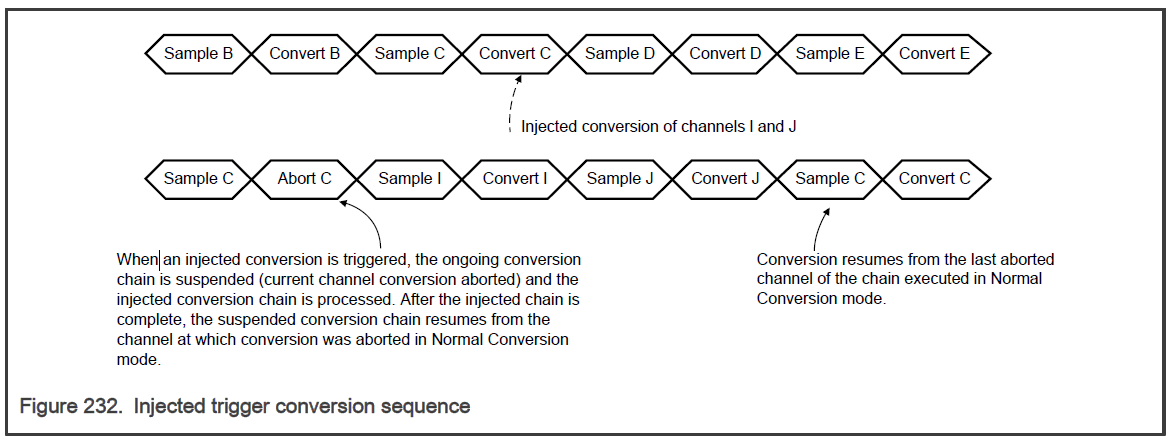

注入触发

注入触发器使您能够转换一组输入通道,尽管标准触发器已经开始转换另一组输入通道。通过将1写入JCMR0、JCMR1或JCMR2中的相应字段,可以单独启用每个通道。

注入触发可以打断之前的正常触发,注入触发结束后,之前的正常触发可以继续执行

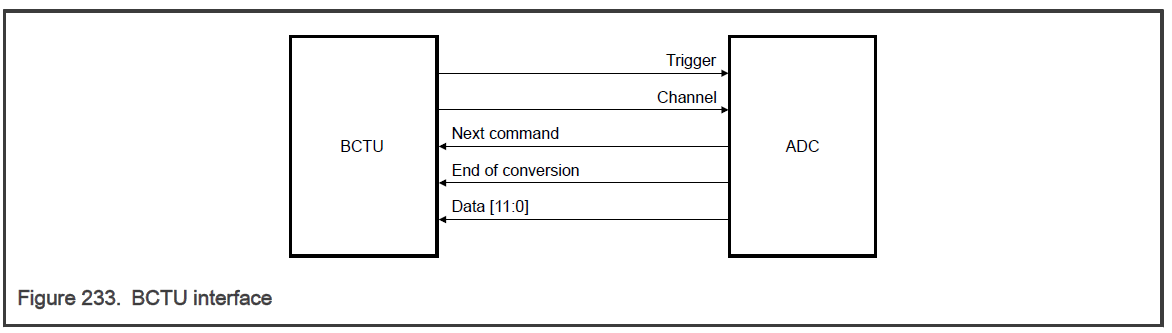

BCTU接口

BCTU接口增强了ADC的注入转换能力。它包含控制输入,用于选择要从适当的事件配置寄存器转换的通道。图233显示了该接口。

BCTU生成一个触发器(bctu_trigger)和一个要转换的通道号(bctu_numchannel)。为每个请求转换一个通道。在执行转换后,ADC在bctu_dataout总线上返回结果,并返回两个名为bctu_nextcmd和bctu_push的输出信号。信号bctu_nextcmd的断言意味着ADC已经准备好接受来自BCTU的下一个触发器。bctu_push信号在转换结束时被断言,这意味着转换已经完成,在输出bctu_dataout处可用的转换结果是有效的。

转换结果也保存在相应通道的数据寄存器中,并在请求时与模拟看门狗阈值进行比较。

bctu_trigger、bctu_nextcmd、bctu_push信号在ADC时钟域均为单周期active-high-pulse类型。当BCTU触发器为active-high时,BCTU提供的通道号必须有效。来自ADC的结果数据使用bctu_push high有效。

如果要启用BCTU接口,请将1写入MCR[BCTUEN].。操作模式(触发或控制)可以固定或可编程

BCTU Trigger mode

在触发模式下,也可以执行正常转换和注入转换。所有类型的转换都可以在此模式中启动。下面将讨论这三种类型转换的优先级。

当接收到触发器时,通道号被作为注入通道值,触发的注入转换开始。MSR[BCTUSTART]在这一点上自动转换为1,当触发的注入转换完成时,它也自动重置为0。

只有在ADC校准成功后,才必须要求进行BCTU转换。在校准过程中,应用程序必须防止任何BCTU触发。

如果在正在进行的注入转换期间接收到BCTU触发器,则注入链立即中止,只有BCTU触发的注入转换继续进行。此外,MSR[JSTART]被重置为零。注入转换的中止由MSR[JABORT]指示。

如果在正在进行的正常信道转换中接收到BCTU触发,则正在进行的正常信道转换暂停,并处理BCTU触发的注入转换。完成bctu触发的转换后,正常的转换将从暂停的通道恢复。

如果在BCTU转换(MSR[BCTUSTART] = 1)过程中请求正常转换,则BCTU转换完成(MSR[BCTUSTART]复位为零)后开始正常转换。

如果在BCTU转换期间请求,任何注入转换都将被丢弃,MCR[JSTART]将立即重置为零。

BCTU Control mode

在BCTU控制模式(MCR[BCTU_MODE] = 0)下,只有BCTU可以开始转换。忽略所有其他触发源。

在触发BCTU的同时,bctu_numchannel信号所提供的信息被作为注入通道的通道号,BCTU触发转换开始。MSR[BCTUSTART]在转换开始时自动转换为1,并且它保持为1,除非BCTU通过将0写入MCR[BCTUEN].而禁用。

当校准成功完成时,必须请求转换(生成bctu_trigger)。如果在校准执行过程中接收到BCTU触发器,校准将立即停止,以满足BCTU要求。在这种情况下,校准失败。

配置ADC时钟分压器和采样时间设置

您可以通过MCR[ADCLKSEL]缩放AD_clk频率。ADCLKSEL只能在Power Down状态(MCR[PWDN] = 1)下被写入。根据模块时钟的频率,功能转换和校准可能需要不同的设置。有关ADC电气特性,请参阅芯片数据表

使用三个转换计时寄存器(CTRn)来支持不同类型通道的不同采样时间。温度传感器通道存在一个例外,它总是使用标准输入转换时序(CTR1)值。详细信息请参见寄存器描述。

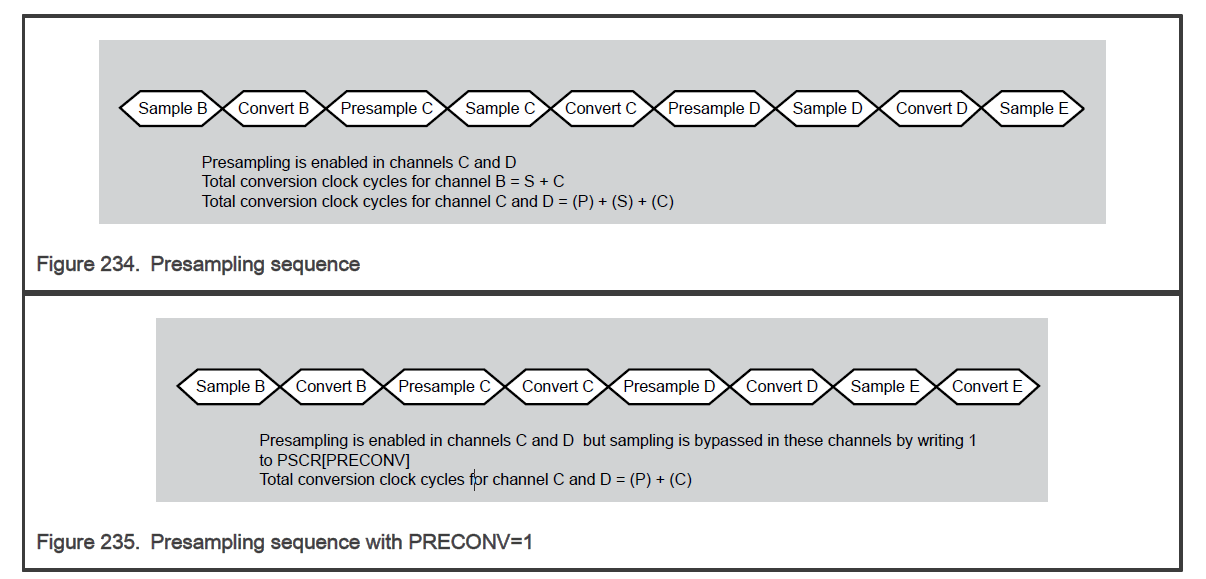

预采样

预采样特性使ADC内部采样电容节点在选定的模拟输入通道开始采样之前预充或放电到定义的水平。这对于从最近的转换中重置信息(历史效果/偏移量)非常有用。在预采样期间,ADC对内部产生的电压进行采样。在采样阶段,ADC对来自电板的模拟输入进行采样。

通过将PSRn寄存器中的相应字段设置为1,在每个通道的基础上启用预采样。

开启信道预采样后,信道的正常操作顺序为:

1.Presampling

2.Sampling

3.Evaluation

您可以通过向PSCR[PRECONV]写入1来绕过所有通道的采样。当一个通道的采样被屏蔽时,在预采样阶段施加的采样和存储内部电压被转换(图234)。有关转换的时间方程,请参阅转换时间。

预采样不适用于自检通道。

通过设置PSCR[PRECONV],使得配置了预采样的通道屏蔽采样过程。预采样后直接进行转换

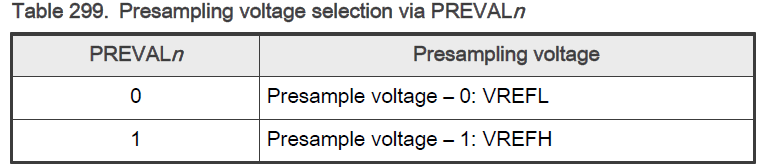

启用每个通道的预采样

通过编程预采样控制(PSCR)为特定通道启用预采样。通过将预采样控制(PSCR)中的PREVALn字段配置为适当的值,可以在两个内部生成的电压之间进行选择,如下表所示。

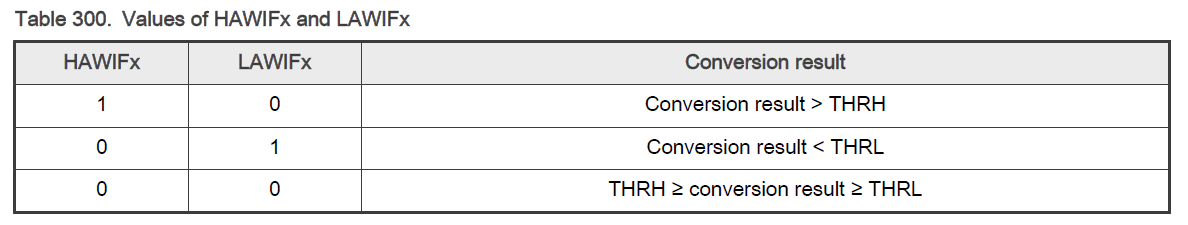

模拟看门狗功能

启用后,模拟看门狗监视关联信道的转换结果,并在确定结果超出客户定义的限制时报告问题(如模拟看门狗配置(最多16个看门狗)所示)。这些限制分别由一个名为THRH和THRL的上限和下限阈值指定。

在所选通道转换后,在转换后的值和阈值之间进行比较。如果转换的值超出该阈值,则ADC生成相应的阈值违反中断

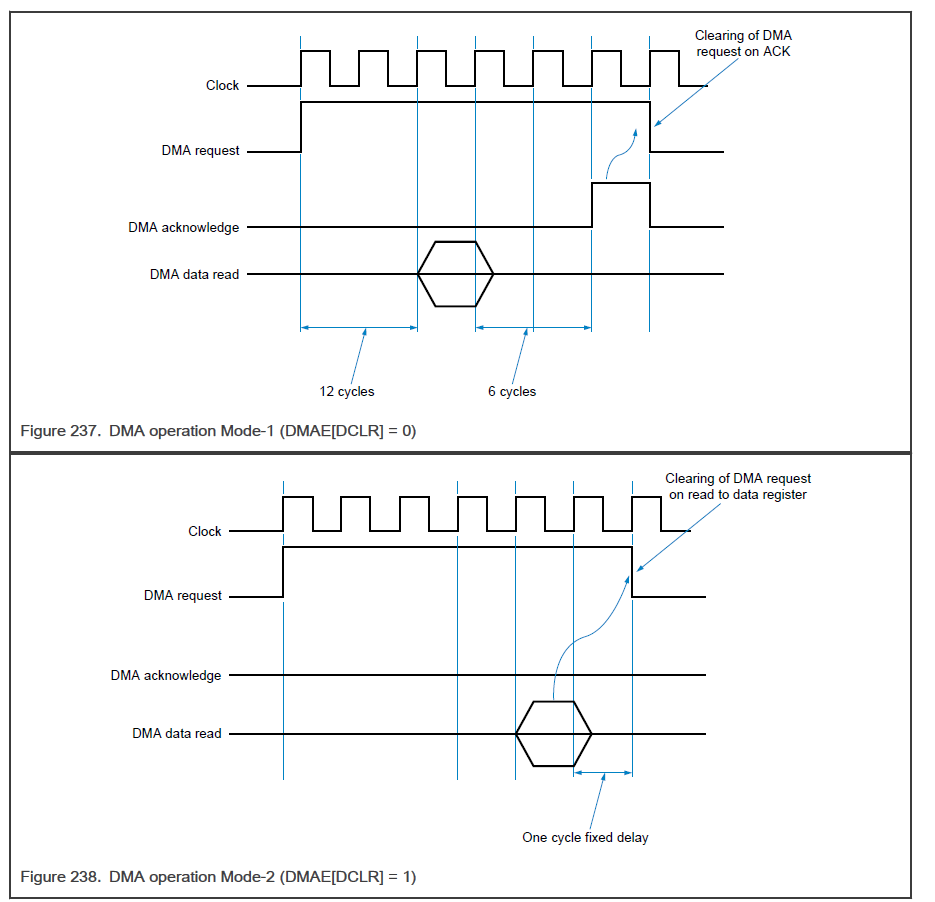

DMA功能

来自任何通道的转换结果数据都可以通过直接内存访问(DMA)从寄存器传输到系统内存。DMA传输通过写入1到DMAE[DMAEN]来实现。启用后,片上DMA控制器可以在每个通道转换后通过将1写入相应的掩码字段来接收DMA请求

•DMA Request Enable For Precision Inputs (DMAR0)

•DMA Request Enable For Standard Inputs (DMAR1)

•DMA Request Enable For External Inputs (DMAR2)

对DMA控制器的DMA请求可以在两种模式下的不同时间被清除:

•模式1:DMA控制器确认DMA请求时清除(DMAE[DCLR] = 0)

•模式2:在读取数据寄存器时清除DMA请求(DMAE[DCLR] = 1)

下图显示了DMA在两种模式下的操作(周期计数是典型值)。

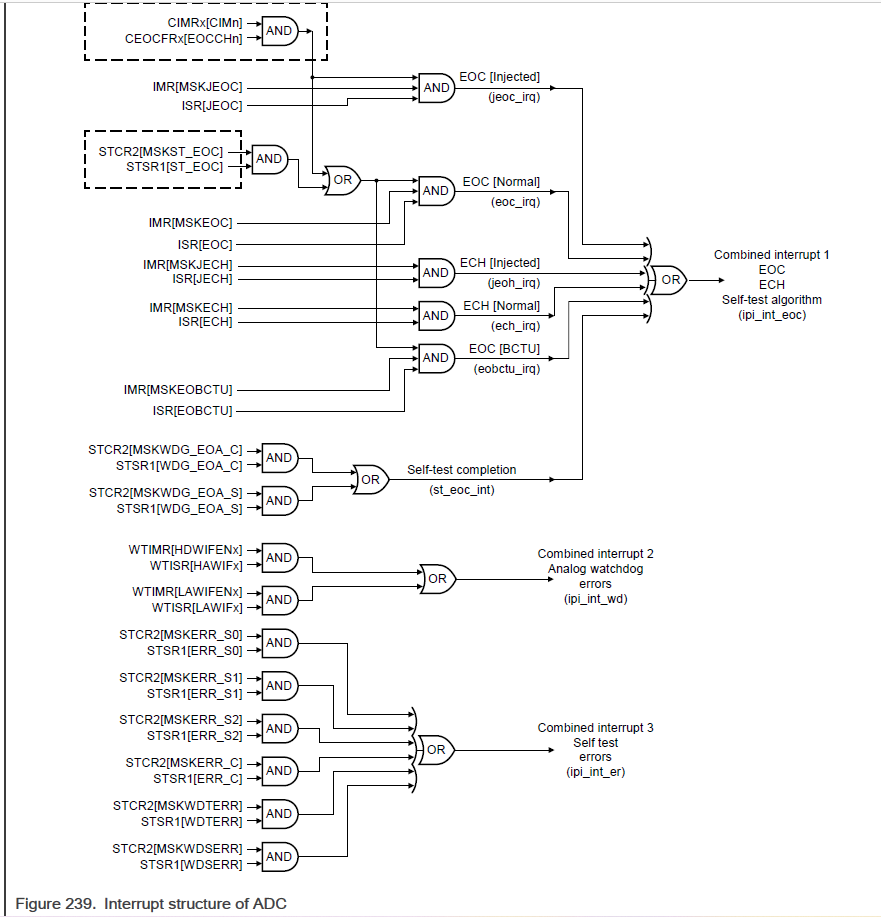

中断

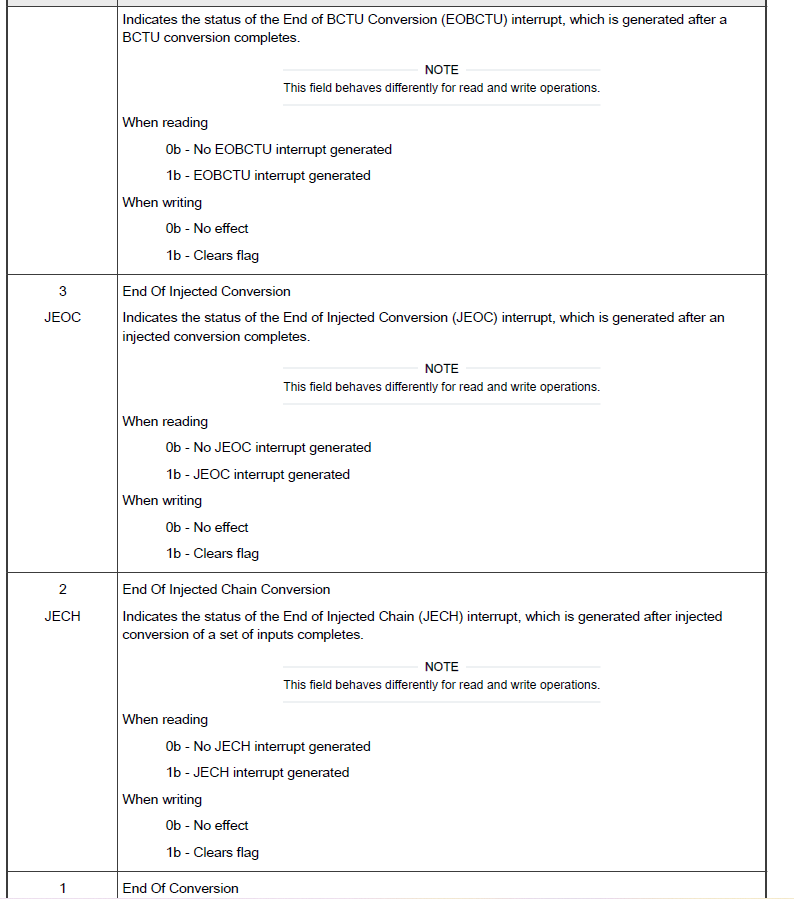

ADC生成以下可屏蔽中断:

•EOC (End of Conversion)转换结束

•ECH (End of Chain)链结束

•JEOC (End of Injected Conversion)注入转换结束

•JECH (End of Injected Chain)注入链结束

•EOBCTU (End of BCTU-triggered Conversion)BTCU触发转换结束

•LAWIFx and HDWIFx (Watchdog threshold)看门狗阈值超过触发的中断

•Self-testing interrupts自测中断

中断合并:

自动关闭模式

为了减少空闲状态(不进入下电状态)的功耗,可以通过向MCR[ACKO]写入1来启用自动关闭功能。当启用时,内部ADC工作时钟(AD_Clk)在空闲期间自动关闭(例如,没有编程转换)。

校准和自测

Calibration

ADC必须经过校准才能进行有意义的转换。在正在进行的校准成功完成之前,应用程序必须防止任何转换的开始。在校准过程中不能接收转换触发器。

在校准过程中,在受控条件下采样并转换已知参考电压,以确定偏置、增益和电容失配的校正值(校准值)

Self-test

为了安全起见,定期检查操作是否正确是很重要的。ADC为此提供了自检功能。当启用自检时,ADC自动检查其组件并标记错误,如果发现任何错误。

可以启用测试以检查参考值(VrefH)和校准值。

Conversion time

总转换时间取决于转换时钟频率,该频率由编程MCR[ADCLKSEL]配置。

转换时间和影响配置的分量为:

•PST-预采样时间

•ST-采样时间

•CT-转换时间

•DP-数据处理时间

•TPT-触发处理时间

数据处理时间为AD_clk的2个周期。在这些周期中,原始转换数据被校正为偏置、增益、电容不匹配等。

触发处理时间包括:

•一个module_clock周期,用于准备通道并计算ADC用于第一次转换的初始增益值。

•BCTU触发时间:

- 来自同步BCTU接口的触发器需要模块时钟的1个周期来处理。在同步模式下注册BCTU触发器还需要一个周期。

Total_conversion_time = ( [(PST + ST + CT + DP) × chain_length] + TPT) × TAD_clk

示例:

ADC控制器时钟等于模块时钟(80mhz,时钟周期= 12.5 ns)

•ADC分辨率12位+ 1位专用电容(CS)

•在NCMRn中编程了三个通道,chain_length=3

•指定默认采样时间(22个周期)

•没有presampling

•转换时间(每位4个周期)

三次转换的总时间= [(0 + 22 + (4×13) + 2) × 3] + 1 = 229cycles~= 2.862 μs

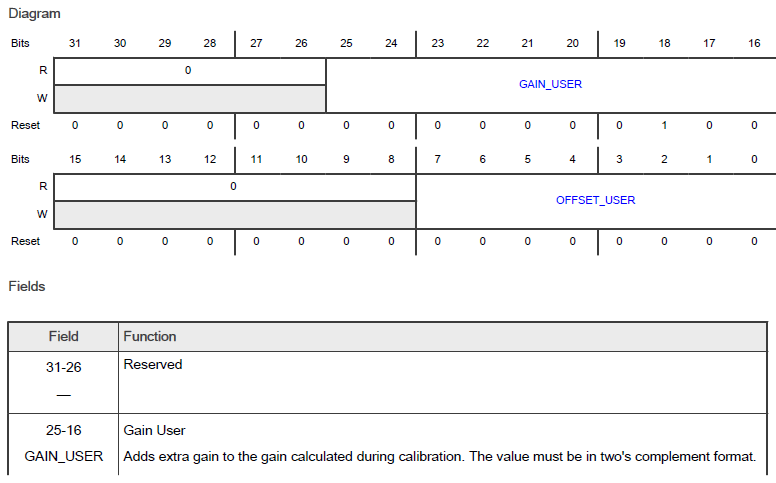

User-defined offset and gain values

除了ADC计算的偏置值和增益值外,ADC还允许您在偏置和增益uer(OFSGNUSR)中指定另一组偏置和增益值。这些值必须以二进制补码格式存储,其中最左边的位(最有效的位)是符号位。

Clock frequency

ADC的内部块设计为输入时钟频率达到Fin(输入信号带宽)最大(参见芯片数据表中的ADC电气规范部分)。指定的速度可以通过这个时钟频率来实现。

如果输入时钟频率超过指定的最大频率,ADC精度会降低,在最坏的情况下,ADC会故障。如果输入时钟频率低于指定的最小频率,ADC精度也会降低。采样时间有一个绝对最大值,以保证规定的参数和精度。对于较慢的时钟,采样时钟计数必须相应编程。

Memory map and register definition

ADC_0 base address: 400A_0000h

ADC_1 base address: 400A_4000h

ADC_2 base address: 400A_8000h

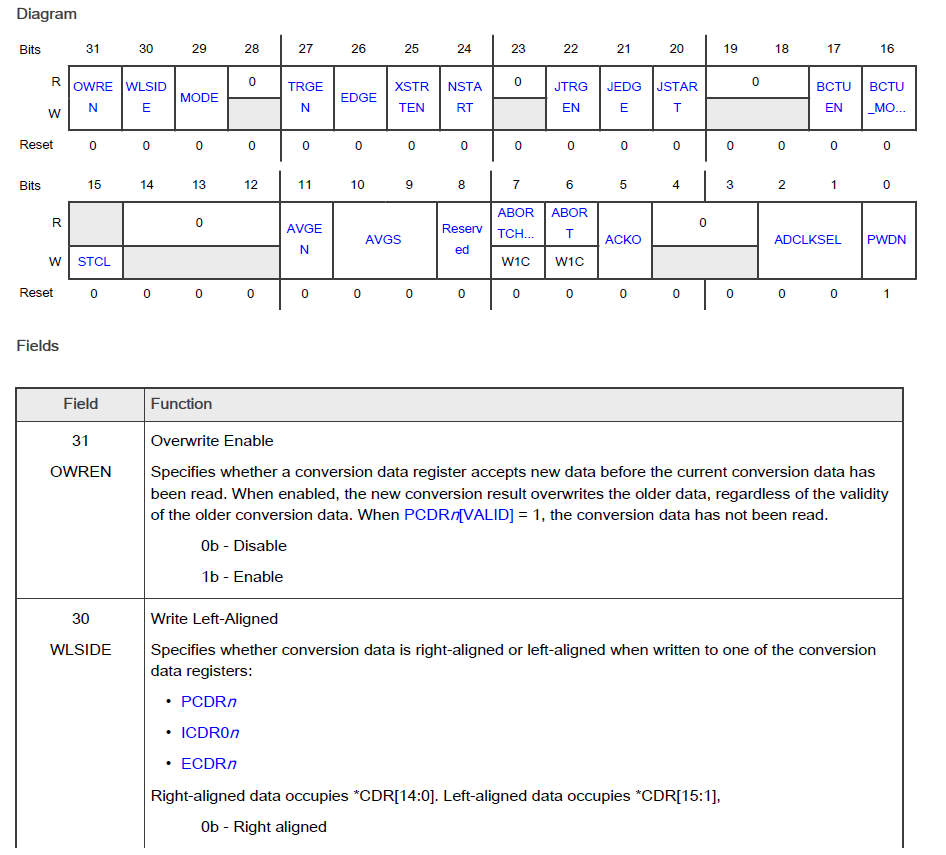

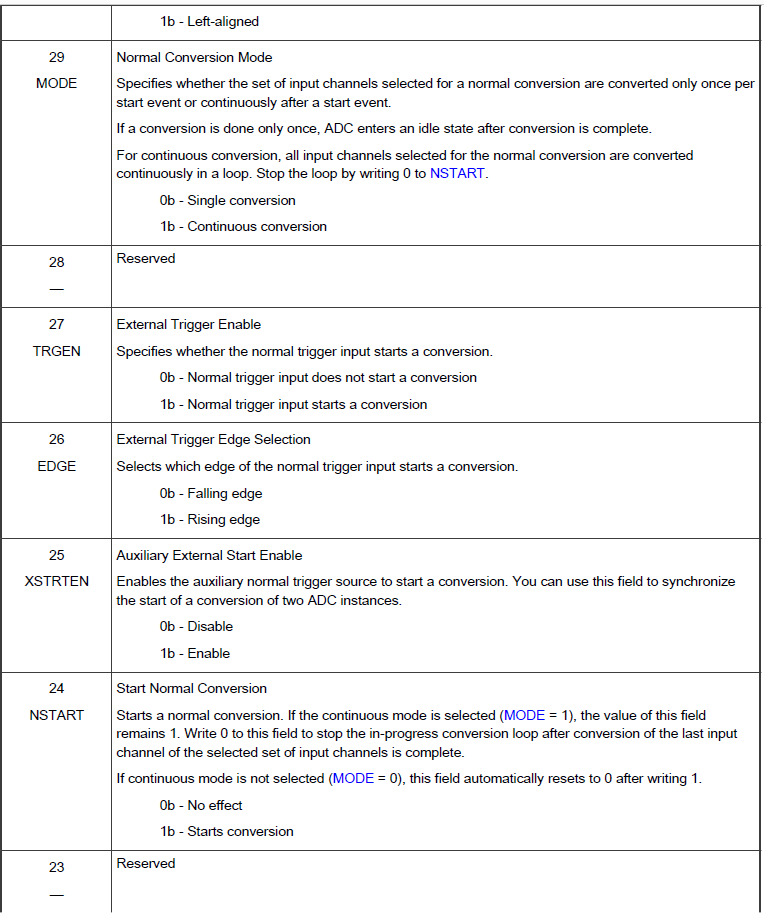

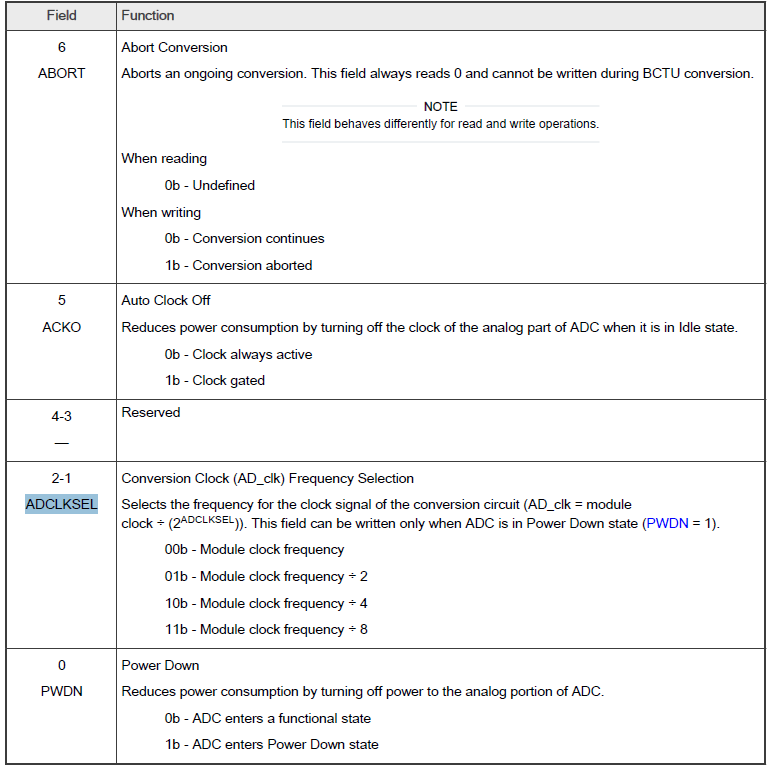

Main Configuration (MCR)

配置大多数ADC特性。只有当ADC处于Idle状态时,才必须更改字段值,ABORTCHAIN和ABORT字段除外。

OWREN:指定转换数据寄存器在读取当前转换数据之前是否接受新数据。启用后,新的转换结果将覆盖旧数据,而不管旧转换数据的有效性如何。当PCDRn[VALID] = 1时,表示尚未读取转换数据

WLSIDE:指定将转换数据写入其中一个转换数据寄存器时是右对齐还是左对齐

右对齐数据占用CDR[14:0]。左对齐数据占用CDR[15:1],

MODE:单次转换还是连续转换

TRGEN:指定普通触发器输入是否启动转换。

EDGE:选择普通触发器输入的哪条边开始转换。上升沿或者下降沿

XSTRTEN:使辅助普通触发源启动转换。您可以使用此字段同步两个ADC实例的转换开始。

NSTART:开始正常转换。如果选择连续模式(MODE = 1),则该字段值保持为1。对该字段写入0以在所选输入通道集的最后一个输入通道转换完成后停止正在进行的转换循环。

JTRGEN:启用注入的触发器输入作为源启动转换。

JEDGE:选择注入触发器输入的哪条边开始注入转换。上升沿或者下降沿

JSTART:中断任何正在进行的正常转换,并开始注入转换。该字段自动重置为0。如果一个注入转换已经在进行中,则该字段值保持为1,直到下一个注入转换开始。该字段只能写成1。

BCTUEN:启用BCTU作为触发源。

BCTU_MODE:指定当BCTU作为触发源使能时,BCTU以外的源是否可以开始转换BCTUEN= 1)。仅当ADC处于Power Down状态(PWDN = 1)时,此字段可写。

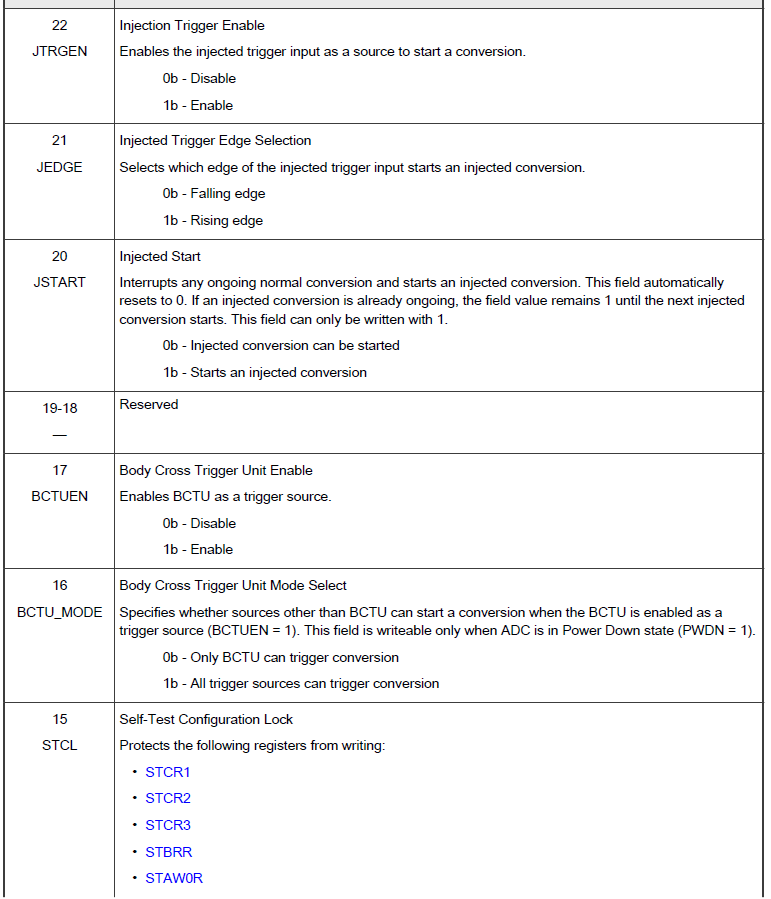

STCL:保护下列寄存器不被写入:•STCR1,STCR2,STCR3,STBRR,STAW0R,STAW1R,STAW2R,STAW4R,STAW5R

AVGEN:启用转换平均。

AVGS:指定ADC用于计算转换结果的转换数。

ABORTCHAIN:中止所选输入通道集(输入通道链)的转换。当前正在进行的转换完成。在BCTU转换过程中不能对该字段进行编程

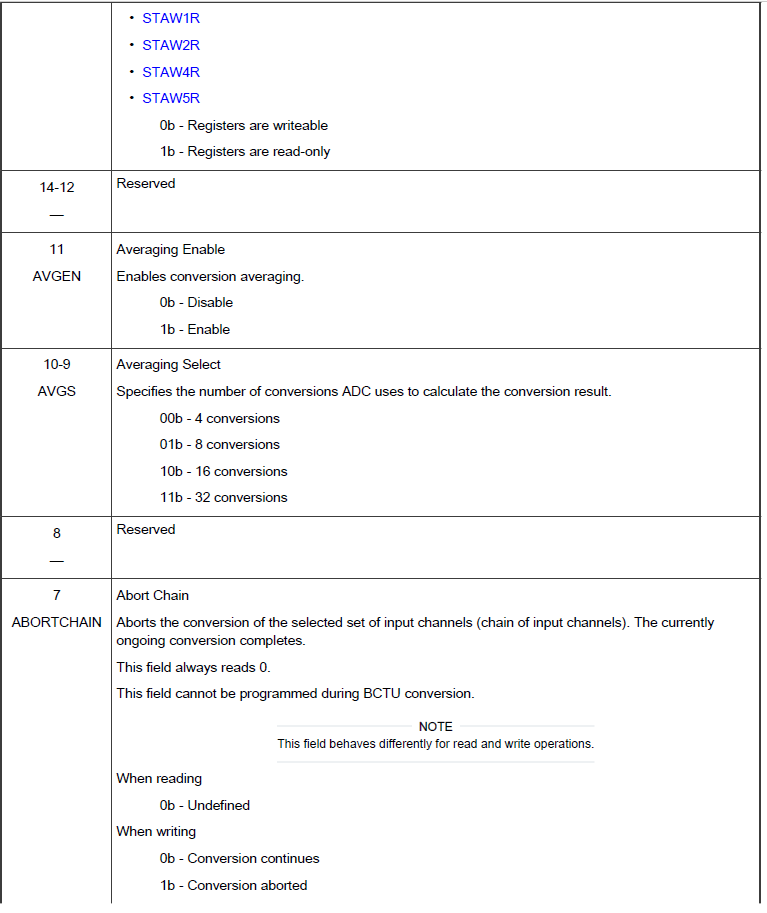

ABORT:中止正在进行的转换。该字段始终为0,BCTU转换时不可写。

ACKO:当ADC的模拟部分处于空闲状态时,通过关闭时钟来降低功耗。

ADCLKSEL:时钟分频

PWDN:通过关闭ADC模拟部分的电源来降低功耗。

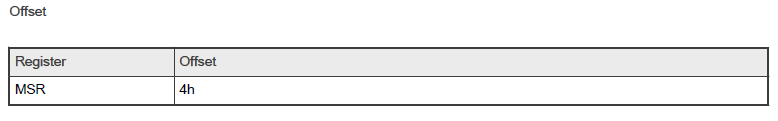

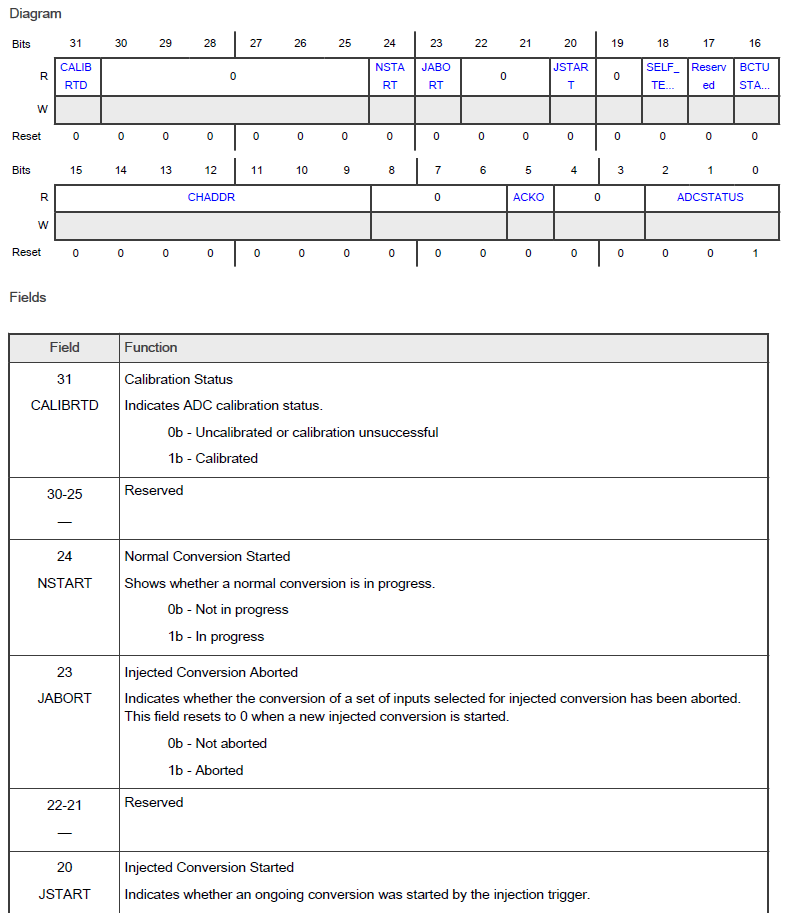

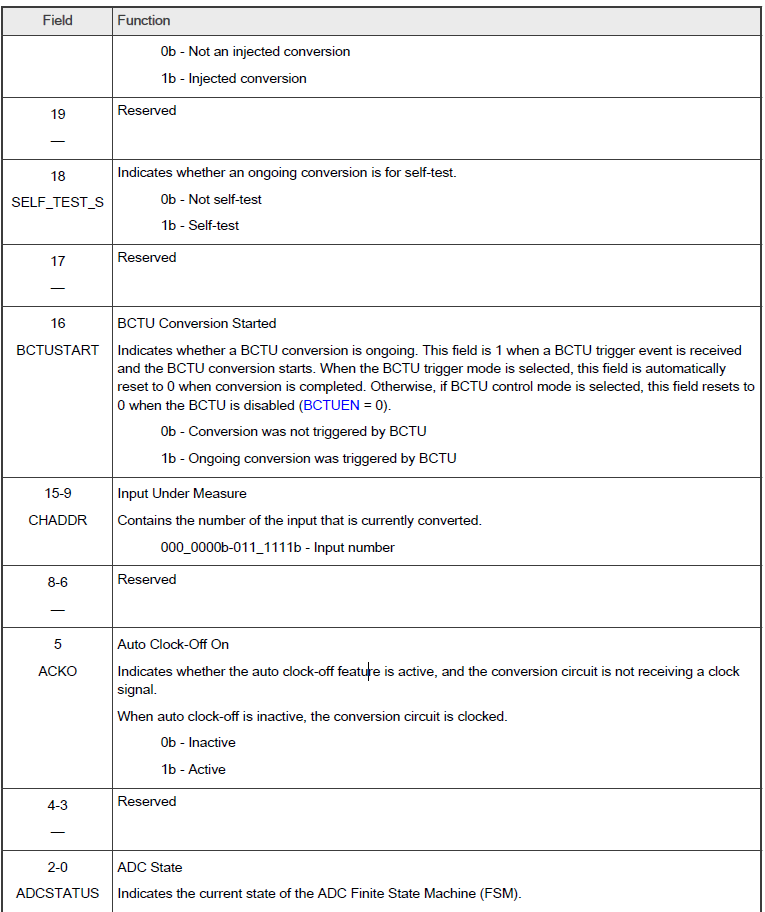

Main Status (MSR)

CALIBRTD:指示ADC校准状态

NSTART:显示是否正在进行正常转换。

JABORT:指示选择用于注入转换的一组输入的转换是否已中止。当一个新的注入转换开始时,这个字段重置为0。

JSTART:指示正在进行的转换是否由注入触发器启动。

SELF_TEST_S:指示正在进行的转换是否用于自检。

BCTUSTART:指示BCTU转换是否正在进行。当接收到BCTU触发事件并开始BCTU转换时,该字段为1。当选择BCTU触发方式时,转换完成后该字段自动重置为0。否则,如果选择了BCTU控制方式,当禁用BCTU时,该字段将重置为0 (BCTUEN= 0)。

CHADDR:包含当前转换的输入的编号。000_0000b-011_1111b - Input number

ACKO:指示自动关闭功能是否激活

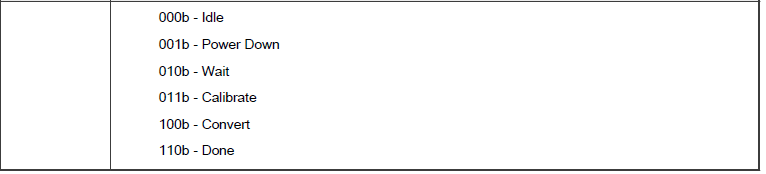

ADCSTATUS:ADC状态

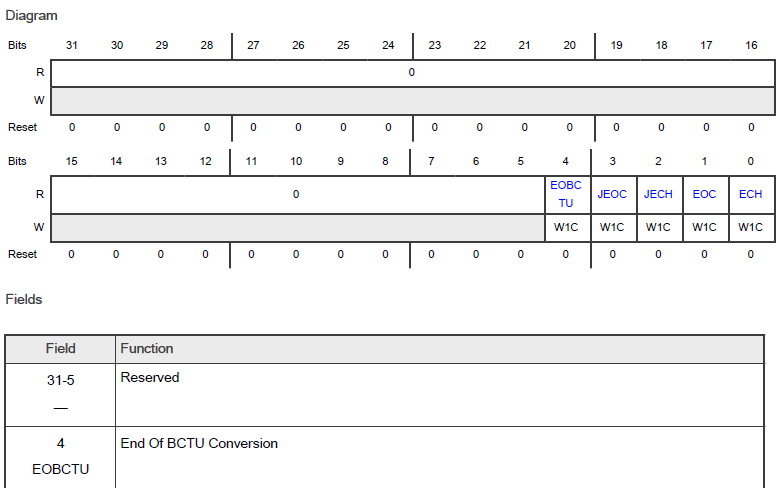

Interrupt Status (ISR)

包含指示中断是否已生成的标志。

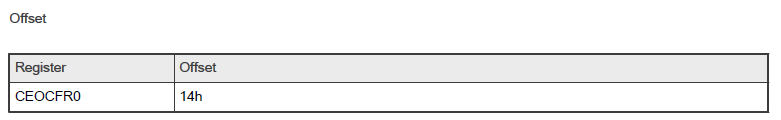

Channel End Of Conversion Flag For Precision Inputs (CEOCFR0)

精确输入转换标志的通道结束(CEOCFR0)

Channel End Of Conversion Flag For Standard Inputs(CEOCFR1)

CEOCFR1是标准转换

Channel End Of Conversion Flag For External Inputs (CEOCFR2)

CEOCFR2是扩展转换

Interrupt Mask (IMR)

启用中断标记。

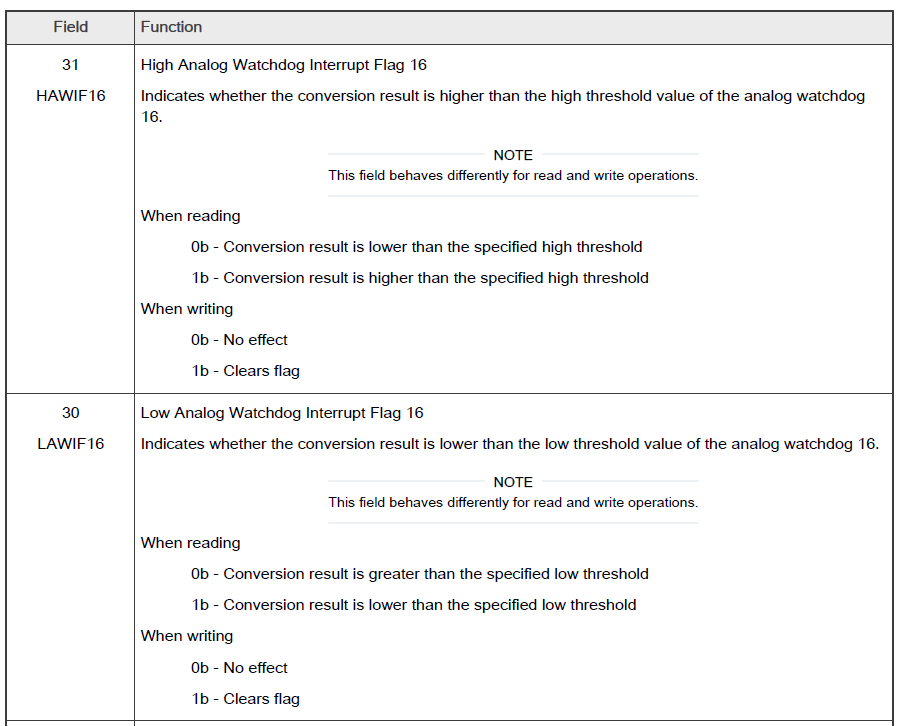

Analog Watchdog Threshold Interrupt Status (WTISR)

包含标志,指示转换结果与模拟看门狗中定义的阈值之间的比较结果。

HAWIF16:转换结果是否高于模拟看门狗16的高阈值。

LAWIF16:转换结果是否低于模拟看门狗16的低阈值。

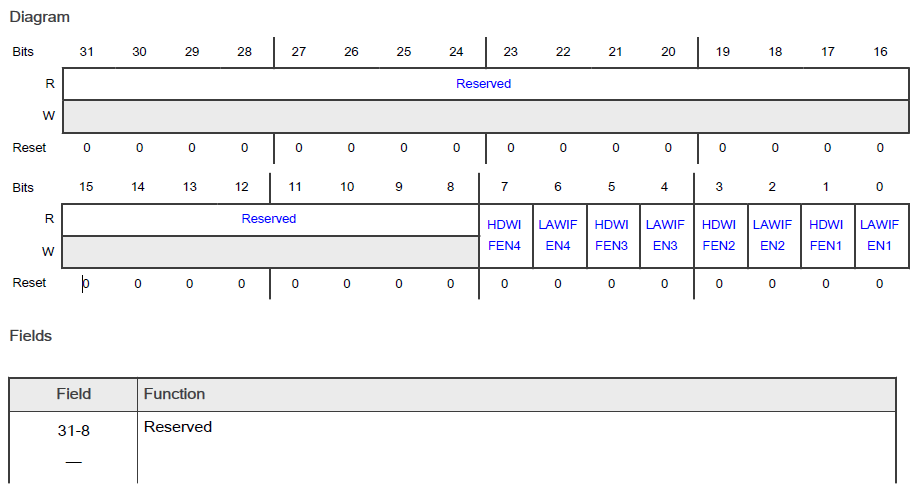

Analog Watchdog Threshold Interrupt Enable (WTIMR)

开启模拟看门狗门限中断。

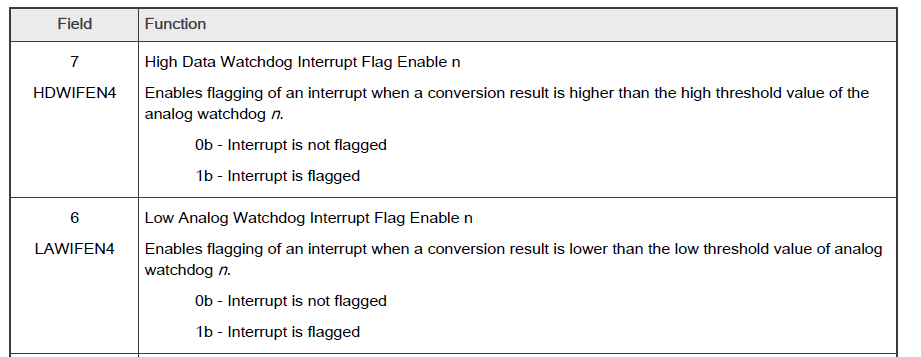

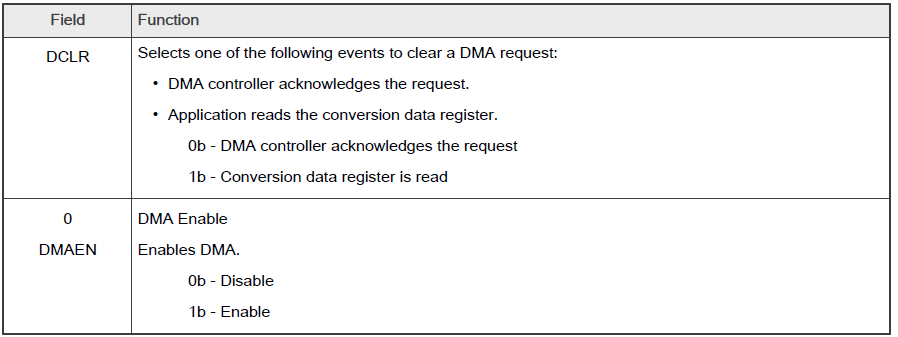

Direct Memory Access Configuration (DMAE)

DCLR:

选择以下事件之一来清除DMA请求:

•DMA控制器确认请求。

•应用程序读取转换数据寄存器。

DMAEN:使能DMA

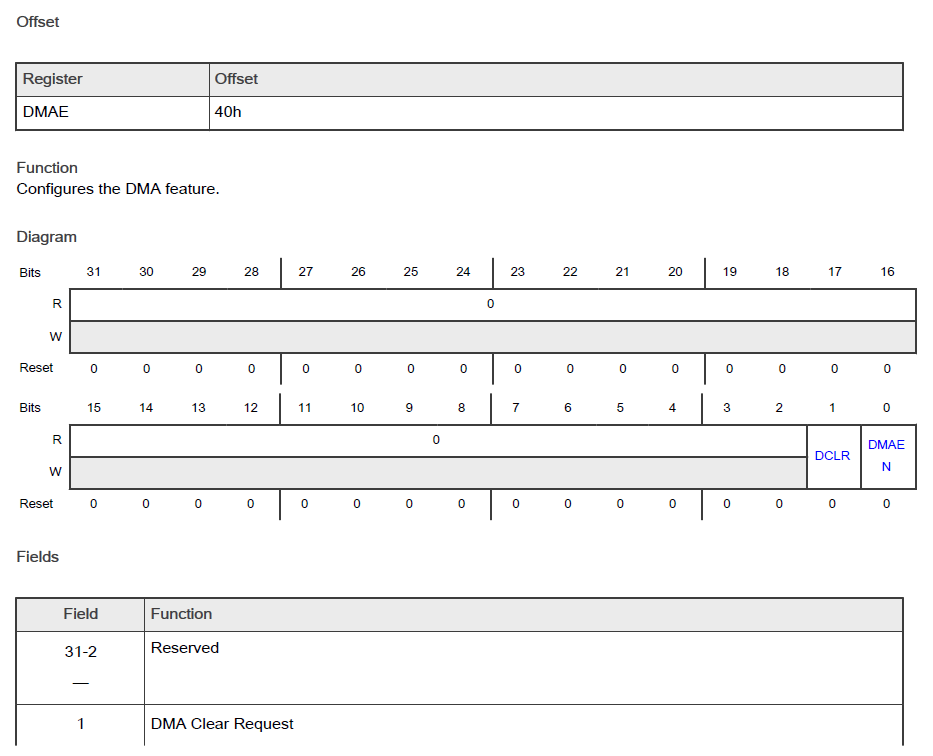

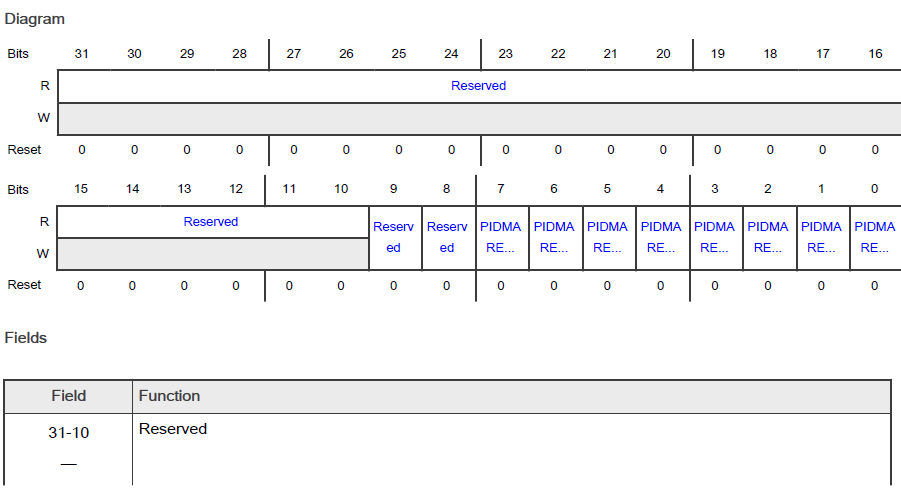

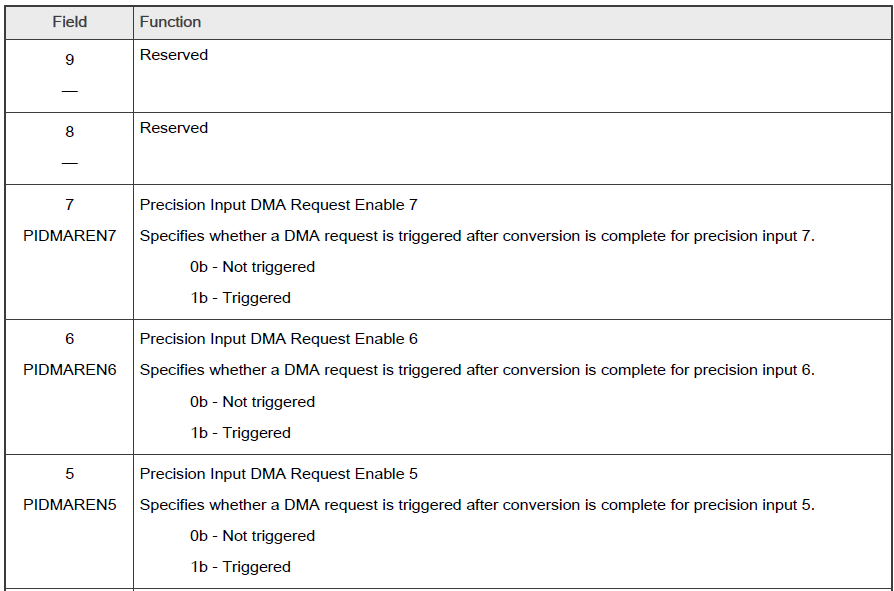

DMA Request Enable For Precision Inputs (DMAR0)

选择在转换完成后触发DMA请求的精确输入。

指定精确输入7的转换完成后是否触发DMA请求。

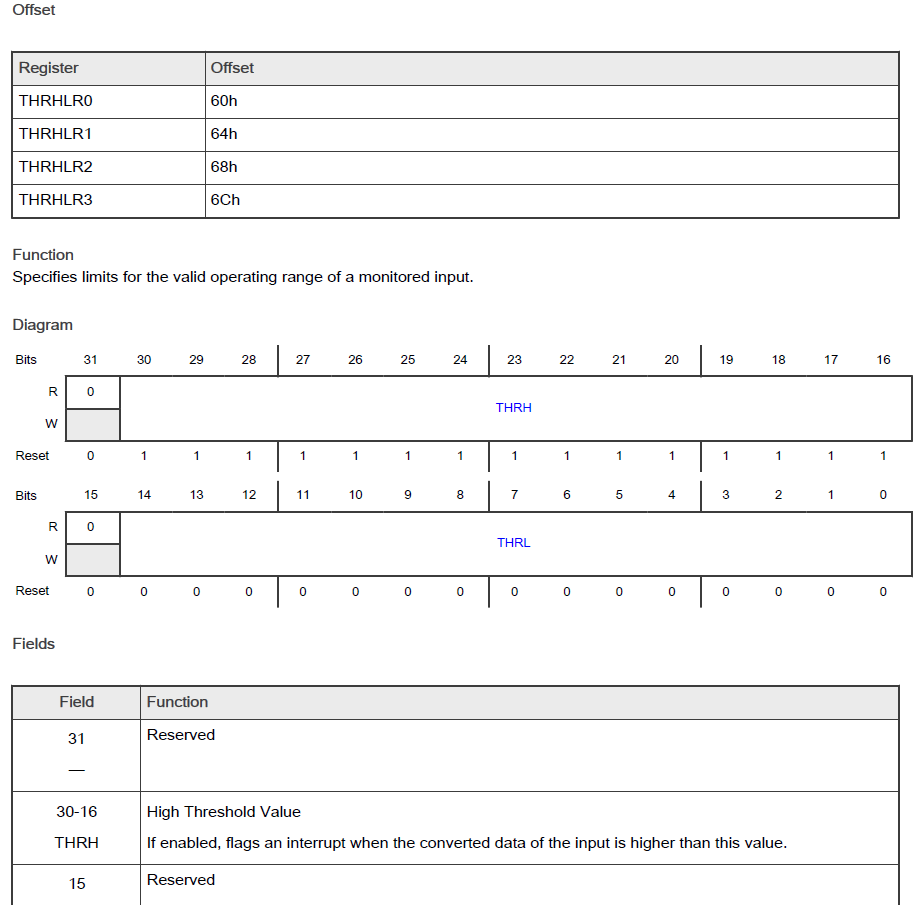

Analog Watchdog Threshold Values (THRHLR0 - THRHLR3)

THRH:如果启用,当输入的转换数据高于此值时标记中断。

THRL:如果启用,当输入的转换数据低于此值时标记中断。

Presampling Control (PSCR)

配置ADC在实际输入转换前预采样一个内部电压。

PREVAL2:选择外部输入预采样的内部电压。0b - VREFL 1b - VREFH

PREVAL1:为标准输入和温度传感器选择预采样的内部电压。0b - VREF 1b - VREFH

PREVAL0:选择为精密输入预采样的内部电压。0b - VREF 1b - VREFH

PRECONV:指定是否在进行预采样后进行比较。如果启用,则预采样之后进行转换,并将结果写入所选输入的转换数据寄存器。

Presampling Enable For Precision Inputs (PSR0)

PRESn:为精确输入n启用预采样。

Presampling Enable For Standard Inputs (PSR1)

Conversion Timing For Precision Inputs (CTR0)

根据转换时钟周期的数量,指定精确输入采样的持续时间。

转换时钟频率取决于MCR[ADCLKSEL]的配置。

INPSAMP:以转换时钟周期为单位指定采样持续时间。最小值为8。指定较低的值会自动强制设置为8。

Conversion Timing For Standard Inputs (CTR1)

TSENSOR_SEL:选择外部温度传感器的电压(如果可用)。如果有温度传感器可用,该字段可以用作两个温度传感器之间的mux的选择器。当有多个温度传感器时,该字段才适用

Normal Conversion Enable For Precision Inputs (NCMR0)

选择正常转换的高精度输入通道

NCMR1,2类似,一个是标准输入,一个是外部输入

Injected Conversion Enable For Precision Inputs (JCMR0)

选择注入转换的高精度输入通道。

和上面的NCMR0类似

Delay Start Of Data Conversion (DSDR)

数据转换延迟

Power Down Exit Delay (PDEDR)

下电退出延迟

Precision Input n Conversion Data (PCDR0 - PCDR7)

高精度通道0-7的转换数据

VALID:转换数据有效性。数据读取之后自动变为0

OVERW:指示以前的转换数据是否在未被读取的情况下被覆盖,在这种情况下,被覆盖的数据将丢失。

RESULT:转换数据类型,指示是由何种方式触发的转换

CDATA:转换数据,数据长度一直是15bit,与转换精度无关,转换精度只影响最终结果和转换时间,右对齐时选择bits [14:0],左对齐时选择bits [15:1]

Standard Input n Conversion Data (ICDR0 - ICDR23)

和上面类似,只是通道为标准输入通道

External Input n Conversion Data (ECDR0 - ECDR31)

和上面类似,只是通道为扩展输入通道

ADC2不支持扩展

Channel Analog Watchdog Select For Precision Inputs (CWSELRPI0)

选择模拟看门狗门限寄存器(THRHLR),提供监控高精度输入的限制。

Channel Analog Watchdog Select For Standard Inputs (CWSELRSI0)

选择模拟看门狗门限寄存器(THRHLR),提供监控标准输入的限制。通道0-7

Channel Analog Watchdog Select For Standard Inputs (CWSELRSI1)

选择模拟看门狗门限寄存器(THRHLR),提供监控标准输入的限制。通道8-15

Channel Analog Watchdog Select For Standard Inputs (CWSELRSI2)

这个应该是没有的,手册中的可能是预留

Channel Analog Watchdog Select For External inputs (CWSELREI0)

选择模拟看门狗门限寄存器(THRHLR),提供监控扩展输入的限制。通道0-7

Channel Analog Watchdog Select For External inputs (CWSELREI1)

选择模拟看门狗门限寄存器(THRHLR),提供监控扩展输入的限制。通道8-15

CWSELREI2对应通道16-23,CWSELREI3对应通道24-31

Channel Watchdog Enable For Precision Inputs (CWENR0)

为每个高精度通道使能模拟看门狗

CWENR1,CWENR2和上面类似,一个是标准输入,一个是扩展输入

Analog Watchdog Out Of Range For Precision Inputs (AWORR0)

显示高精度输入模拟看门狗比较的状态。

AWOR_CH7:读取时,0转换结果在限制范围内,1转换结果超出限制

写入1时清除标志

AWORR1显示标准输入模拟看门狗比较的状态,AWORR2显示扩展输入模拟看门狗比较的状态

Analog Miscellaneous In/Out register (AMSIO)

配置SAR算法比较步长。如果你想要进行高速校准或高速转换(见表298),你必须将3d写入HSEN。该寄存器中的所有其他值必须保持其重置值,并且不能写入。

HSEN:设置时启用高速转换或校准。所有其他位必须始终保持其重置值。

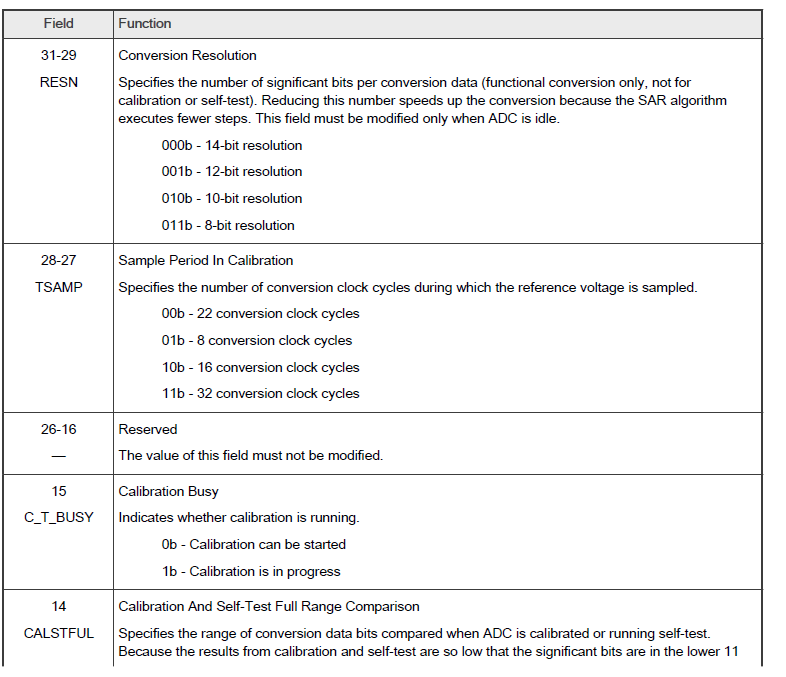

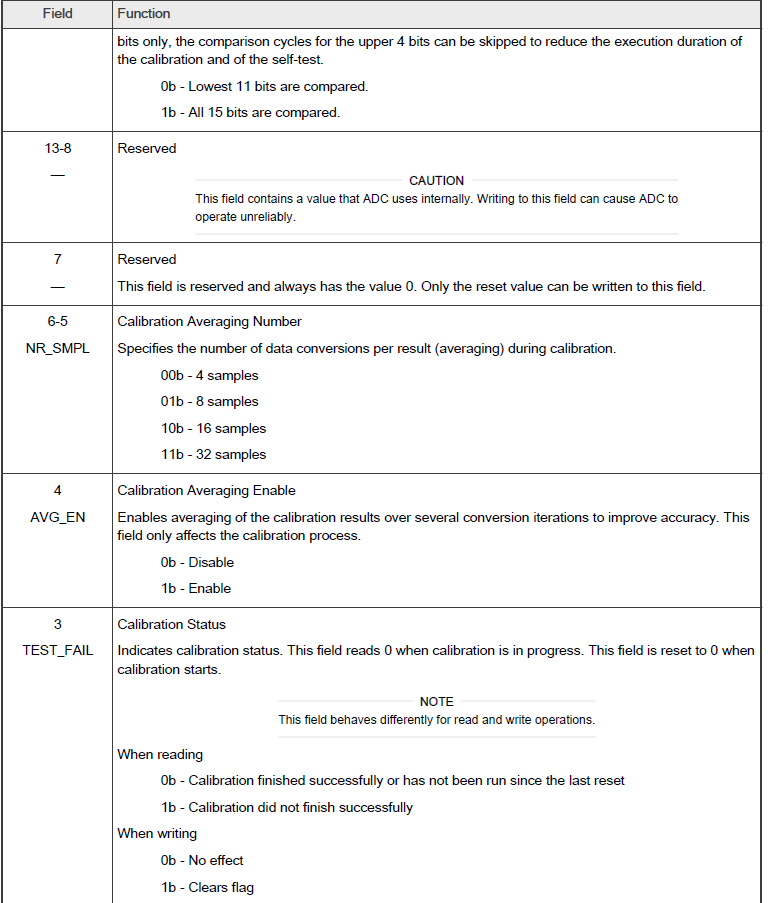

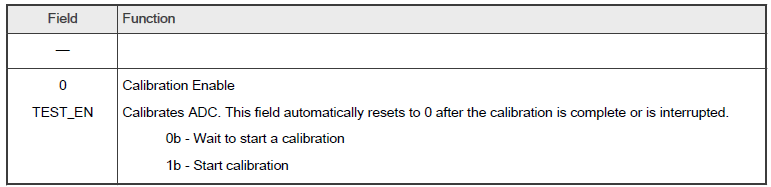

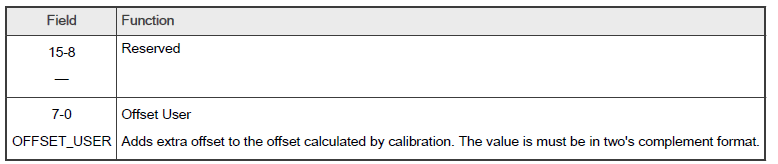

Control And Calibration Status (CALBISTREG)

控制多个ADC功能,用于数据转换、校准和校准状态。

RESN:指定每个转换数据的有效位数(仅用于功能转换,不用于校准或自检)。减少这个数字可以加快转换速度,因为SAR算法执行的步骤更少。

TSAMP:指定基准电压采样期间的转换时钟周期数。

C_T_BUSY:指示校准是否正在执行

CALSTFUL:指定ADC校准或运行自检时比较的转换数据位的范围。由于校准和自检结果较低,有效位仅在较低的11位,因此可以跳过较高4位的比较周期,以减少校准和自检的执行时间。

NR_SMPL:指定校准期间每个结果(平均)的数据转换数。

AVG_EN:是否启用校准平均功能

TEST_FAIL:表示校准状态。当校准正在进行时,该字段读数为0。当开始校准时,该字段被重置为0。

TEST_EN:校准ADC。在校准完成或中断后,该字段自动重置为0。

Offset And Gain User (OFSGNUSR)

指定SAR算法使用的用户配置的偏移和增益值。这些值必须以2的补码格式,可以是正的也可以是负的。

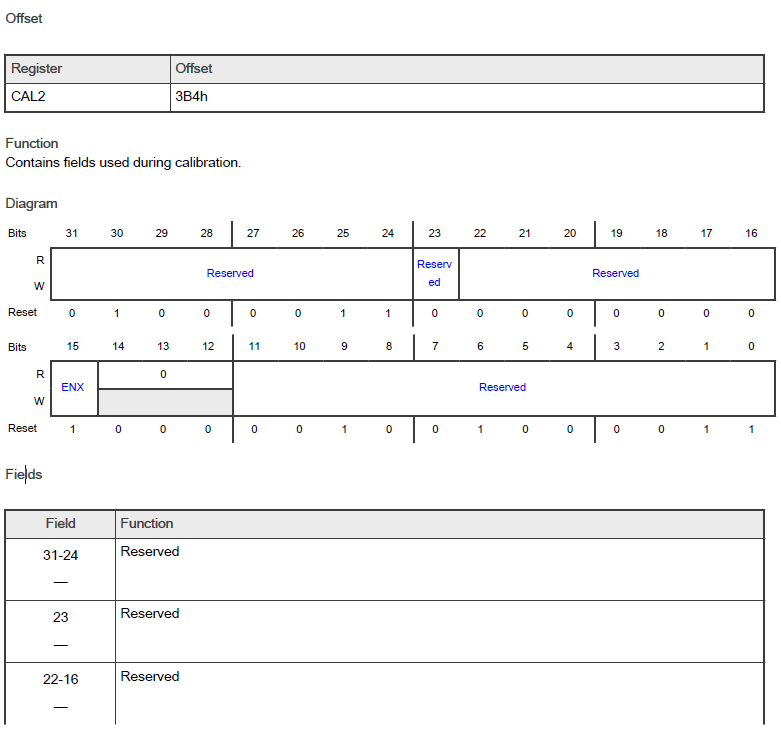

Calibration Value 2 (CAL2)

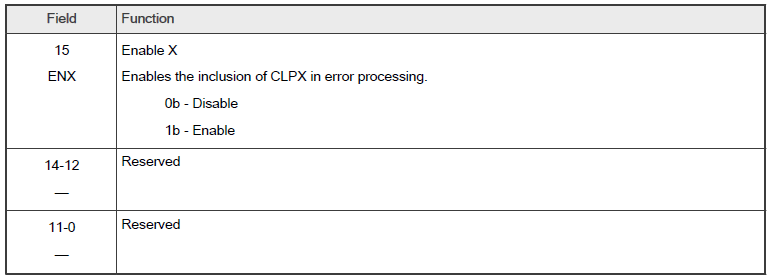

ENX:允许在错误处理中包含CLPX。

本文详细介绍了S32K324芯片的ADC功能。该芯片最多有3个ADC实例,通道分3组。阐述了用于内部供应监控的ANAMUX、BCTU接口、硬件触发等内容,还介绍了ADC的功能框图、特点、时钟、转换等方面,以及各寄存器的定义和作用。

本文详细介绍了S32K324芯片的ADC功能。该芯片最多有3个ADC实例,通道分3组。阐述了用于内部供应监控的ANAMUX、BCTU接口、硬件触发等内容,还介绍了ADC的功能框图、特点、时钟、转换等方面,以及各寄存器的定义和作用。

1301

1301

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?