目的

之前有使用过除法器,但感觉对生成ip配置还是很多不理解地方,于是阅读了Xlinx 除法器IP PG151中部分内容,记录备忘。

内容

1. 三种算法LutMult,Radix2,HighRadix 区别

方法对比

| 方法 | 建议操作数位宽 | 吞吐率 clocks per division | 描述 | 主要资源 |

| LUTMult | <=12bit | 1 | 把分母倒数用查找表存储起来,然后用乘加实现。适用小数据。 | DSP+BRAM |

| Radix2 | <= 16bits | >= 1 | 用加减法一个周期一个周期的计算商。类似于列式计算。只有它可以设置吞吐量(clocks per division,也就是几个周期计算一次) | Reg+LUT |

| High radix | >16bit | ≤1/N | 适用大数据。 对商的多个bit运算,好像也是先预估分母倒数大小(pre scale),然后用它和分子相乘(用到DSP),迭代N次计算这个过程。同时会有校正算法(因为预估的倒数可能不准)。 | DSP+BRAM |

LutMult 限制被除数和除数总位宽23bit。

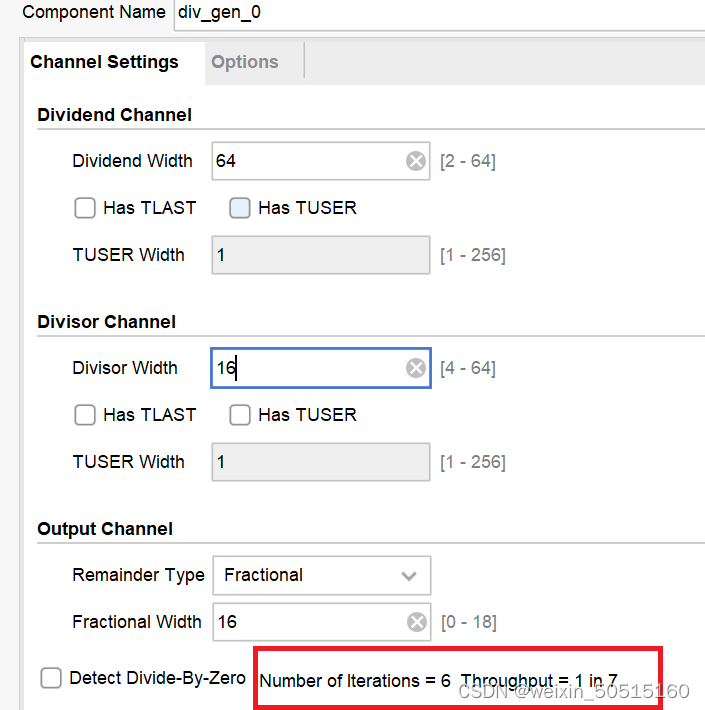

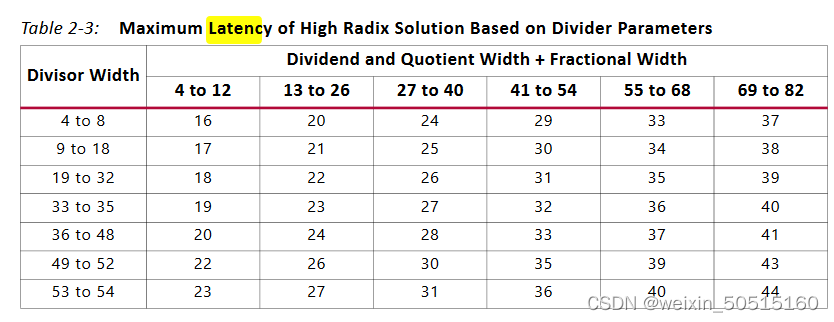

HighRadix算法的吞吐率和迭代次数N在VIVADO 19.1中截图如下。

2. 余数模式,小数模式,有符号运算原理。

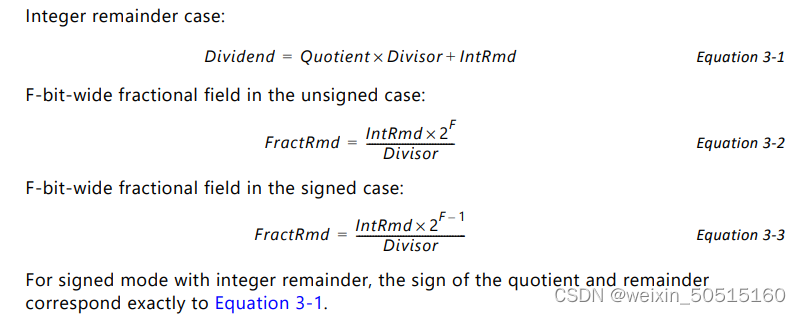

原理如下,小数模式相当于把余数模式的余数扩大后,再运算一次。

(1)商(quotient)和被除数(dividend)位宽相同。

(2)余数(remainder)和除数(divisor)位宽相同。

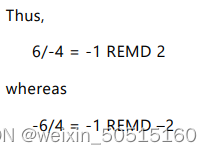

(3)有符号+余数模式,余数符号和被除数一致。例子截图如下图。

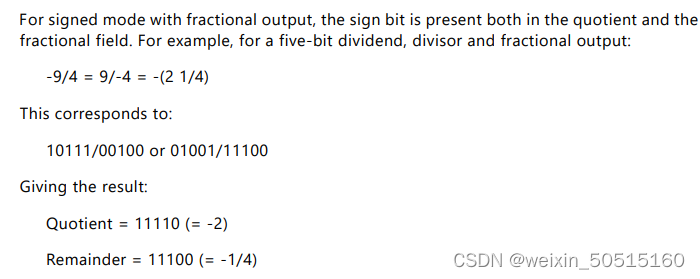

(4)有符号+小数模式,商和小数都保留符号位,例子截图如下。

3. 阻塞模式(Blocking Mode)和非阻塞模式(Non Blocking Mode)

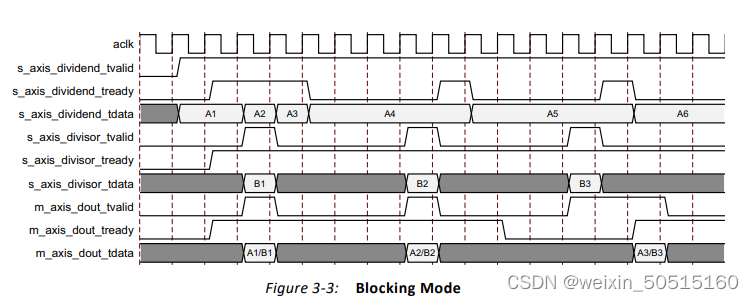

阻塞模式:除数和被除数可分时有效,也就是可以分时钟给。输入的被除数和除数同时受到valid,ready信号控制和握手。参考下图。

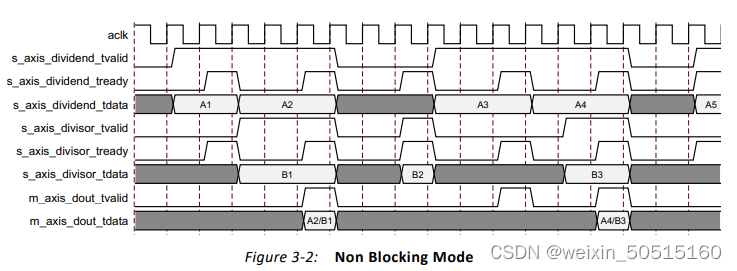

非阻塞模式:除数和被除数需要同时有效。输入的被除数和除数同时受到valid,ready信号控制和握手。

4. TUSER和TLAST

个人理解:两者除法器本身作用不是很大,可以用来旁路一些数据。

(1)TUSER 位宽可以自定义,用来传输一些用户想要传输的数据,延时和除法器计算延时相同。

(2)如果打开了Divide_by_zero detect功能(也就是分母=0),则TUSER 的bit 0 固定传输除0标志位。分母为零时候计算结果是不确定的。

(3)TLAST是AXI协议中内容,表示最后一个块(last block)数据,在除法计算本身好像也没什么用。1 bit宽度。

可以把除数和被除数的TLAST逻辑运算后输出,如”与“,”或“。

4. 输入数据(除数和被输出)位宽

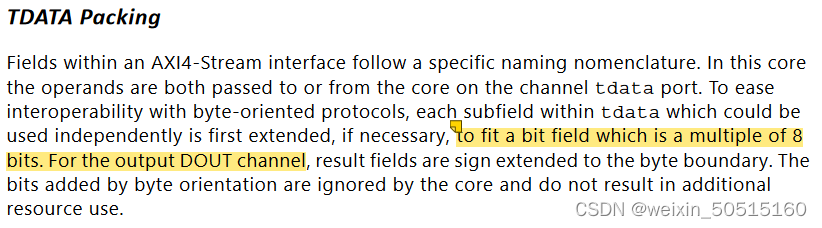

可以设置任意位宽,但由于AXI4总线原因,接口中会扩展为8bit位宽,我理解会影响例化那里的端口位宽,实际除法核心部分和用户设定的位宽一致的。

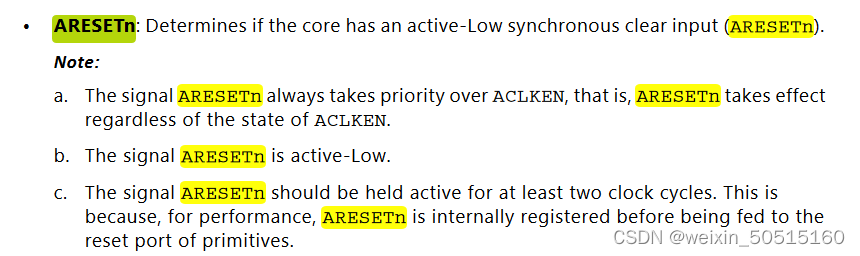

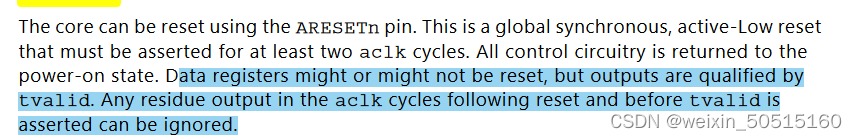

5. 复位ARSTn

默认内部复位,同步低电平复位,可以打开,至少需要两个时钟(aclks)周期。

实际输出结果以tvalid握手信号为准,避免出现有些寄存器没有完全reset情况。

6. 延时

(1)LutMult 固定为8T

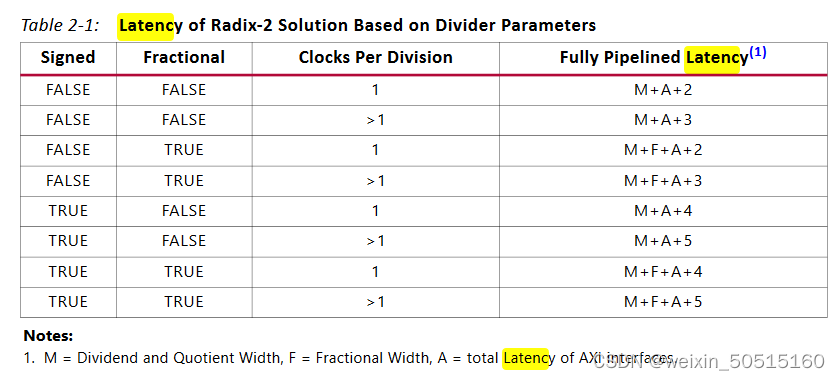

(2) Radix2

手动延时:吞吐率=1时候可以设置延时,吞吐率是指每个时钟计算几次(clocks per division)。

自动延时:延时计算如下图,这时候为延时最大值。如果时钟不是很高,可以设定为手动模式,适当调低此值,减少资源消耗。

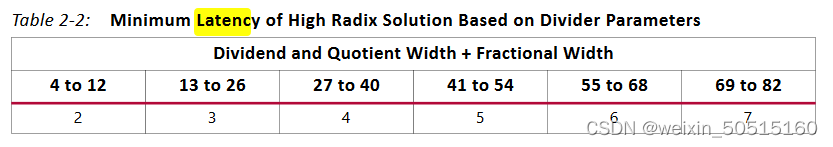

(3) HighRadix

非阻塞模式的最小延时计算如下。也就是被除数(dividend)位宽+小数(fractional)位宽。

非阻塞模式最大延时如下图。

阻塞模式下,需要在上面基础上附加延时。

| 模式 | 附加延时 |

| 阻塞 无tready输出 | +1 |

| 阻塞 有tready输出 | + 3 |

参考资料

Divider Generator v5.1 Product Guide (PG151)

pg151-div-gen.pdf • Viewer • AMD Adaptive Computing Documentation Portal (xilinx.com)

7411

7411

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?