RiscV实现教程

参考来源

tinyriscv: https://gitee.com/liangkangnan/tinyriscv

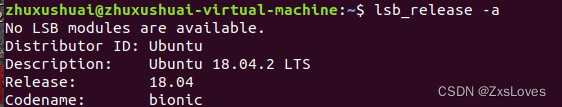

平台实现 : Linux ubuntu 实现介绍

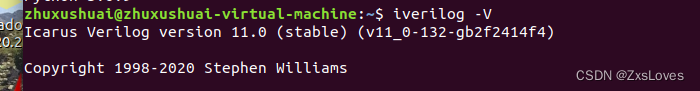

环境 : 需要 iverilog (切换到 v11或以上的版本)

1.下载iverilog源码

git clone https://github.com/steveicarus/iverilog.git

2.切换到v11分支(必须用V11或以上的版本)

git checkout v11-branch

3.安装依赖

sudo apt-get install autoconf gperf flex bison build-essential

4.编译、安装iverilog和vvp

sh autoconf.sh

./configure

make

make i

nstall

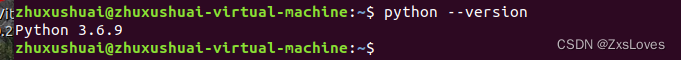

5.创建python软链接

sudo ln -s /usr/bin/python3.8 /usr/bin/python

其中/usr/bin/python3.8对应你实际安装的python版本。

这是大概的环境实现教程 我记得在 python 软连接上面需要注意 ,我pyhton下载的有 2 3 版本,但是内部链接的是2 所以 需要先进入 管理员模式把 python 2 的软连接删除再进行 重新链接新的3系列软连接

注意!!! 一定要确认python 软连接是否正确 不然会在下面的验证中出错

6.安装gtkwave

sudo apt-get install gtkwave

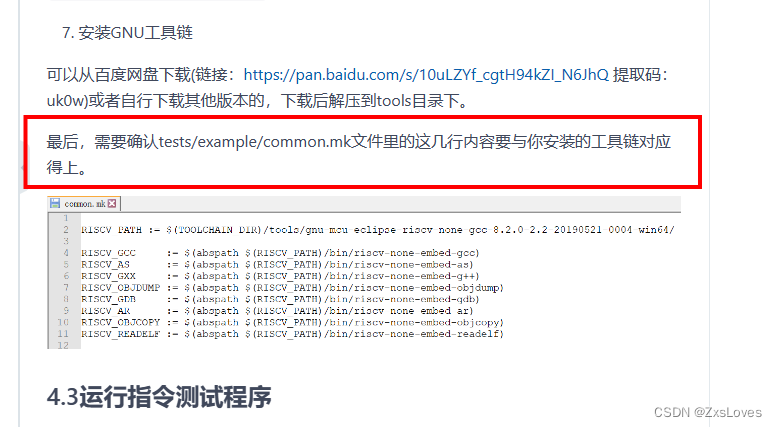

7.安装GNU工具链

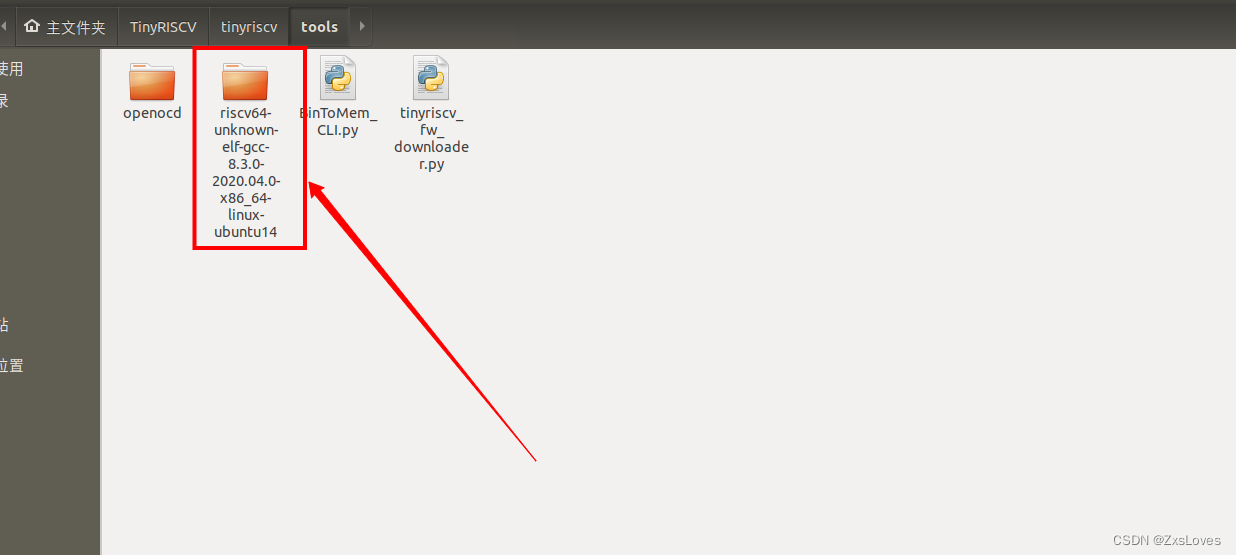

可以从百度网盘下载(链接:https://pan.baidu.com/s/10uLZYf_cgtH94kZI_N6JhQ 提取码:uk0w)或者自行下载其他版本的,下载后解压到tools目录下。

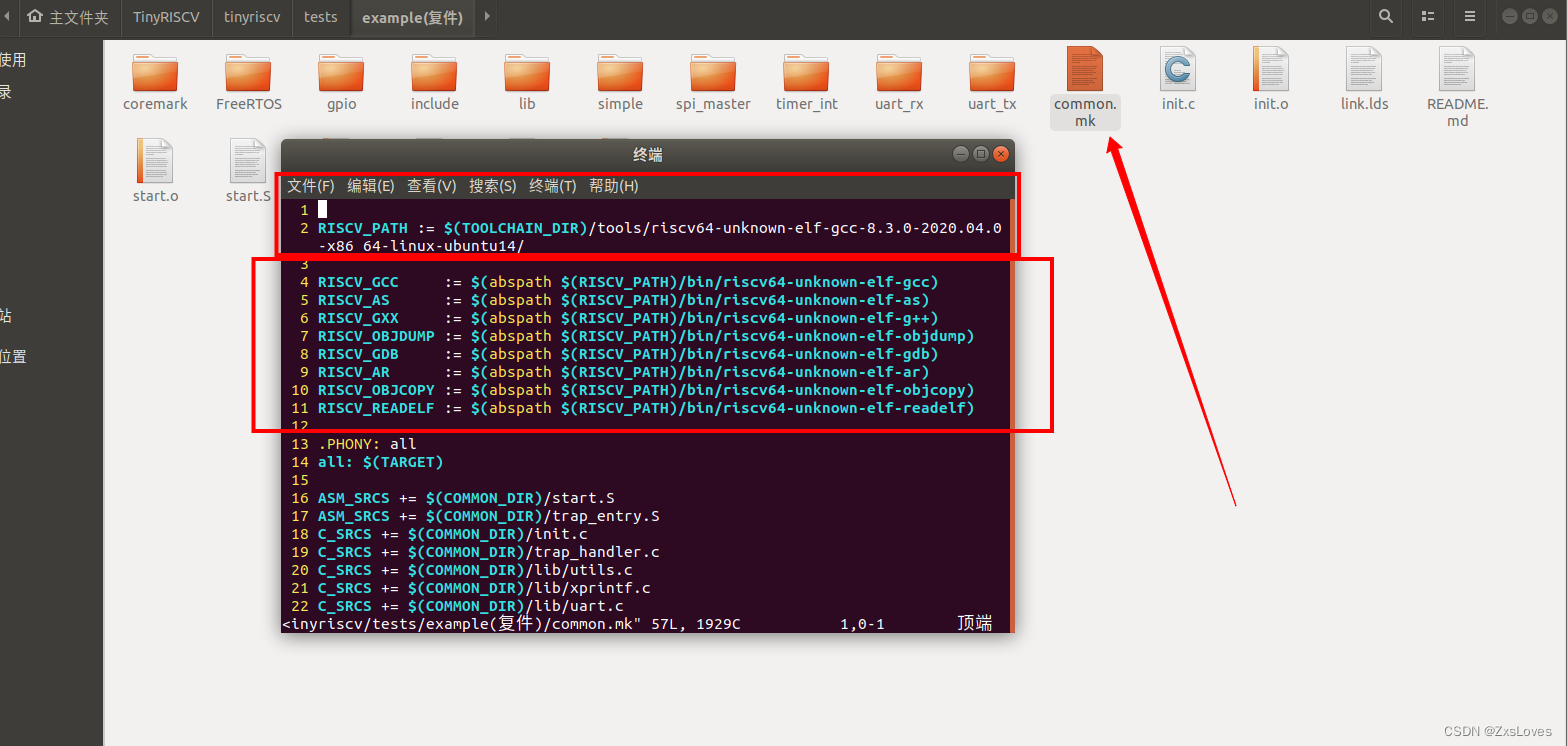

最后,需要确认tests/example/common.mk文件里的这几行内容要与你安装的工具链对应得上。

我建议是百度网盘下载 嘿嘿

然后用git把工程拉近linux 下 git clone https://gitee.com/liangkangnan/tinyriscv.git

进入之后,进入文件夹的sim下列

在终端执行 python .\sim_new_nowave.py ..\tests\isa\generated\rv32ui-p-add.bin inst.data

会出现大大的pass

指令的全部测试 输入 python ./test_all_isa.py

下面进入 C语言的运行

进入 tests\example 下的文件夹 的simple

其实后面的gpio uart_rx uart_tx 都是写好的c程序 这次我们在linux上只实现 simple 的测试

因为已经有Makefile文件了 我们现在进入 在终端输入make 发现可能会报错

是因为

第一行是我们把下载的工具链放在哪里了

后面是修改工具链的来源

1

2 RISCV_PATH := $(TOOLCHAIN_DIR)/tools/riscv64-unknown-elf-gcc-8.3.0-2020.04.0 -x86_64-linux-ubuntu14/

3

4 RISCV_GCC := $(abspath $(RISCV_PATH)/bin/riscv64-unknown-elf-gcc)

5 RISCV_AS := $(abspath $(RISCV_PATH)/bin/riscv64-unknown-elf-as)

6 RISCV_GXX := $(abspath $(RISCV_PATH)</

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2618

2618

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?