标准单元设计

一个数字标准单元是一个有固定尺寸和功能的预定义模块。

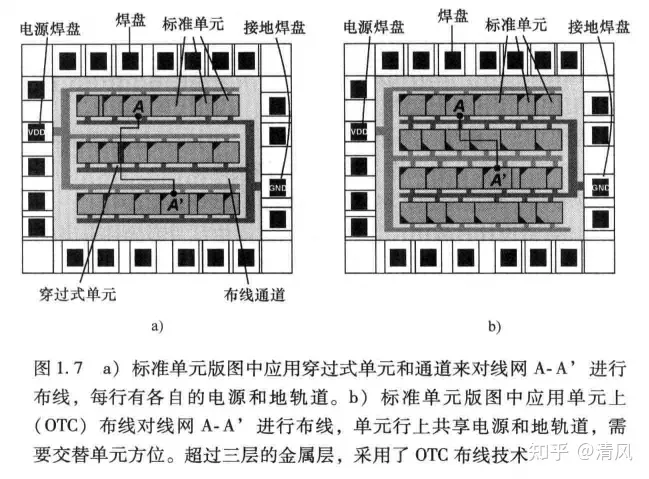

在标准单元版图设计中,所有的单元按行排列,电源和地网在水平方向上分布邻接,单元的信号端口可能在单元边界的“上方”或者“下方”,又或者分布在整个单元区域。因为标准单元布局的自由度较少,所以其复杂度大大降低,这样的设计可以大大减少上市时间。

标准单元行之间的布线使用行内的穿过式单元或者行之间可用的布线轨道。此外,由于芯片上晶体管数量的增多,标准单元行将的布线区域已变得不能满足设计需求,因此,单元上(OTC)布线越来越流行,采用多重金属层的方法。

宏单元

宏单元是典型的较大块逻辑,执行可重用的功能。宏单元范围从简单(一对标准单元)到高复杂(整个子电路达到嵌入式处理器或者存储模块级别)。

大多数情况下,宏单元可放置在版图区域中的任何位置,以达到布线距离或者电气性能的最优化。

门阵列

门阵列是具有标准逻辑功能的硅片,例如NAND和NOR,但是没有连接。单芯片指定的需求明确后,互联(布线)层会在后面添加上。

版图物理设计优化

物理设计是一个复杂的优化问题,他有几个不同的目标,例如最小芯片面积,最小线长和最少过孔。优化目标满足的程度,决定了版图的质量。

不同的优化目标可能难以在算法中捕获且可能互相冲突,然而,多目标的折中是将目标简化为一个目标函数,例如:

w1*A+w2*L

A是芯片面积,L是总线长; 和w1和w2 是表示A和L的相对重要性的权值。

在版图优化中,三类约束必须满足:

- 工艺约束,用于指导特定工艺节点的生产制造。包括最小版图宽度和在版图形状间的空间值。

- 电气约束,保证设计达到预期的电气行为。包括满足最大的时序约束,对于信号时延和在最大耦合电容下的滞留。

- 几何约束,为了减小设计过程的整体复杂度。包括在布线中使用优选布线方向和行间标准单元的布局。

2042

2042

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?