系列文章目录

前言

哈工大计组网课,教材是《计算机组成原理》(唐朔飞)

(三)定点运算

1.移位运算

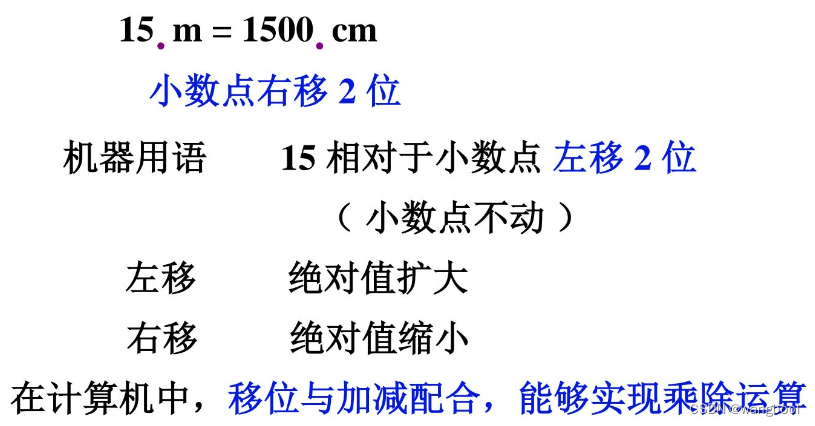

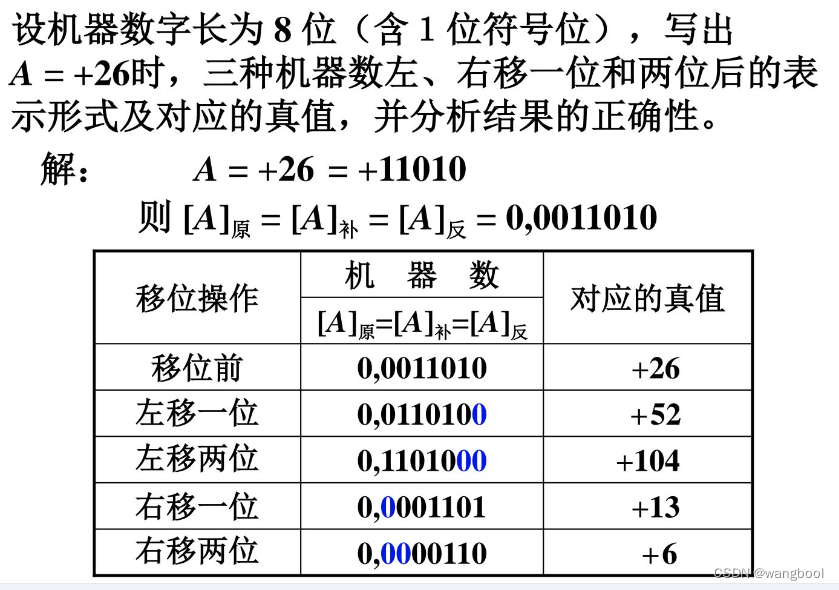

1.1.移位运算的数学意义

在计算机当中,数据的存储如果是二进制,二进制的数值相对于小数点左移一位,数值就变成的两倍,右移一位,则变成原来的二分之一。

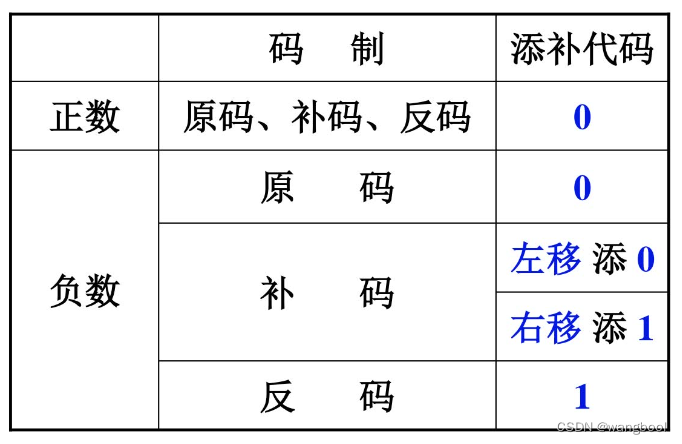

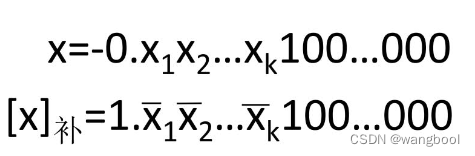

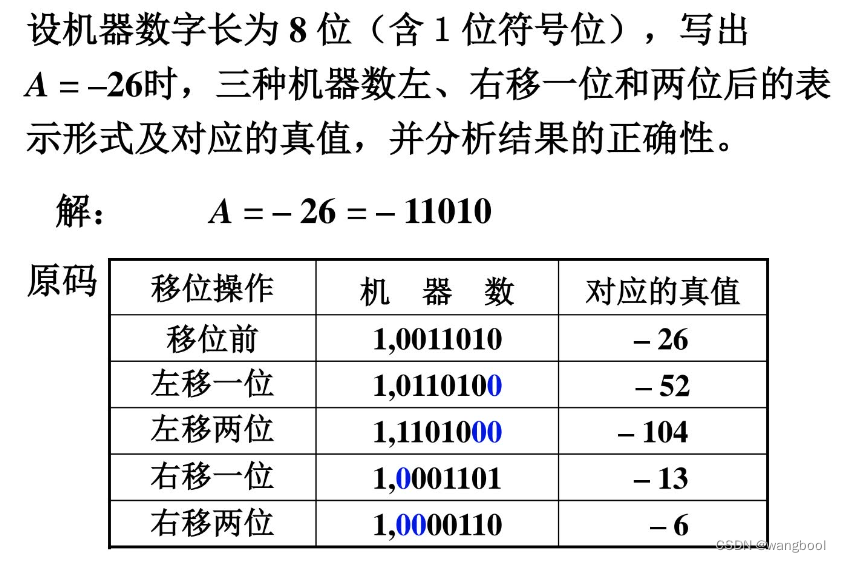

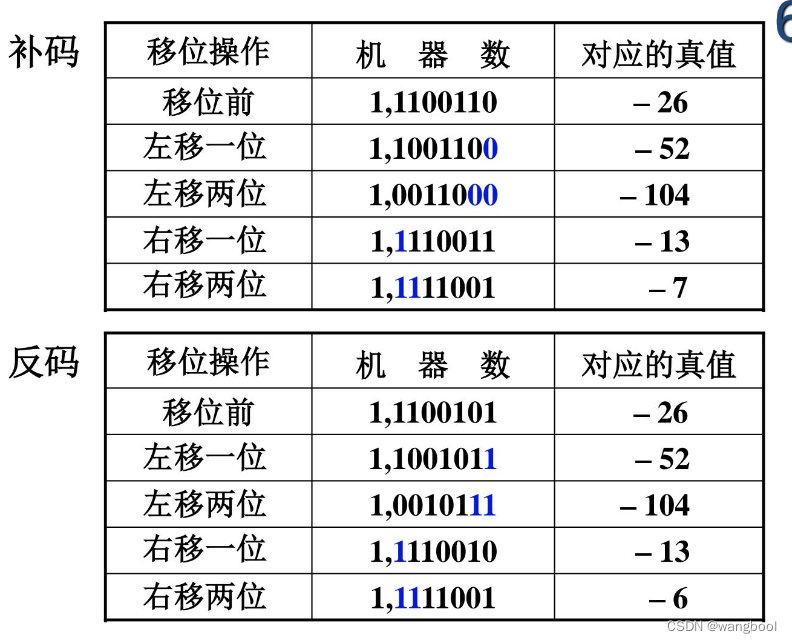

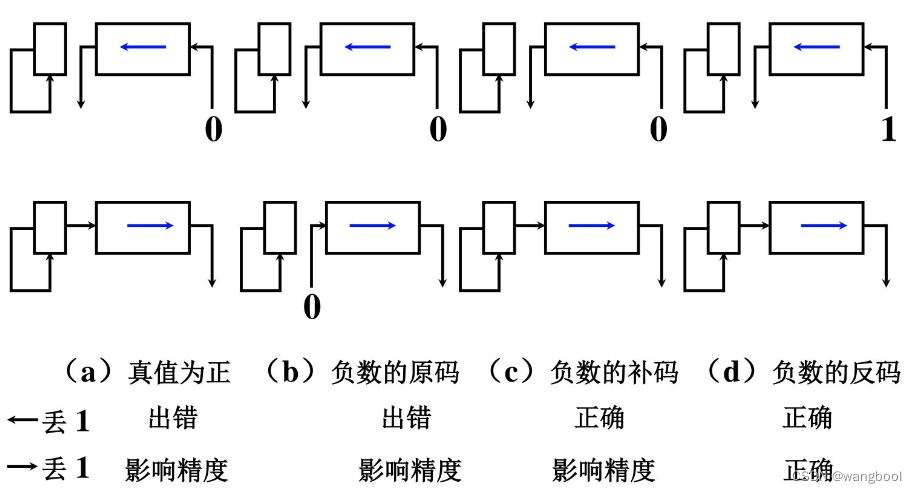

1.2.算术移位规则

符号位不变

1.3.算术移位的硬件实现

1.4.算术移位与逻辑移位的区别

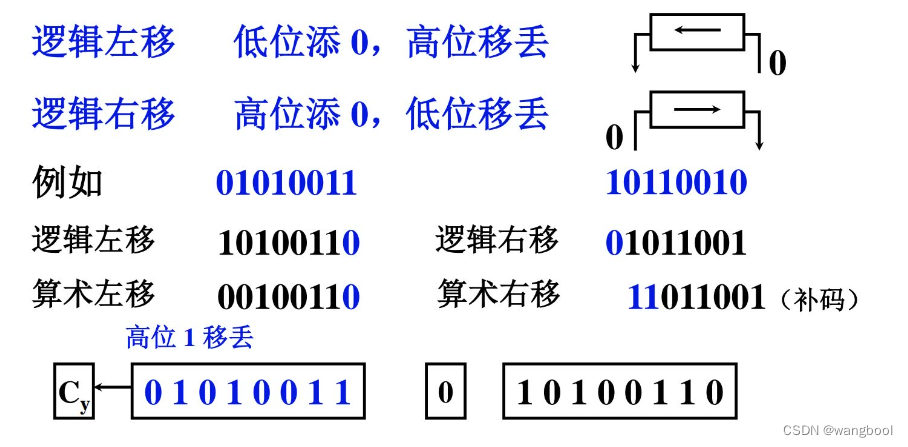

算术移位:符号不动,移动数值位,是有符号数的移位。

逻辑移位:无符号数移位,所有位都会参加移位运算。

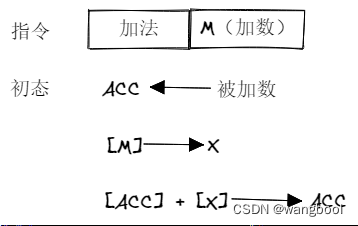

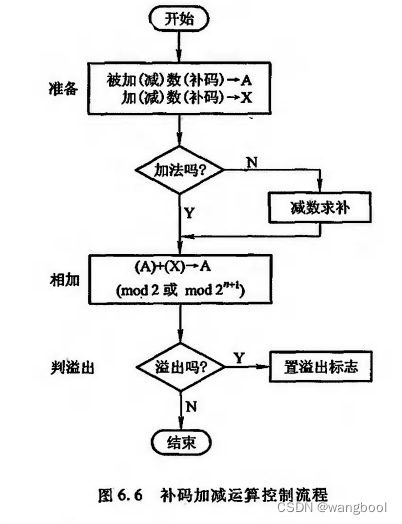

2.加减法运算

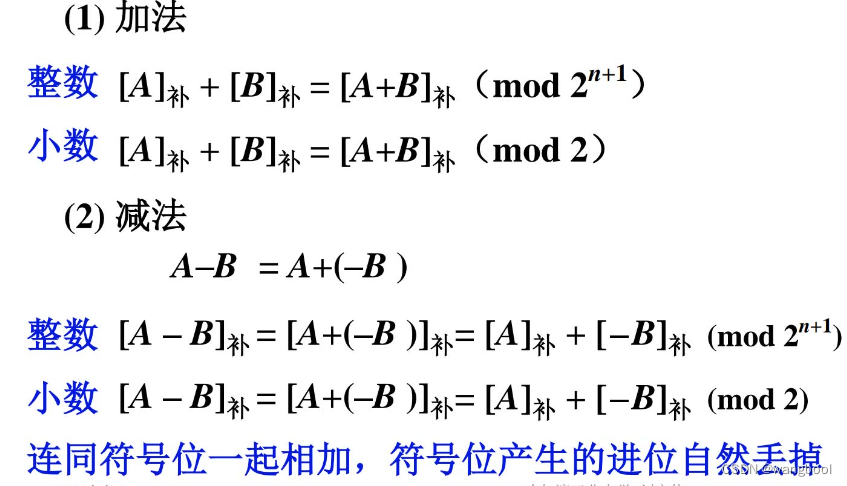

2.1.补码加减法运算的公式

称 [ − B ] 补 [-B]_补 [−B]补为“求补”后的减数

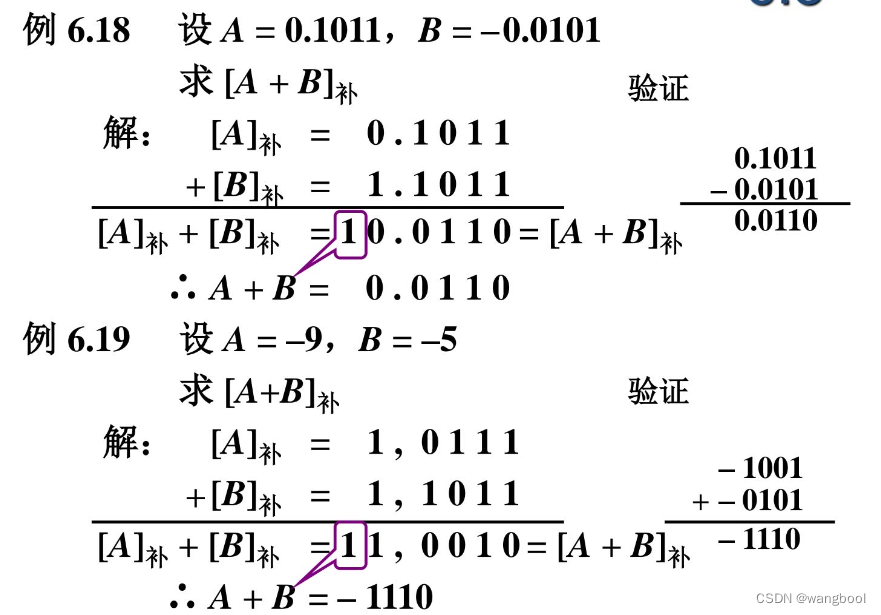

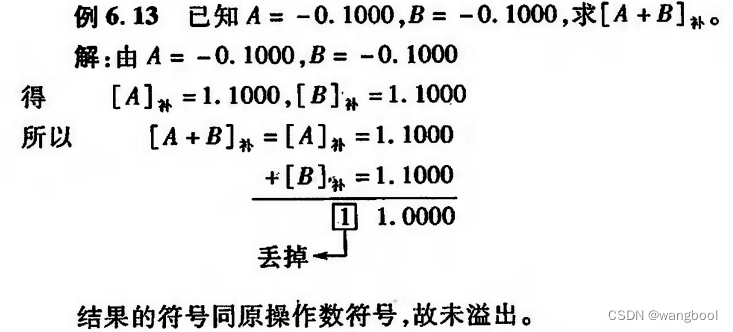

2.2.举例

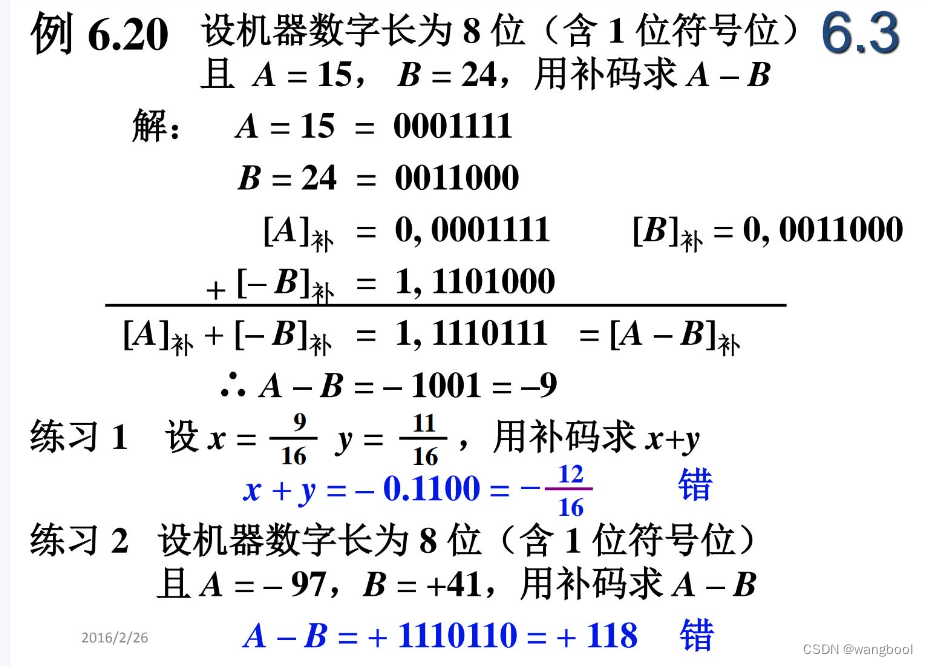

发生溢出后,答案出错。

2.3.溢出的判断

一个正数和一个负数进行加法运算,不可能发生溢出。

对于加法,只有正数加正数或者负数加负数才会溢出,对于减法,只有负数减正数,或者正数减负数才可能溢出。

一位符号位判溢出:参加操作(即加法)的两个数(减法时即为被减数和“求补”以后的减数)符号相同,其结果的符号与原操作的数的符号不同,即为溢出。

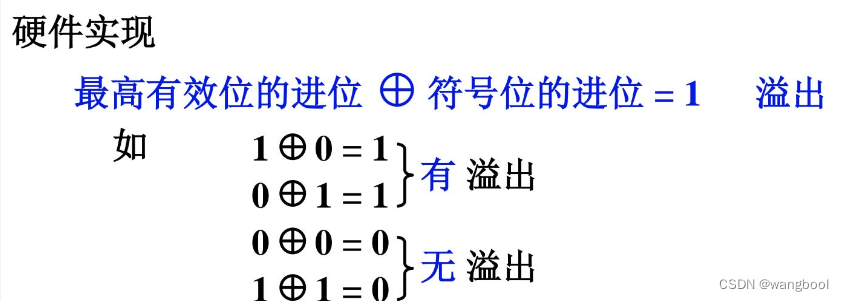

将最高有效位进位情况与符号位进位情况保存下来并送入一个异或器,1为有溢出,0为无溢出。

这里算出A+B=-1,只能根据补码的定义的公式算,因为原码不能表示-1,所以用补码算原码的公式算不出来。

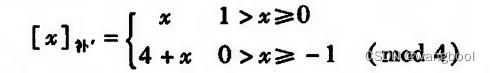

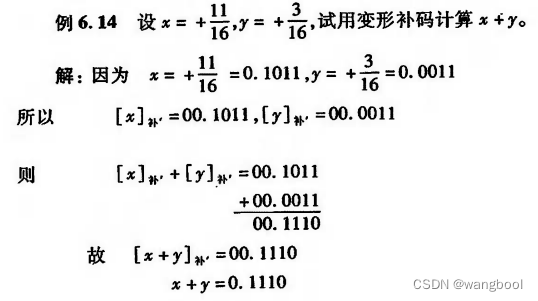

两个符号位判溢出(变形补码):在变形补码做加法时,两位符号位要连同数值部分一起参加运算,而且高位产生的进位自动丢失,即可得正确结果

[

x

]

补

′

+

[

y

]

补

′

=

[

x

+

y

]

补

′

(

m

o

d

4

)

[

x

]

补

′

+

[

−

y

]

补

′

=

[

x

−

y

]

补

′

(

m

o

d

4

)

[x]_{补'}+[y]_{补'} = {[x+y]_{补'}}\quad(mod 4)\\ [x]_{补'}+[-y]_{补'} = {[x-y]_{补'}}\quad(mod 4)

[x]补′+[y]补′=[x+y]补′(mod4)[x]补′+[−y]补′=[x−y]补′(mod4)

当两位符号不同时,表示溢出,否则无溢出。最高符号位代表了真正的符号位。

如果是整数,模就要变成

2

n

+

2

2^{n+2}

2n+2

推广:如果小数以2的k(k = 1、2、3…)次方为模,那么其补码形式的符号就占了k位。

如果整数以2的n+m(m = 1、2、3…)次方为模,那么其补码形式的符号就占了m位。

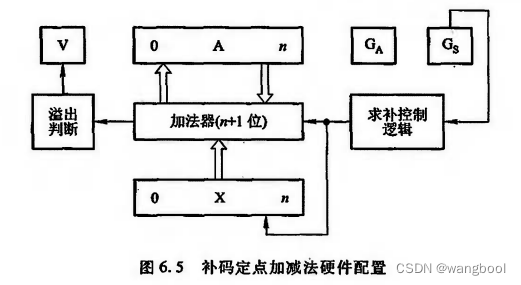

2.4.补码加减法的硬件配置

- A:ACC,保存的被加数,为n+1位。

- X:保存加数(如果是减法运算就是被减数)为n+1位。

- KaTeX parse error: Expected 'EOF', got '&' at position 4: G_A&̲G_S:两个标记,如果做加法 G A G_A GA置1,如果是减法, G S G_S GS置1,用 G S G_S GS控制求补逻辑。

- 求补控制逻辑: [ y ] 补 → [ − y ] 补 [y]_补\rightarrow {[-y]_补 } [y]补→[−y]补。完成了X中保存数据每位取反,然后实现了每位去取反。可以利用另一个加法器完成加1。

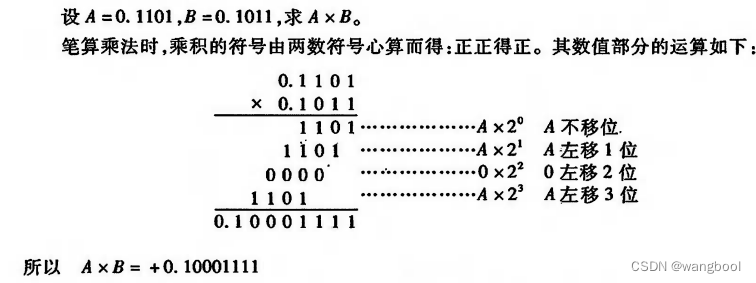

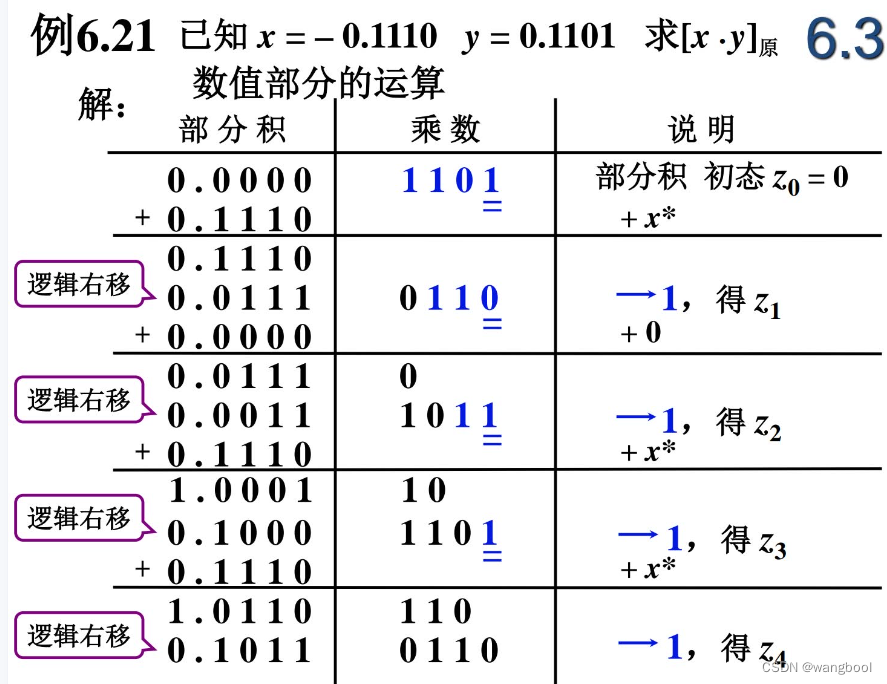

3.乘法运算

3.1.分析笔算乘法

符号位单独处理(心算求得)

乘数的某一位决定是否加被乘数

四个位积一起累加

乘数的位数扩大一倍

存在问题:四个位积一次相加,机器难以实现,位数增长了一倍,将会造成器材的浪费和运算时间的增加。

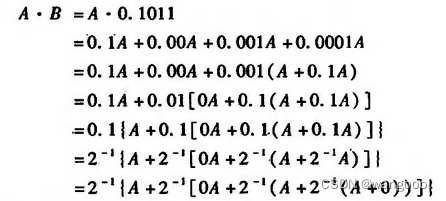

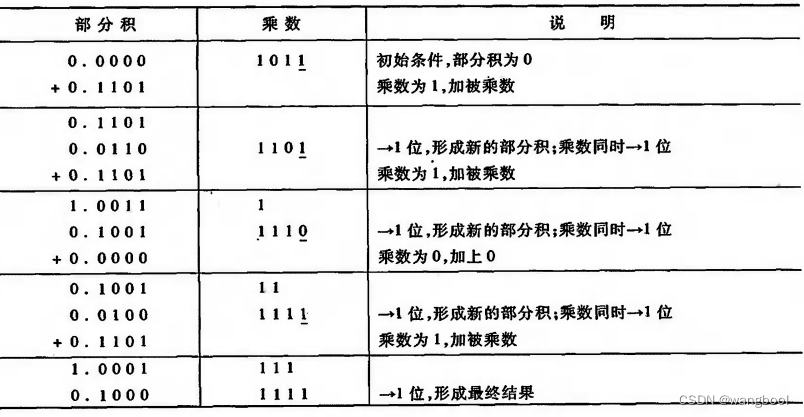

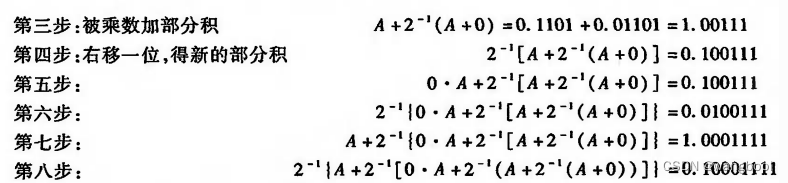

3.2.笔算乘法的改进

最里面的的0,是补进来的,表示进行加法操作的的时候,给出的累加和的初始值。

改进的区别:本来是位积不断左移

运算过程

符号位需要通过异或电路取得

- 乘法运算可用jia和移位实现,n = 4,加四次,移四次。

- 由乘数的末位决定被乘数是否与原部分积相加,然后右移1位形成新的部分积,同时乘数右移一位(末位移丢),空出高位存放部分积低位。

- 被乘数只与部分积高位相加

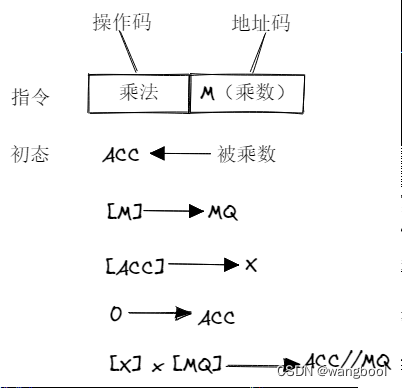

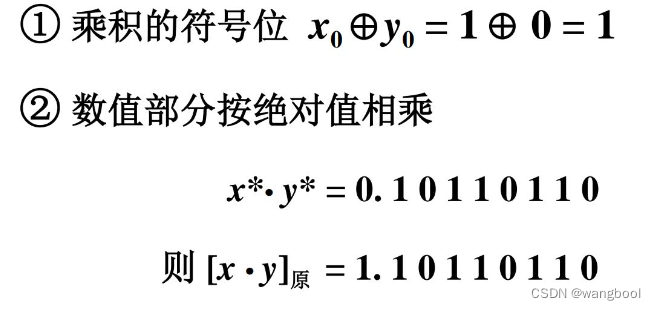

被乘数放在X寄存器当中,乘数放在乘商寄存器(MQ)当中,乘法的累加值的高位放在ACC中,ACC寄存器的值随着右移加长,低位被移到了MQ当中,MQ当中保存的乘数也在逐渐的进行右移,每一次移位操作,都会把运算过的最低位移丢,通过新的最低位判断是否需要加上被乘数。

被乘数只是和部分积的高位相加,即只和ACC保存的数据相加。

硬件上需要三个寄存器,其中两个要具有移位功能,一个用于保存被乘数(需要一直被保存),ACC保存乘积的高位,MQ存放乘积的低位和剩余的乘数。ACC、MQ需要具有移位功能,还需要一个全加器,实现被乘数和部分积的高位相加的操作,需要n+1位。

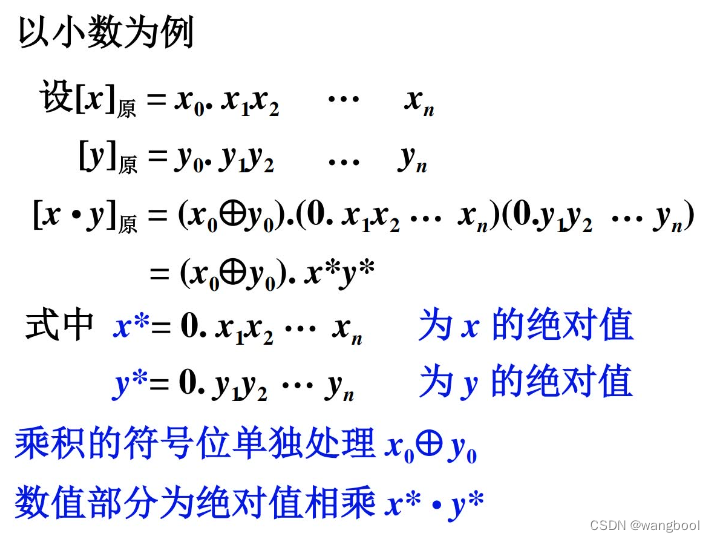

3.3.原码乘法

3.3.1.原码的一位乘运算规则

因为真值与原码表示只差一个符号,乘法的符号是由两个数的符号取异或得,是由之前讨论的乘法可直接用于原码一位乘。

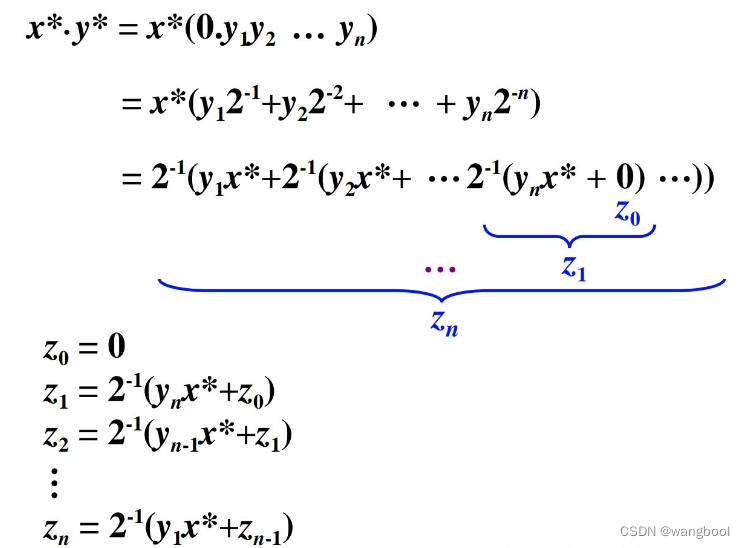

3.3.2.原码一位乘递推公式(类使笔算乘法得改进)

这里运算是绝对值的运算,所以是逻辑右移。

3.3.3.原码乘法特点

- 绝对值运算,逻辑移位

- 用移位的次数判断乘法是否结束(加法并不一定每次都运行,所以不用加法次数判断)

3.3.4.原码一位乘的硬件配置

- 计数器对移位次数进行计算。

- S是符号位,通过符号位取异或对S置值。

- 移位和加控制:负责移位控制和加法控制,由乘数的最低位来控制。

- 控制门:当乘数最低位的值是1的时候,控制门打开,被乘数通过控制门送到加法器与部分积的高位进行累加。如果最低位是0,控制门直接将0送到加法器中,或者不送入,直接由移动和加控制将Q中进行移位。

- G M G_M GM是乘法的标志。

- A、X、Q都是n+1位。

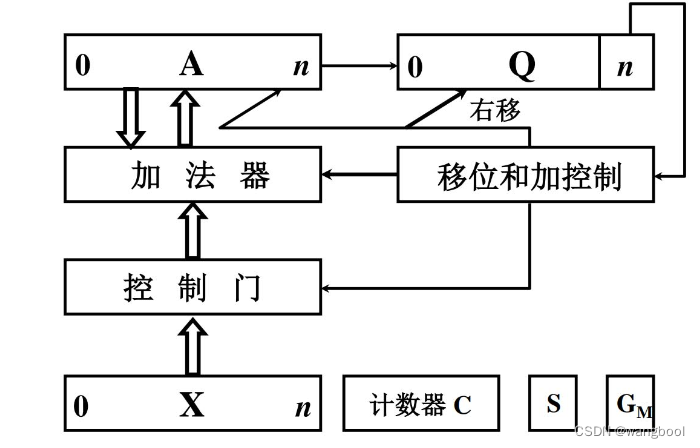

4.除法运算

4.1.分析笔算除法

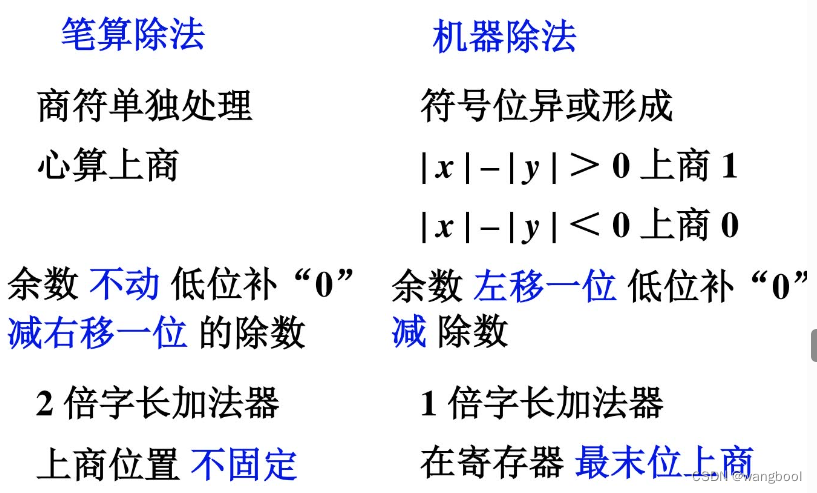

4.2.笔算除法与机器除法的比较

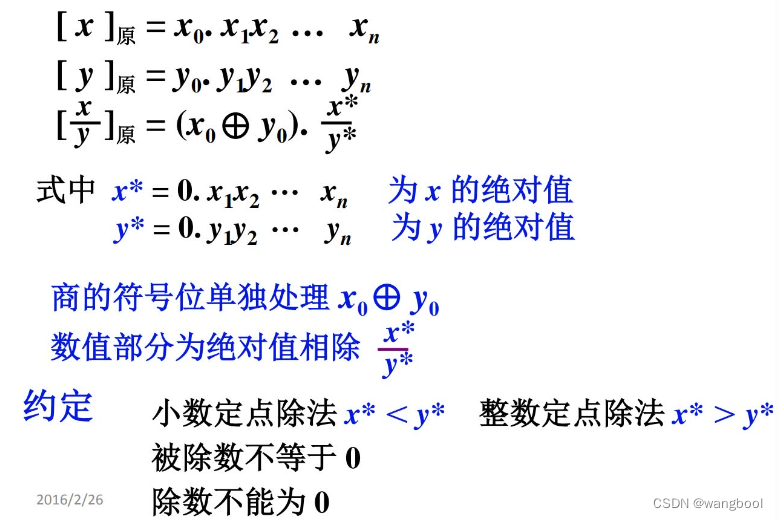

4.3.原码除法

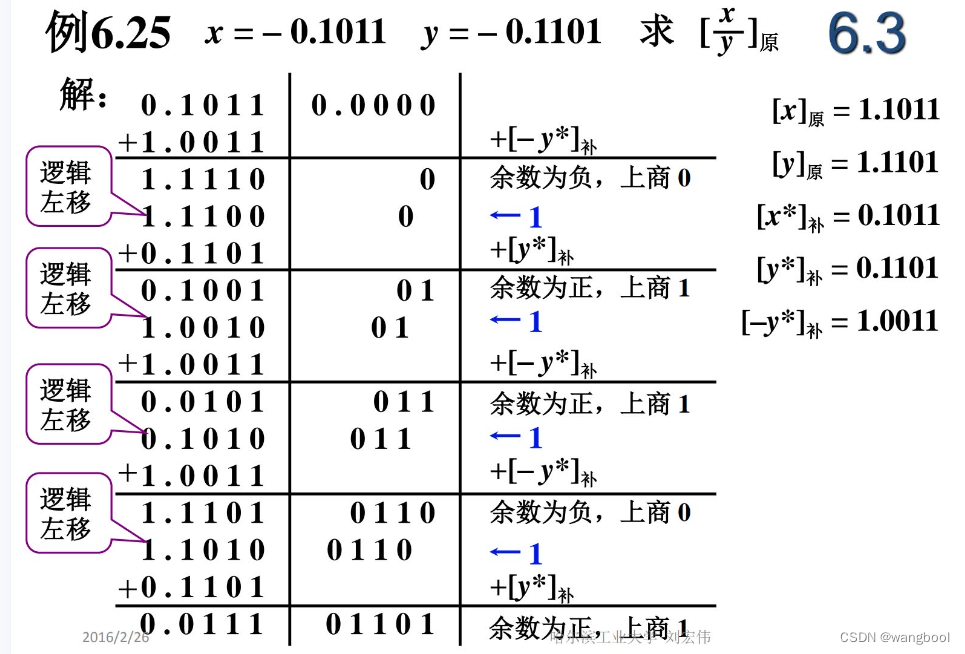

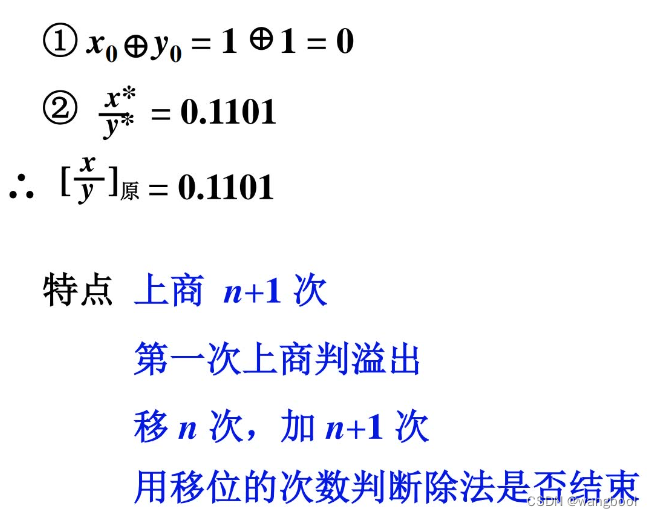

在小数定点机当中,如果被除数大于除数,即第一步的上商为1,计算结果就发生了溢出,此时停止计算并说明发出溢出。如果被除数为0,结果可以直接写0。

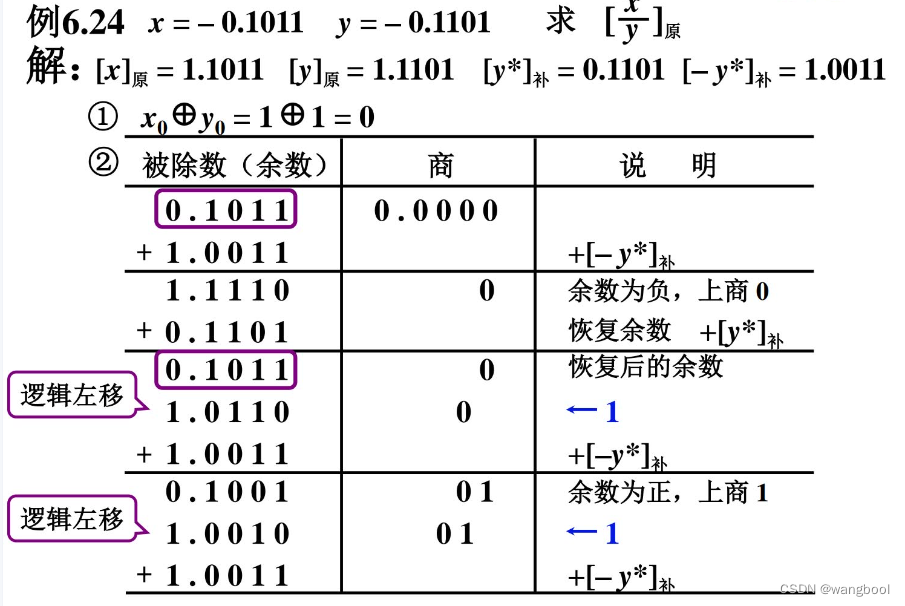

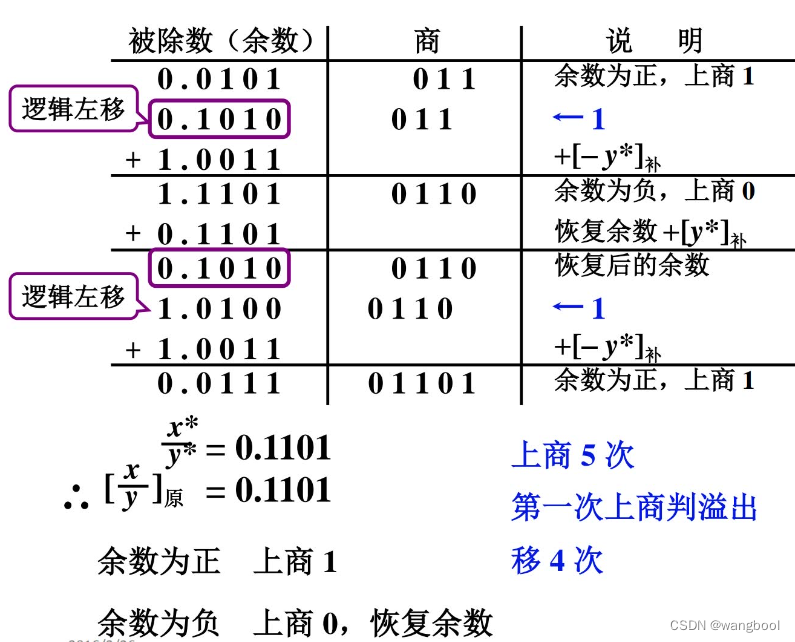

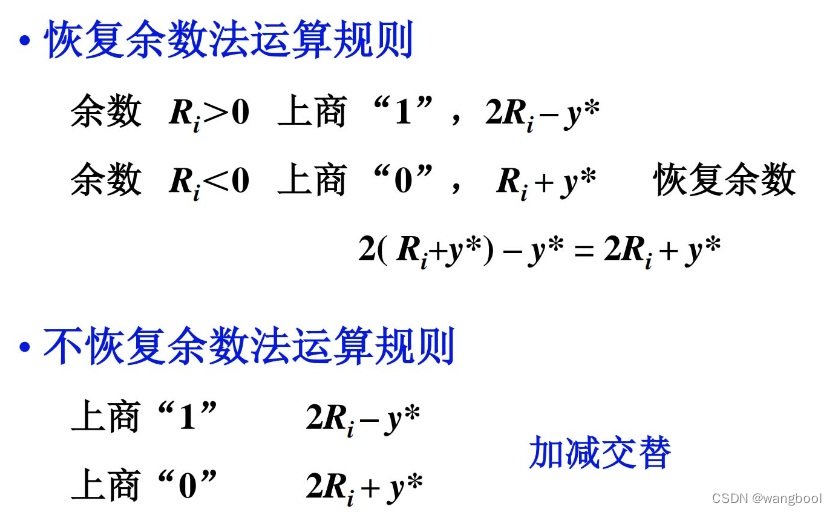

4.3.1.恢复余数法

做减法是为了算出上商取1还是0,如果结果(暂时的余数)为正,上商取1,结果为负,上商取0。如果上的商不是1,就说明此时减法操作不对,就要把剪掉除数之后的余数进行恢复,即又加上除数,回退到之前的被除数(即上上次操作产生的余数),然后对被除数逻辑左移一位(因为算的是绝对值),重新对新的被除数做减法操作。如果上的商是1,就说明此时减法正确,余数是真的余数,此时余数的直接左移一位,作为被除数参与下一次减法操作。

4.3.2.不恢复余数法

- 第一步依然要对除数做减操作,因为此时没有上商,无法判断加/减操作,直接做减操作判断是否溢出。

- 如果未溢出,此时上商为0,对余数进行 2 R i + y ∗ 2R_i+y^* 2Ri+y∗(左移一位加上除数,或者说恢复余数后左移一位再减去除数)的操作,产生新的余数(下次一操作的被减数)

- 每一次上商就是做一次加法操作。

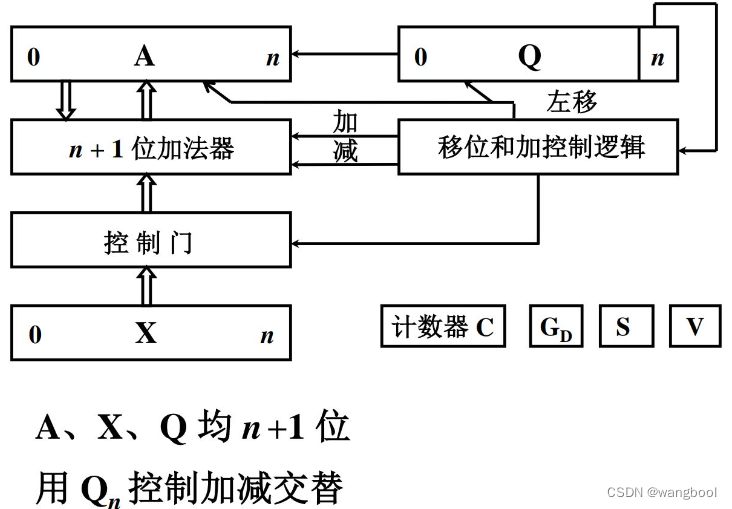

4.3.3.原码加减交替除法硬件配置

- ACC:保存被除数和余数,X保存除数,Q保存商,由上一次上商的值来决定下一次ACC和Q一次左移后是加上除数,还是加上除数的负的补码。

- 通过移位和加控制逻辑控制加法器做加法操作或减法操作。

- 计数器C:用移位的次数作为除法操作停止的控制。 S是符号位,V是溢出标志。

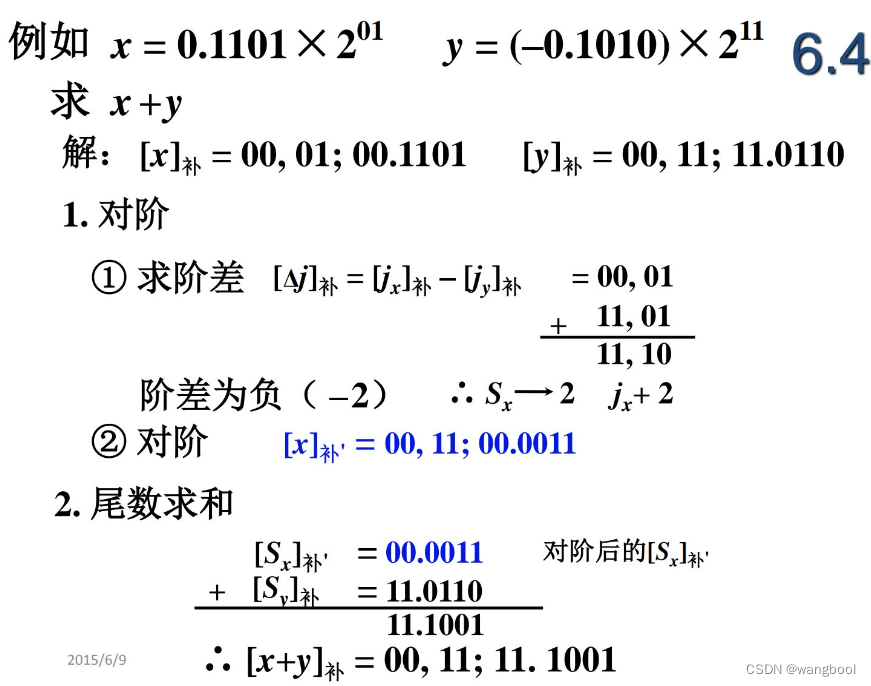

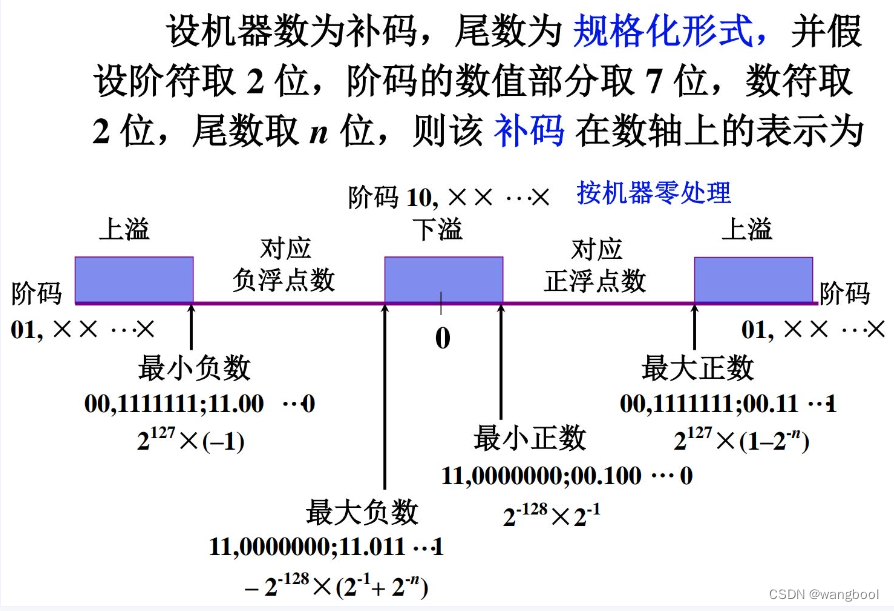

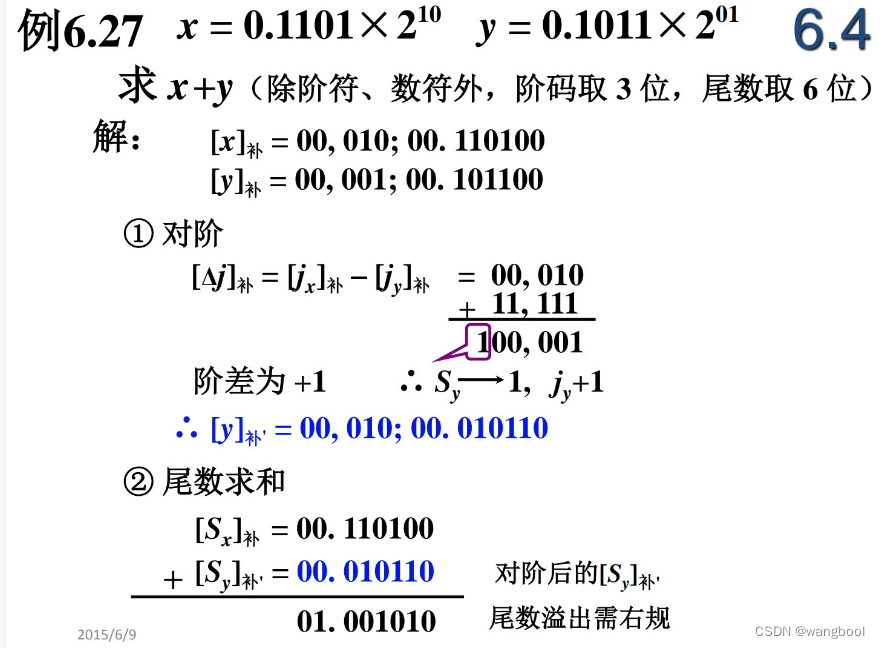

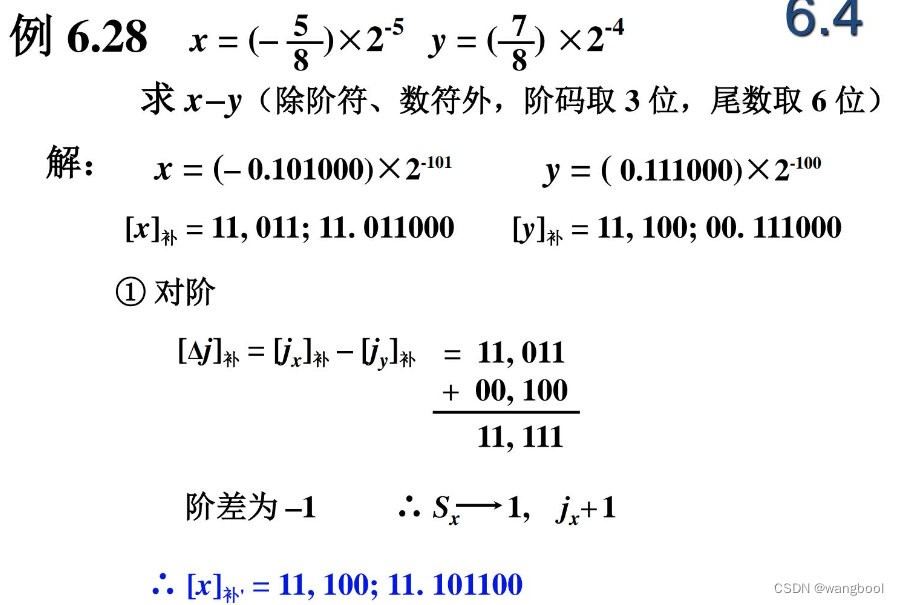

(四)浮点四则运算

1.浮点数的加减运算

x = S x ⋅ 2 j x y = S y ⋅ 2 j y x = S_x \cdot 2^{j_x} \quad \quad y = S_y\cdot2^{j_y} x=Sx⋅2jxy=Sy⋅2jy

算数运算的的常识是:两个浮点数如果要进行加减法运算的话,他们的阶或者是指数,必须是相同的。如果在基值相同的情况下,阶码不同,就需要对阶码的值进行调整,在调整阶码的值的时候,尾数的值也需要进行调整。通过阶码和尾数两部分的调整,保证参与运算的数据真值大小不发生变化,依然是原来参加运算的数据的值。

1.1.对阶

求阶差:用两个阶码做减法操作。

δ

j

=

j

x

−

j

y

=

{

=

1

j

x

=

j

y

已对齐

>

0

j

x

>

j

y

{

x

向

y

对齐

(

减小

j

x

)

S

x

←

1

,

j

x

−

1

y

向

x

对齐

(

增加

j

y

)

S

y

→

1

,

j

y

+

1

<

0

j

x

<

j

y

{

x

向

y

对齐

(

增加

j

x

)

S

x

→

1

,

j

x

+

1

y

向

x

对齐

(

减小

j

y

)

S

y

←

1

,

j

y

−

1

\delta j =j_x-j_y = \left\{ \begin{aligned} &=1\quad j_x = j_y \quad 已对齐\\ & > 0 \quad j_x>j_y{\left\{\begin{aligned}&x向y对齐(减小j_x)\quad S_x\leftarrow1,j_x-1\\&y向x对齐(增加j_y)\quad S_y\rightarrow1,j_y+1\end{aligned}\right.}\\&<0\quad j_x<j_y{\left\{\begin{aligned}&x向y对齐(增加j_x)\quad S_x\rightarrow1,j_x+1\\&y向x对齐(减小j_y)\quad S_y\leftarrow1,j_y-1\end{aligned}\right.} \end{aligned} \right.

δj=jx−jy=⎩

⎨

⎧=1jx=jy已对齐>0jx>jy{x向y对齐(减小jx)Sx←1,jx−1y向x对齐(增加jy)Sy→1,jy+1<0jx<jy{x向y对齐(增加jx)Sx→1,jx+1y向x对齐(减小jy)Sy←1,jy−1

对阶原则:小阶向大阶看齐

在计算机当中,只能小阶向大阶对齐,如果大阶向小阶对齐,即大阶的尾数要向左移,此时可能会导致尾数高位丢失导致数据错误,而小阶向大阶对齐,则小阶的尾数右移,此时小阶的低位数据可能丢失,导致数据精度下降,但不会导致数据错误。

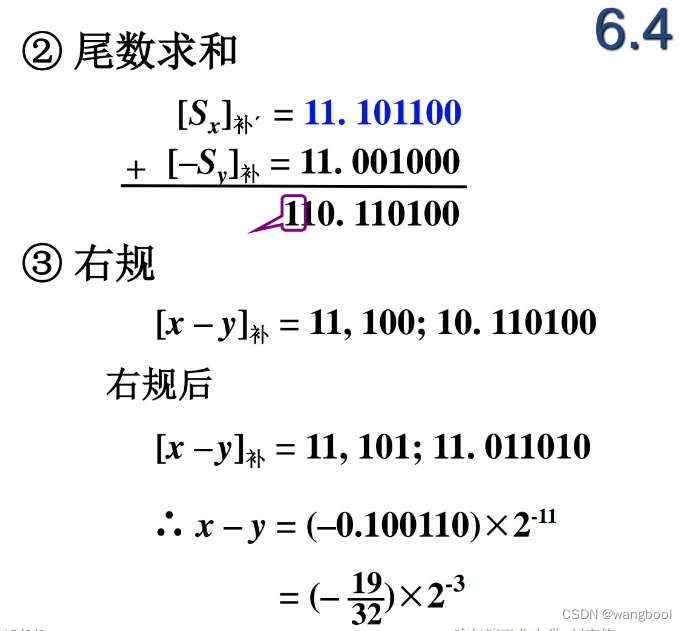

1.2.尾数求和

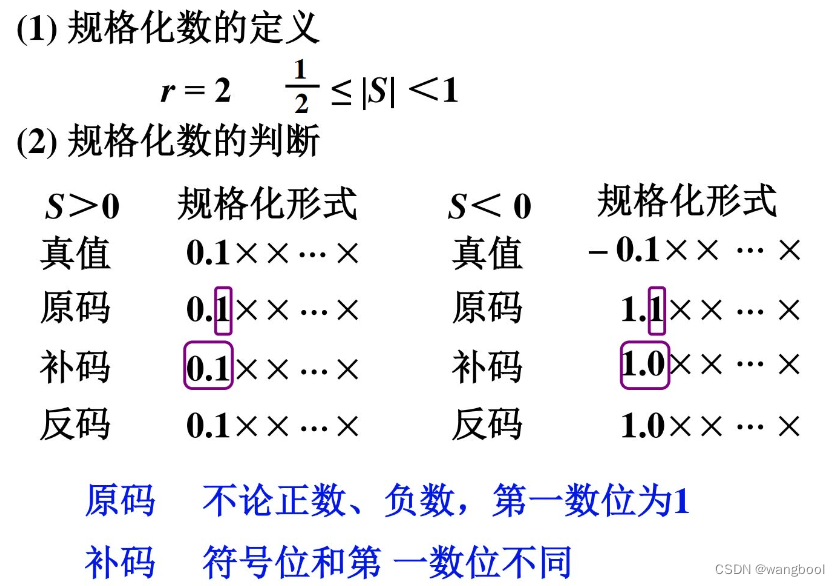

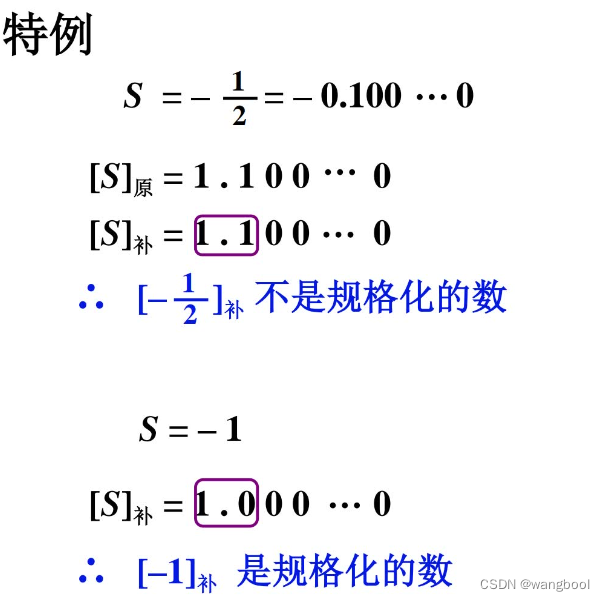

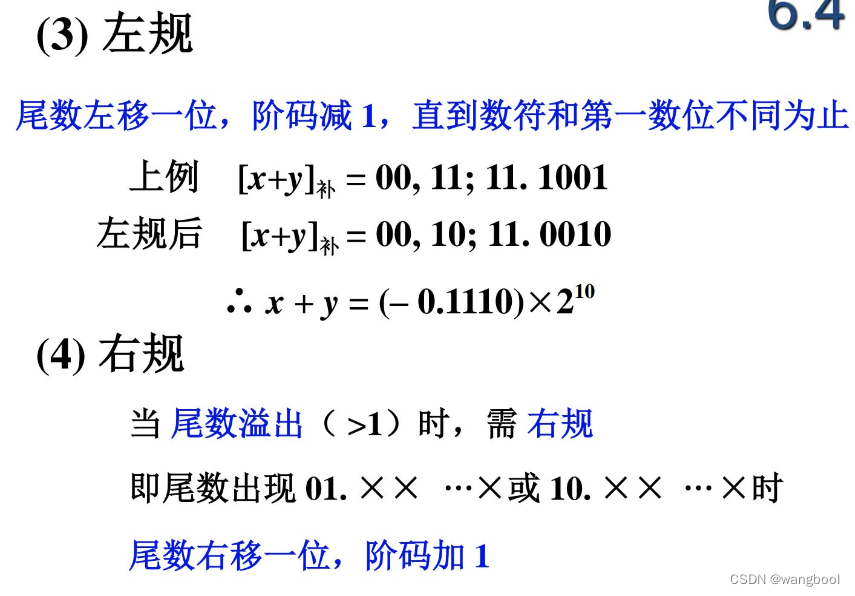

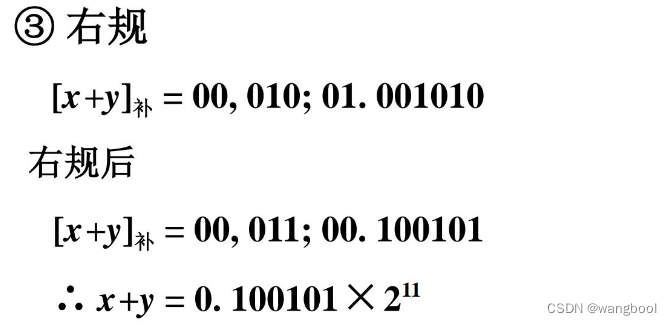

1.3.规格化

为了尽可能提高在计算机中浮点数表示精度。

01.XXX…X真正的符号位是0,两个正数相加就有可能造成这种溢出,尾数右移一位,阶码加1,将溢出的进位重新放回尾数中,可能会影响精度。

1.4.舍入

数据的长度超过了计算机当中存储数据的物理器件能够保存的数据的长度,因此低位部分就要被处理,保证数据能够以比较精确的保存在计算机当中。在对阶和右规过程中,都可能出现尾数末尾丢失,引起误差,为尽可能减少误差,需考虑舍入。

0舍1入法:如果被丢掉的数据是1,那么在可保存数据的最低位加1,是0就不做处理。

末位恒置1法:不管末尾丢掉的数据的是什么,这个保存的数据的最低位永远置为1。

留个小尾巴,查阅其他舍入方法,思考其优缺点,一定要记得查资料!

1.5.溢出判断

存放在计算机当中的数据字长是有限的,表示的数的个数和表示的数据的大小也是有限的,即使在可表示的那一部分数据的范围中,表示出来的那些数据也是离散的,如果在计算机可以表示的数据范围内,某一个点没有正好落在计算机可表示的数据的那个点上,那么只能用近似的值进行表示。

1.6.举例

2.浮点的乘除法运算

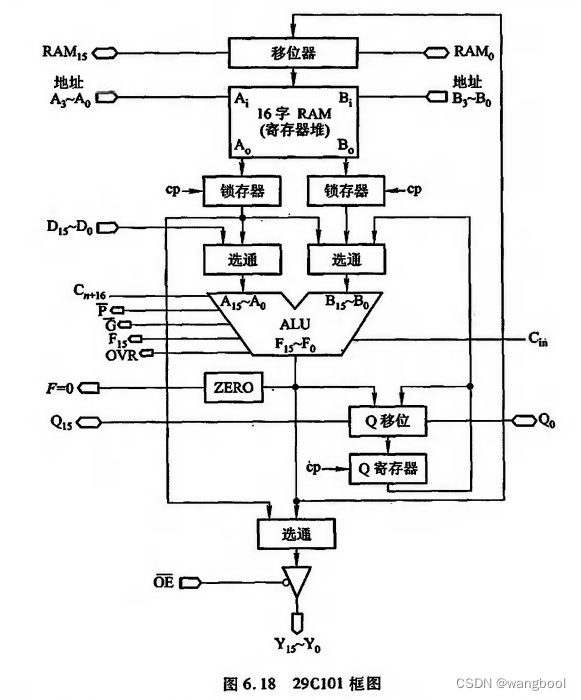

(五)算术逻辑单元

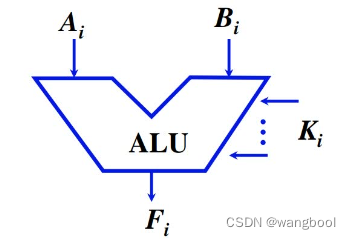

定点运算,浮点运算等运算的硬件电路在计算机当中被集成到一个被称为算术逻辑单元的电路当中,算术逻辑单元和计算机系统当中的控制器集成在一起构成了计算机系统的CPU。

1.ALU电路

A

i

A_i

Ai和

B

i

B_i

Bi表示参加运算的数据,

F

i

F_i

Fi表示输出的运算结果,

K

i

K_i

Ki是控制端,决定要进行什么样的运算,

K

i

K_i

Ki不同取值,则

F

i

F_i

Fi不同。

ALU电路是一个组合逻辑电路,所谓组合逻辑电路是没有记忆功能的,输入消失,输出端的运算结果也会消失,为了对输出的结果进行保存,并且使运算能够稳定,在输入端

A

i

A_i

Ai和

B

i

B_i

Bi都要连接寄存器,输出端

F

i

F_i

Fi也要连接寄存器。

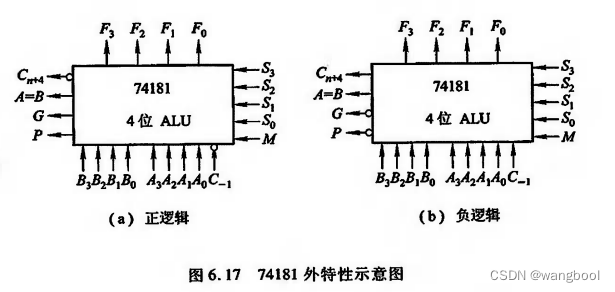

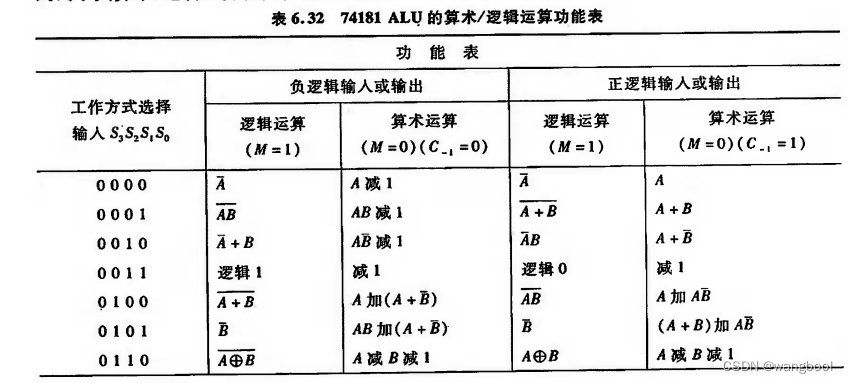

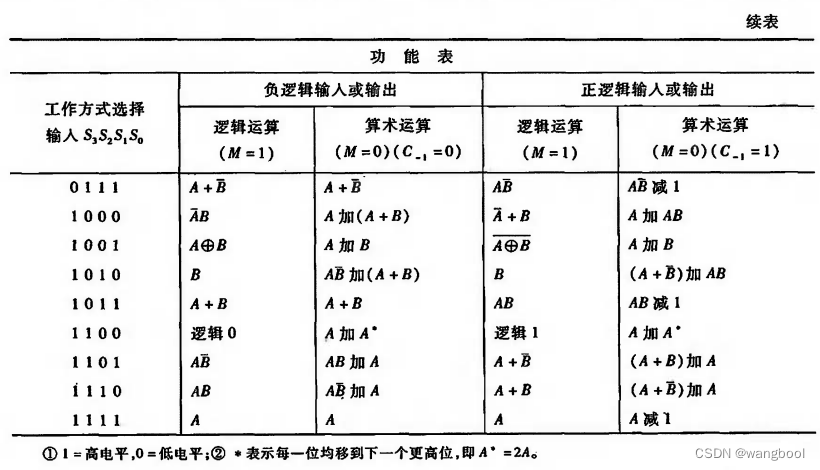

1.1.举例:74181

实现四位数的算术运算和逻辑运算。

- M=0----算术运算

- M=1----逻辑运算

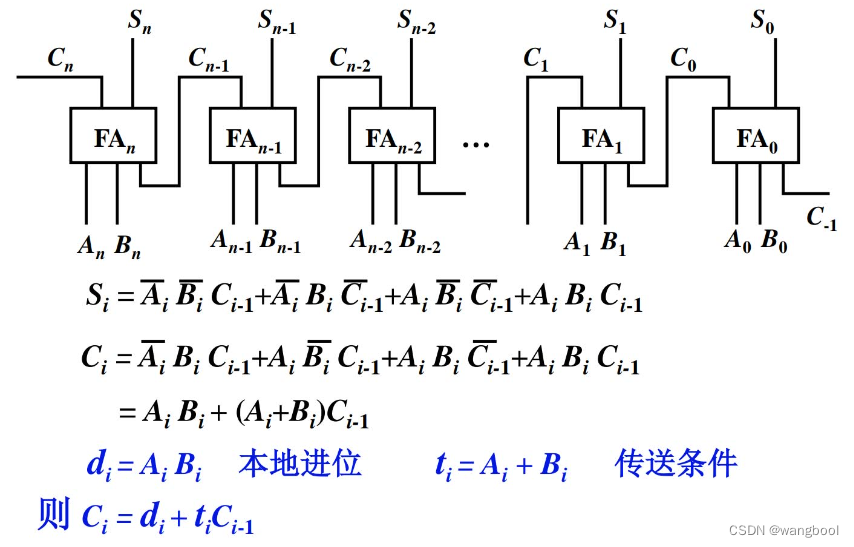

2.快速进位链

2.1.并行加法器

在并行加法器中,影响运算速率的瓶颈就是

C

i

−

1

C_{i-1}

Ci−1,如果能快速产生进位,就能提高加法运算速度。

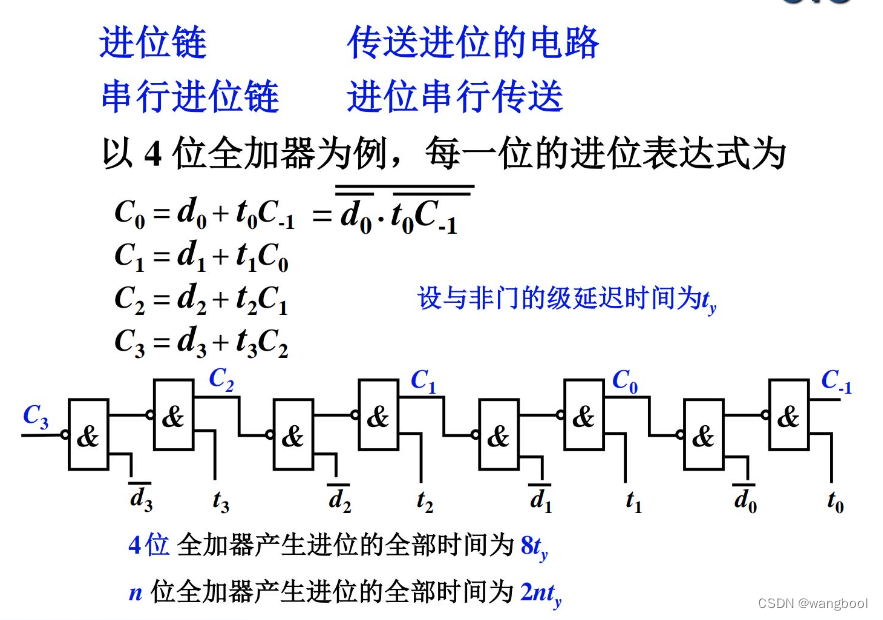

2.2.串行进位链

从上图可知,进位链就是影响加法速度的瓶颈,需要想办法提高加法运算中进位链的速率。

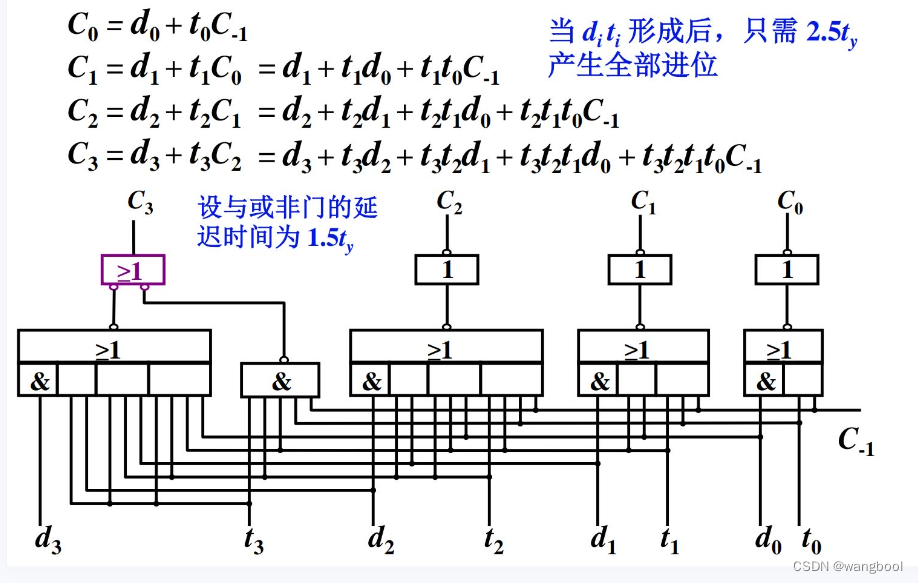

2.3.并行进位链(先行进位,跳跃进位)

n位加法器的进位同时产生。

存在问题:电路比较复杂,如果是32位的计算,那么这个进位电路将会非常恐怖!

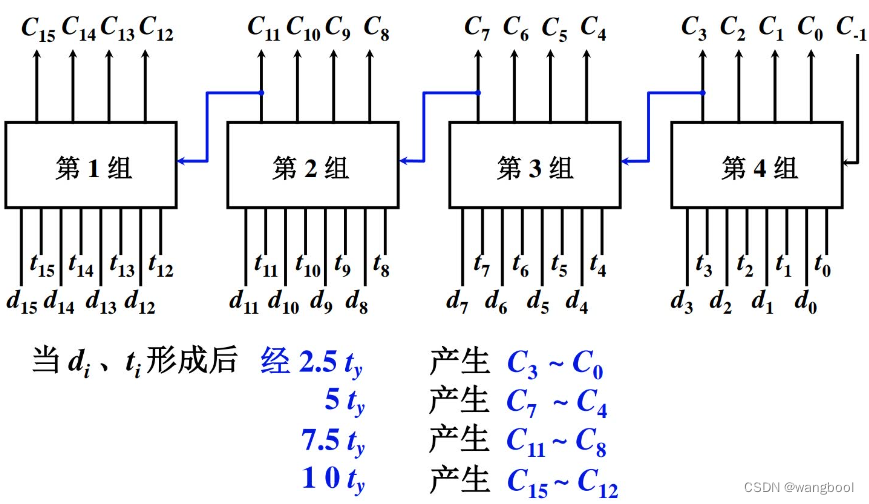

2.4.单重分组跳跃进位链

n位全加器分若干小组,小组中的进位同时产生,小组与小组之间采用串行进位。

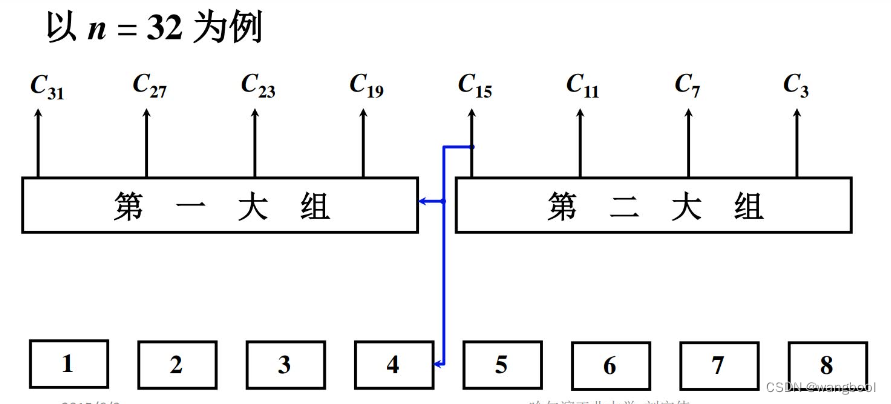

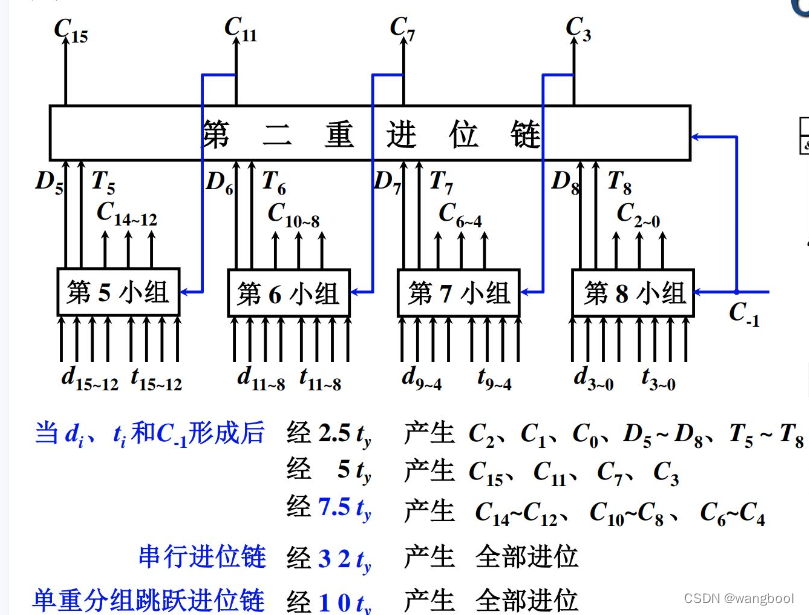

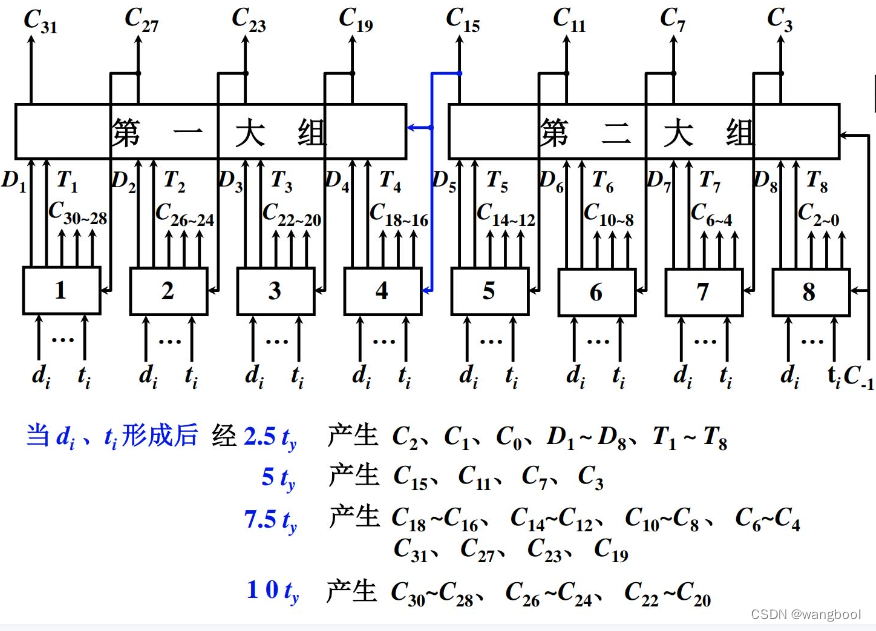

2.5.双重分组跳跃进位链

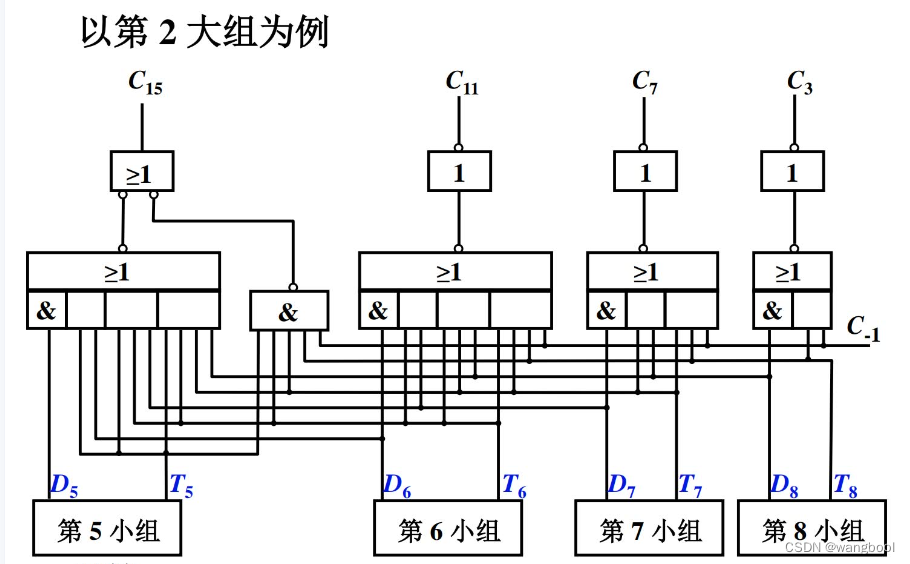

n位全加器分为若干大组,大组中又包含若干小组,每个大组中小组的最高位进位同时产生,大组和大组之间采用串行进位。

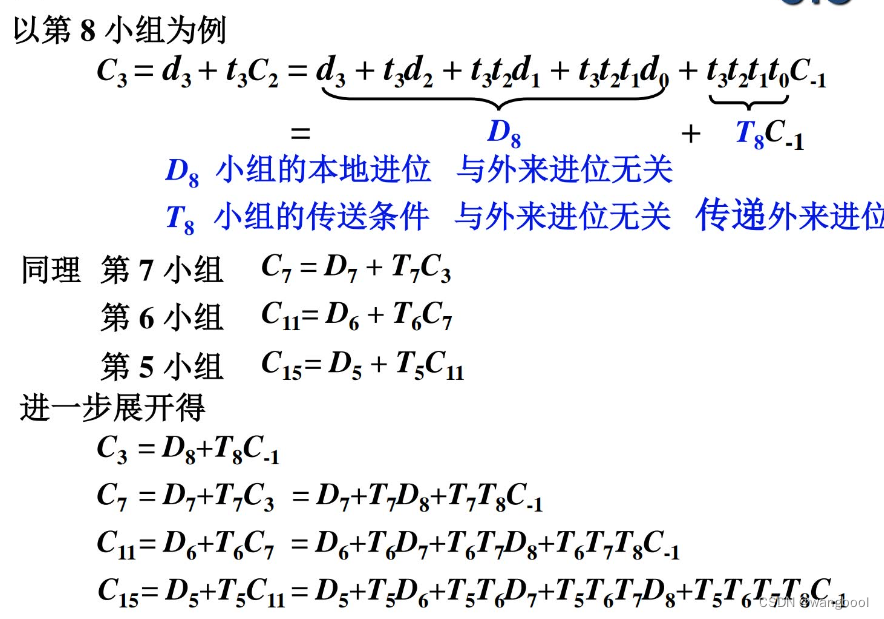

2.5.1.大组进位分析

D

D

D和

T

T

T只与本小组输入的

B

i

B_i

Bi和

A

i

A_i

Ai有关,只要

B

i

B_i

Bi和

A

i

A_i

Ai已知,就可以用逻辑电路计算出

D

D

D和

T

T

T,然后用与或非门加非门的方式生成电路。

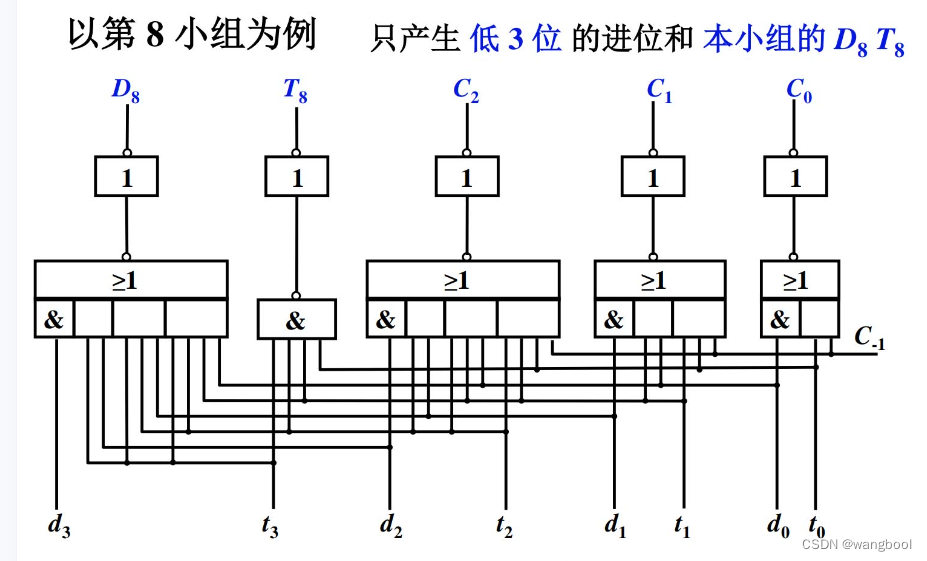

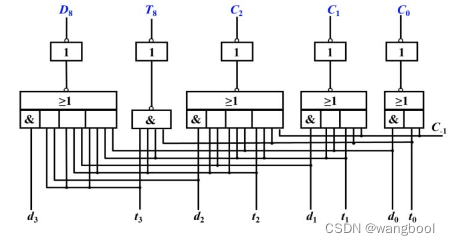

2.5.2.小组进位线路

2.5.3. n = 16 n = 16 n=16的双重分组跳跃进位链

第一重进位链产生三个进位

C

0

、

C

1

、

C

2

C_0、C _1、C_2

C0、C1、C2和各小组的本地进位

D

D

D、传送条件

T

T

T。

第二重进位链利用每个小组的本地进位

D

D

D和传送条件

T

T

T,以及上个小组的最高位进位,产生这个大组当中每个小组的最高位的进位。

2.5.4. n = 32 n = 32 n=32的双重分组跳跃进位链

1757

1757

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?