文章目录

1、实验目的

①学习 Quartus 、Platform Designer、Nios-II SBT 的基本操作;

②初步了解 SOPC 的开发流程,基本掌握 Nios-II 软核的定制方法;

③掌握 Nios-II 软件的开发流程,软件的基本调试方法。

2、实验设备

硬件:PC 机、DE2-115 FPGA 实验开发平台;

软件:Quartus Prime 18.1、Platform Designer、Nios II SBT

3、实验内容

①在DE2-115开发板上用Nios软件编程方式完成LED流水灯显示

②用Nios软件编程通过DE2-115开发板串口输出“Hello Nios-II”字符到笔记本电脑串口助手

4、实验原理

4.1 nios介绍

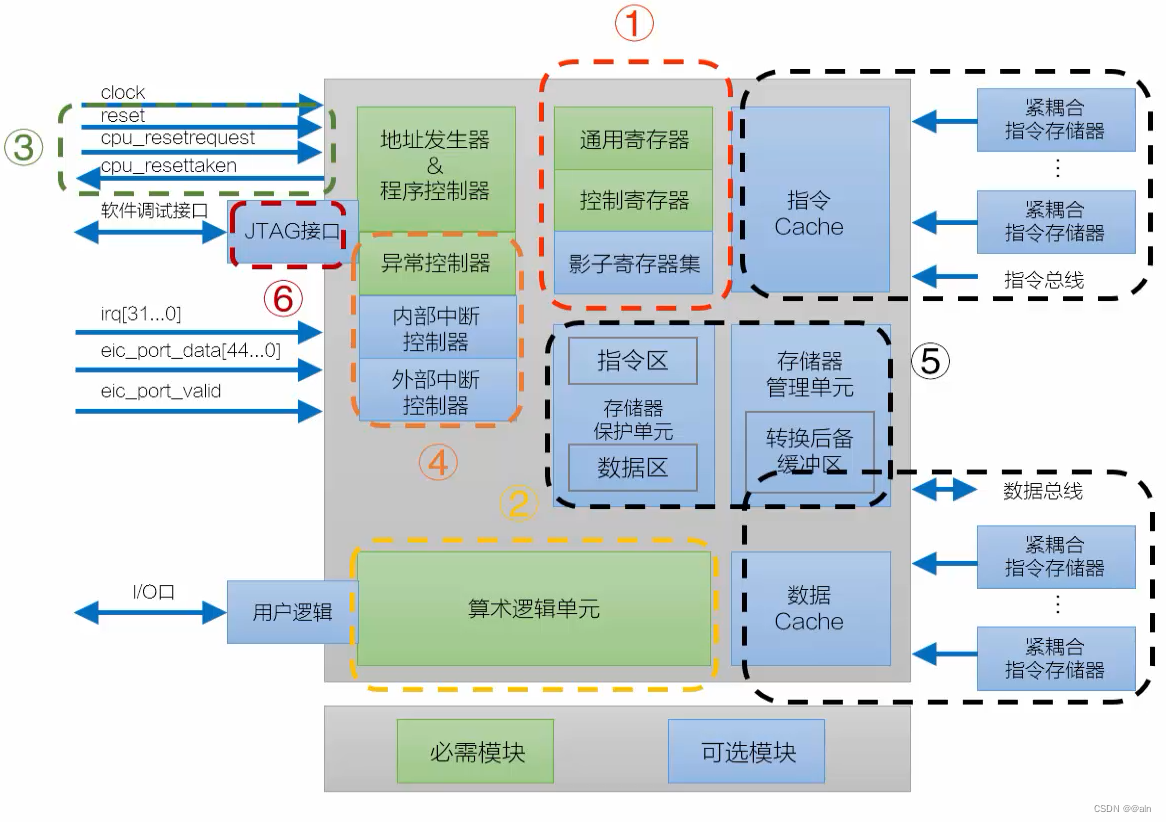

NIOS硬件框架结构

①、处理器

①、处理器

在弄清楚什么是软核处理器之前,需要首先明白什么是处理器,这里笔者浅显的作一番解释。众所周知处,理器是可以按照指令序列完成特定的逻辑功能的集成电路,一般的常见的微控制器都为SOC,即片上系统,包括中央处理单元、总线、存储器、外设,比如大家熟知STM32,其F103系列就是由Coretex-M3内核、AHBAPB总线、RAM、ROM以及GPIO等等一些外设组成的,上述所有的内容包含在一个芯片上,所以称之为片上系统,也是常说的微处理器。

②、软核处理器

具有FPGA和数字电路基础知识的读者应该清楚,FPGA可以通过编程实现几乎所有的数字电路的功能,并且由于Verilog HDL等硬件描述语言具有类似于C语言这类高级语言的特点,还能描述一些复杂的功能。而处理器无非也是由触发器、寄存器、逻辑门这些基本的数字电路器件构成的,所以理论上来说,我们可以通过编程对一些处理器在FPGA上进行复刻,进行引脚分配以后,可以让FPGA变成一个处理器。软核处理器无非就是使用硬件描述语言来描述一个片上系统,使其可以实现微处理器的功能,相较于传统的封装好的处理器芯片,软核处理器具有可裁剪的特性、外设定制灵活等等优越性。

但是一个CPU的集成器件是非常多的,如果想要通过手工编写并进行逻辑分析是一件非常困难的事情。并且既然使用FPGA来实现一个CPU已经具有了这么多的灵活性,为什么不充分发挥他的优点,不再单纯的去模仿一些已经存在的处理器,而是设计一个能将FPGA的优势发挥到极致的全新的处理器。NIOS II由此应运而生。

4.2 具体原理

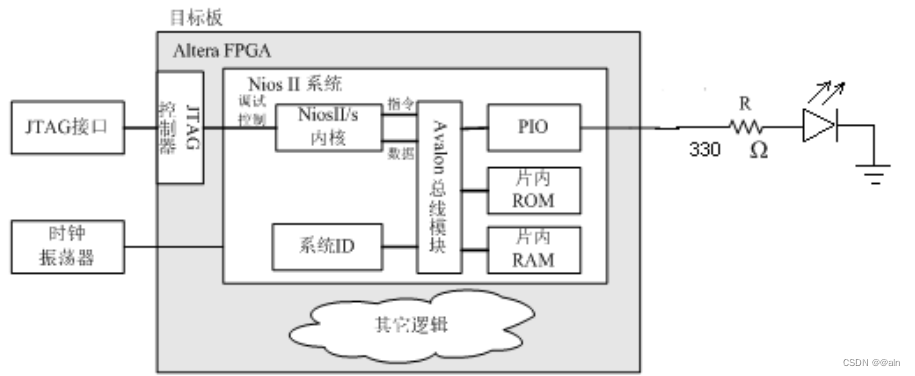

控制 LED 灯闪烁的用户程序代码很小,可将其固化在片内 ROM 来执行。变量、堆栈

等空间使用片内 RAM,不使用任何片外存储器。整个系统的框图如图 1 所示。

从图 1.1 控制 LED 闪烁的系统框图可知,其它逻辑与 Nios II 系统一样可存在于 FPGA

中。Nios II 系统可与其它片内逻辑相互作用,取决于整个系统的需要。为了简单起见,本实

验在 FPGA 内不包括其它逻辑。

5、实验步骤

5.1新建项目

5.2 Qsys 系统设计

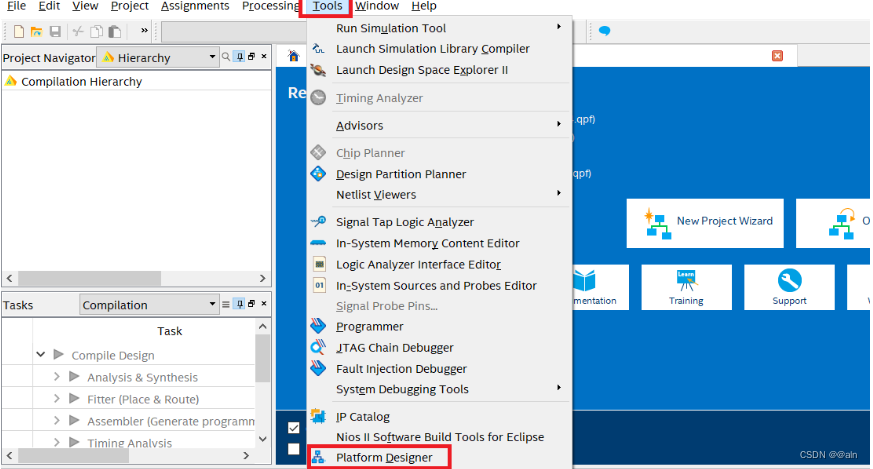

①点击 Tools 下拉菜单下的 Platform Designer 工具

②启动 Platform Designer 后,点击 File-save,在文件名中填写为 kernel

后点击 OK

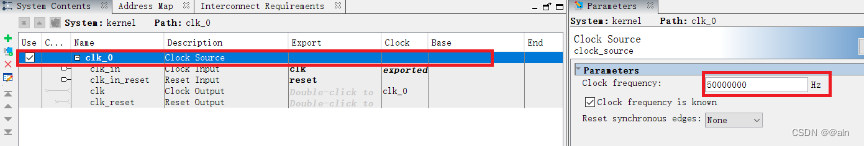

③鼠标放在 clk_0 处点击右键 Edit 或是双击 clk_0 元件,对 Clock 进行时钟设置,设为 50M

④添加 CPU 和外围器件。从 PD 的元件池中选择以下元件加入到当前设计的系统中:Nios II 32-bit CPU、jtag uart、片上存储器、PIO、system ID。

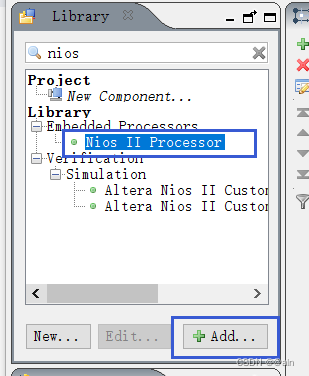

⑤在 “component library” 标签栏中找到 “Nios II Processor” 后点击 Add

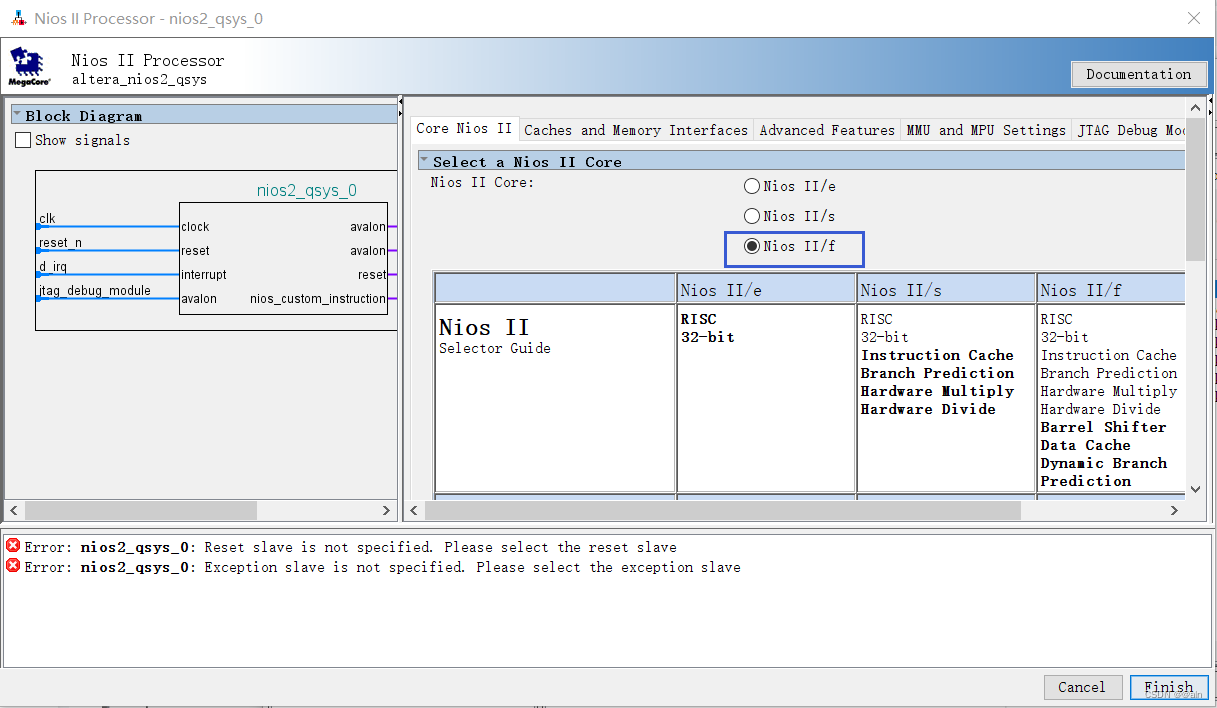

⑥在 Nios Core 栏中选择 Nios II/f 选项,其他保持默认选项

⑦在 ”Caches and Memory Interfaces” 标签栏中保持默认设置 (Instruction Cache 选择

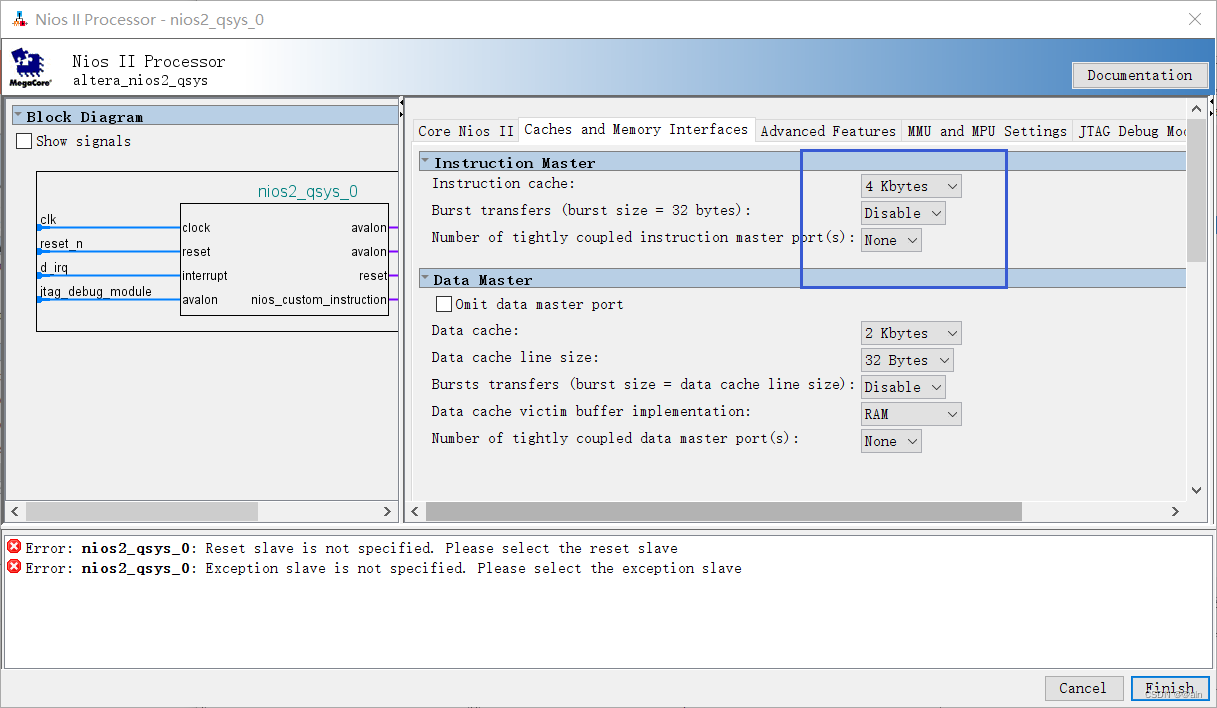

4Kbytes),在 ”Advanced Features” 标签栏中保持默认设置, 在 ”MMU and MPU Settings” 标签栏中保持默认设置,在 ”JTAG Debug Module” 标签栏中保持默认设置

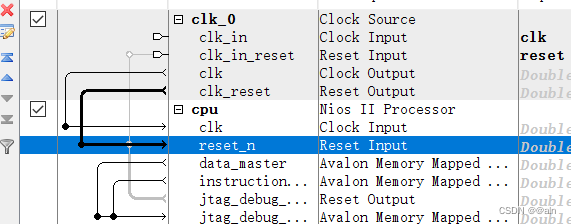

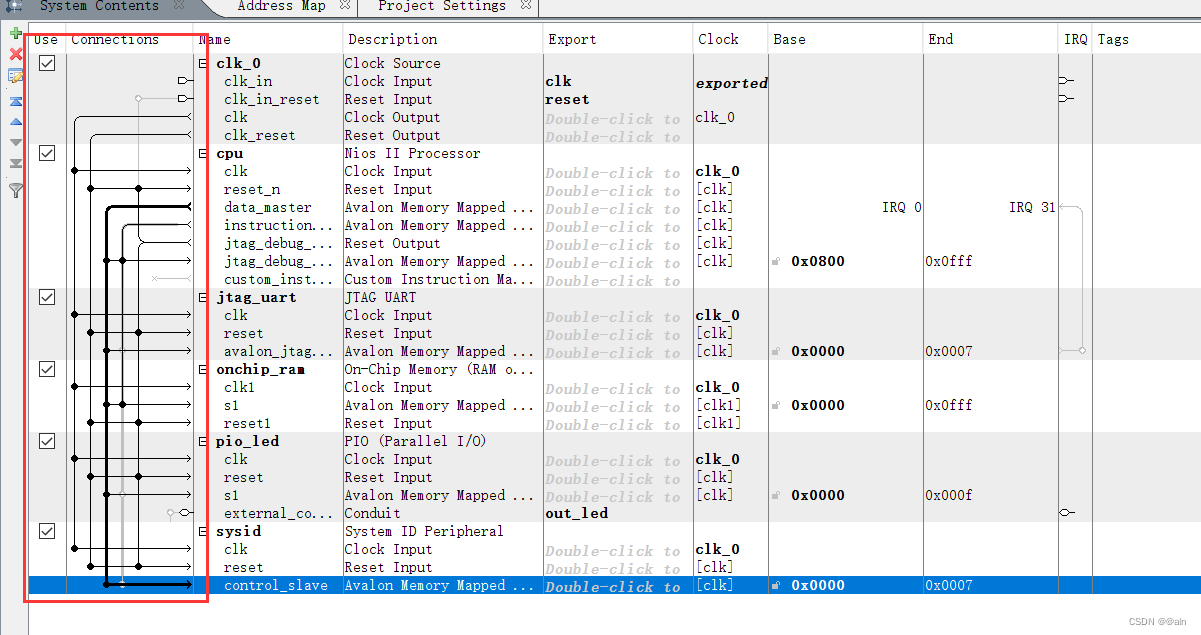

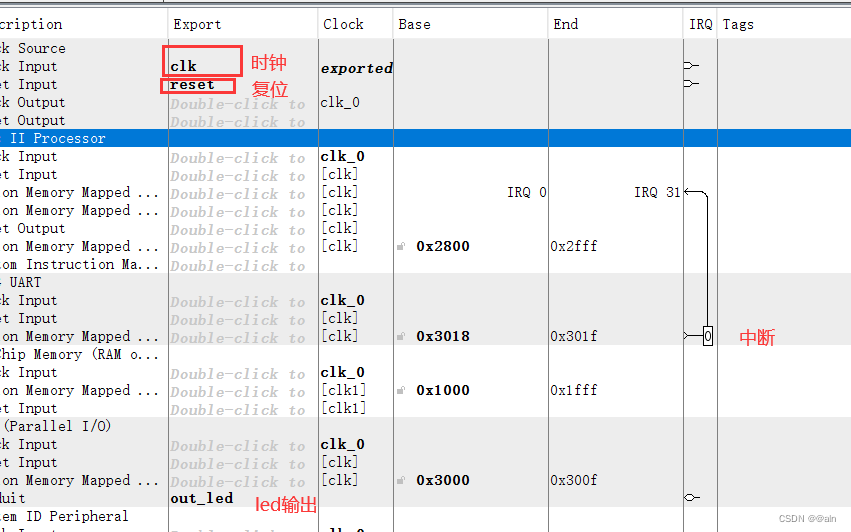

⑧点击 Finish 回到 Qsys 界面 将 nios2_qsys_0 重命名为 cpu,点击 ”Rename” 即可重新命名,将 cpu 的 clk 和 reste_n 分别与系统时钟 clk_0 的 clk 和 clk_reset 相连

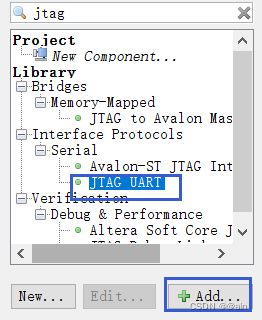

⑨同样,在 ”Component Library” 标签栏中的查找窗口输入 jtag 找到 ”JTAG UART ”,然后点击 Add

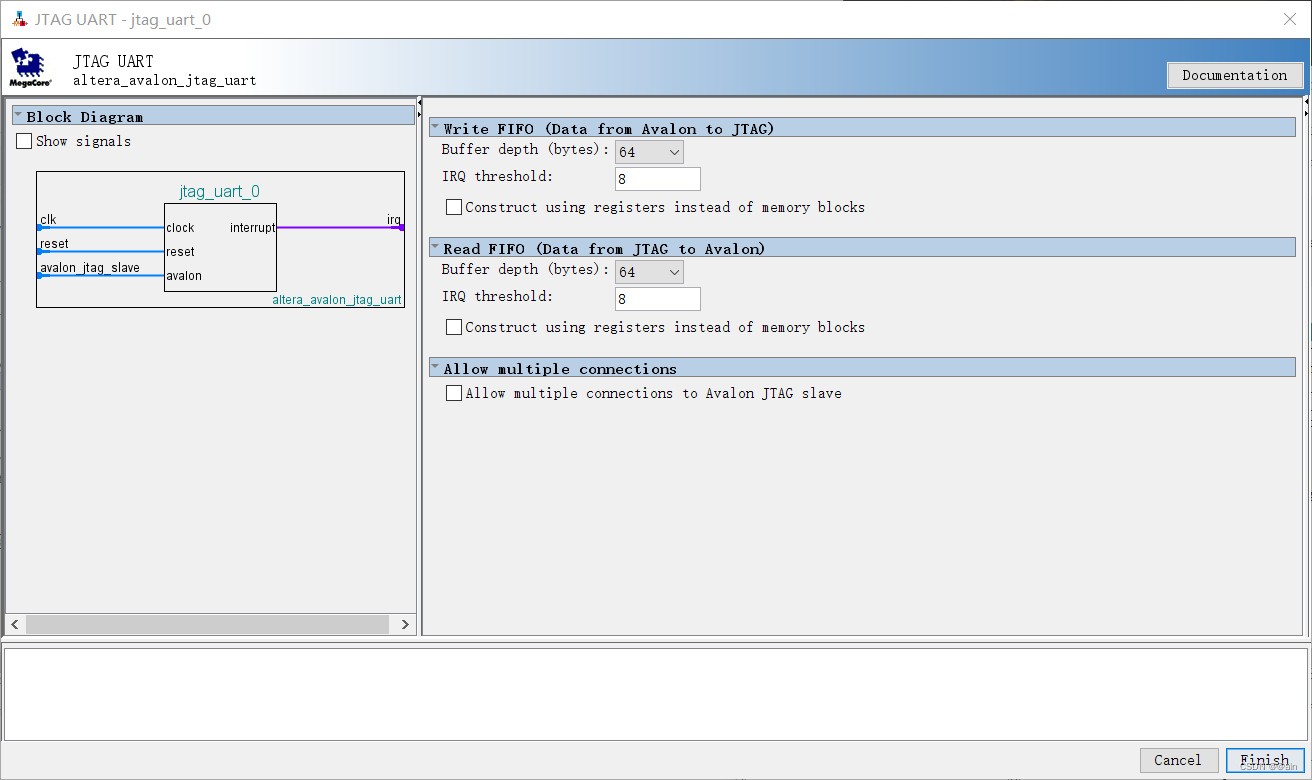

①〇 在 JTAG UART-jtag-uart_0 的设置向导中保持默认选项,点击 Finish

①① 返回 ”System Contents” 标签栏可以看到新加入的 ”JTAG UART” 核。在 ”Name” 列中将

jtag-uart_0 重命名为 jtag-uart。进行 clk、reset 以及 master-slave 的连线,进行中断 irq 连线

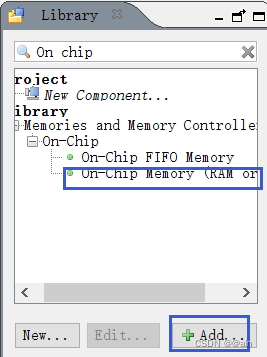

①② 在左侧 ”Component Library” 标签栏中的查找窗口输入 On Chip 找到 ”On-Chip

Memory(RAM or ROM)” 后点击 Add

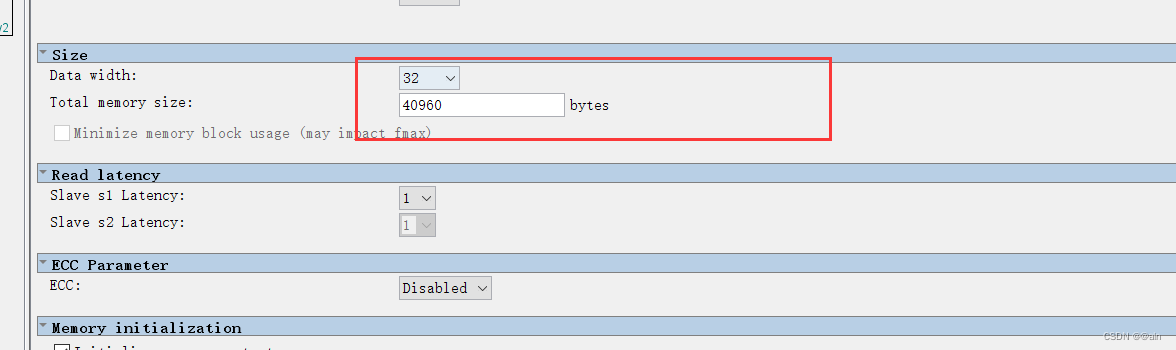

①③在 ”Size” 栏中的 ”Total memory size” 窗口中输入 40960(即片上内存的大小为 40KB),其余选项保持默认,点击 Finish。

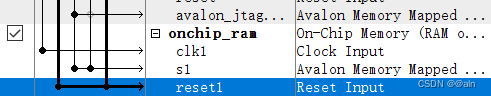

①④返回 ”System Contents” 标签栏可以看到新加入的 ”On-Chip Memory” 核。在 ”Name”

列中将 onchip_memory2_0 改名为 onchip_ram。进行时钟、数据端口、指令端口的连接。

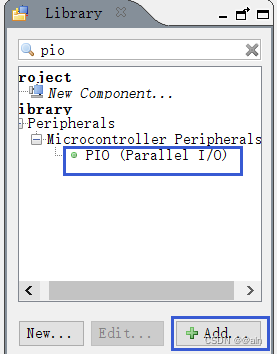

①⑤在左侧 ”Component Library” 标签栏中的查找窗口输入 pio 找到 ”PIO” 后点击Add

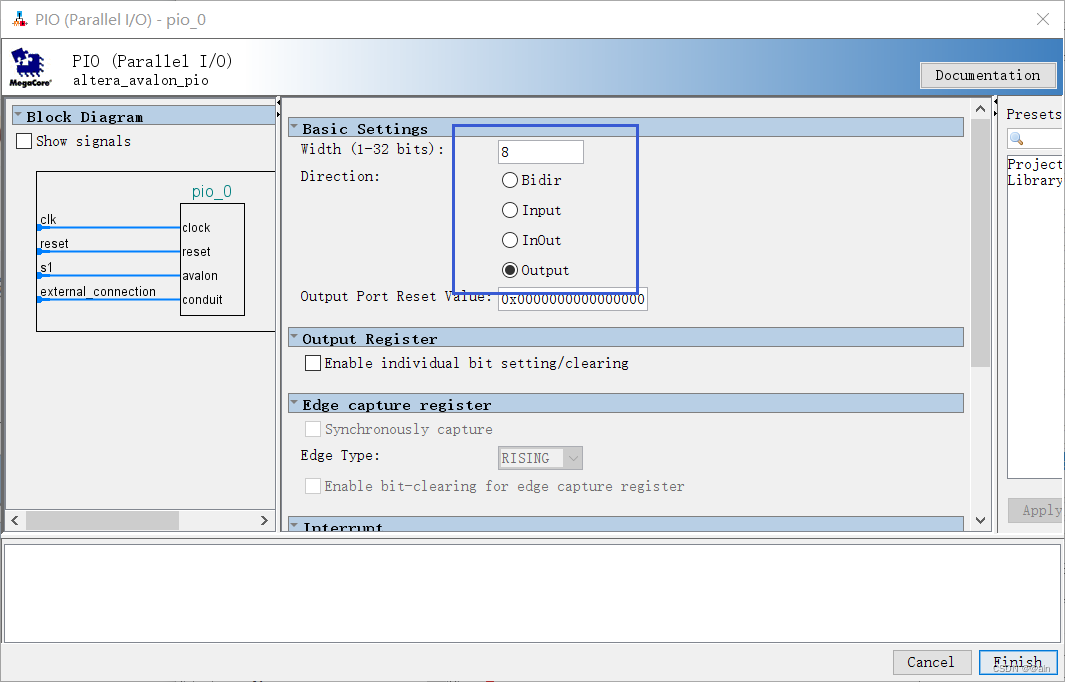

①⑥确定以下选项:Width 为 8bits,Direction 选择 output,其余选项保持默认,点击

Finish

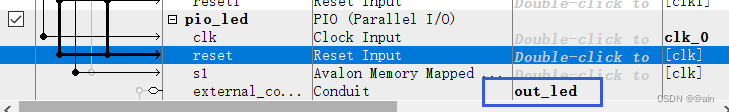

①⑦返回 ”System Contents” 标签栏可以看到新加入的 ”PIO” 核。在 ”Name” 列中将

pio_0 改名为 pio_led。并在在 Export 栏处双击,把输出口引出来,并命名为 out_led。

进行时钟、数据端口、指令端口的连接。

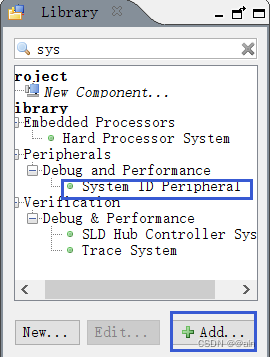

①⑧在左侧 ”Component Library” 标签栏中的查找窗口输入 sys 找到 ” System ID

Peripheral” 后点击 Add。保持默认选项,单击 Finish。

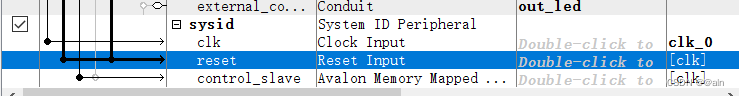

①⑨返回 ”System Contents” 标签栏可以看到新加入的 ” System ID Peripheral” 核。在 ”Name” 列中将 sysid_qsys_0 改名为 sysid。进行时钟、数据端口的连接。

②0 再次确认检查

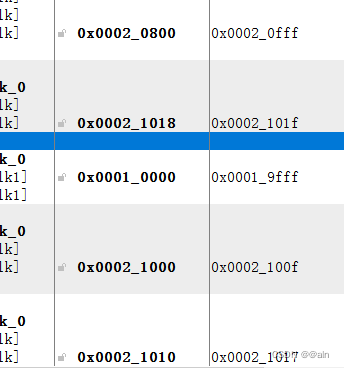

②① 点击 Qsys 主界面菜单栏中的 ”System” 下的 ”Assign Base Addresses”

②②在 ”IRQ” 标签栏下点选 ”Avalon_jtag_slave” 和 IRQ 的连接点就会为 ”jtag_uart” 核添加一个值为 0 的中断号

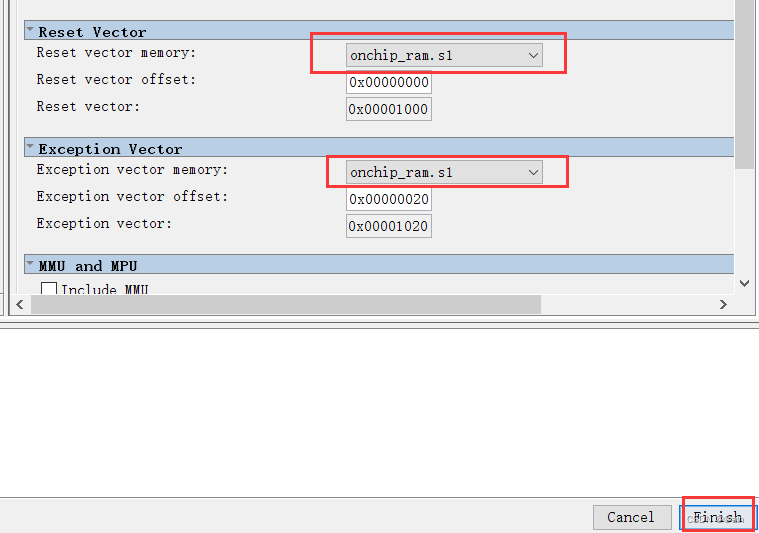

②③从 ”System Contents” 标签栏双击建立好的 cpu 进入 Nios IIProcessor 的配置界面,配置 Reset Vector 和 Exception Vector 为”onchip_ram.s1”,点击 Finish。

②④点击 Qsys 主界面菜单栏中的 ”System” 下的 ”Create Global Reset Network”。完成后会自动连接所有复位端口

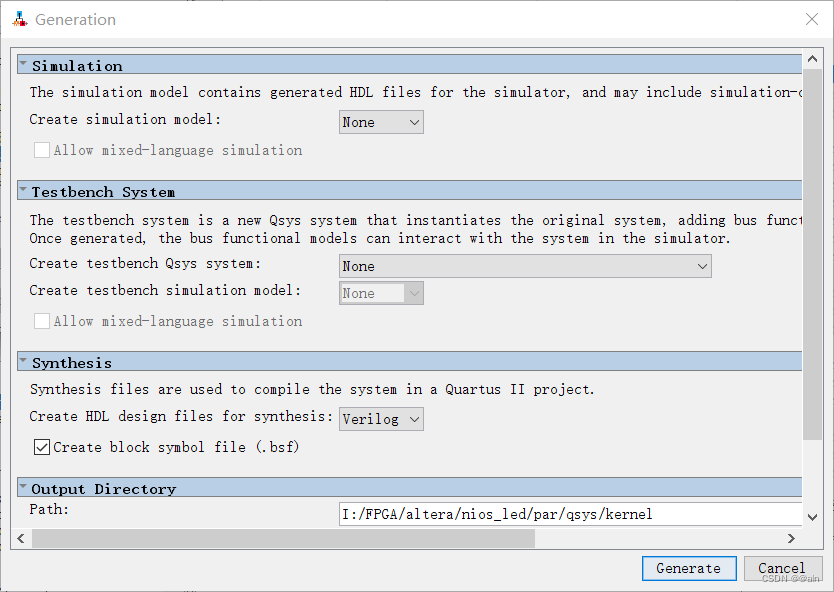

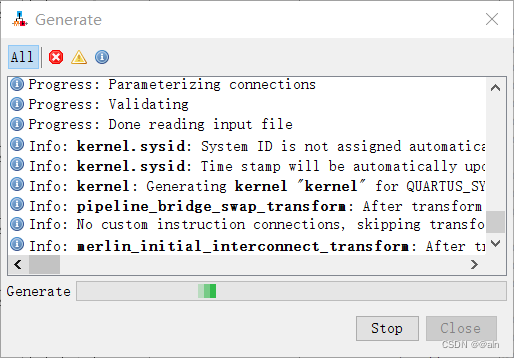

②⑤点选 ”Generation HDL” 标签栏中 Generate 按钮生成 Qsys 系统,保存文件

②⑥完成后,点击 Close 后关闭窗口后,再关闭 Qsys 主界面

5.3逻辑及引脚配置

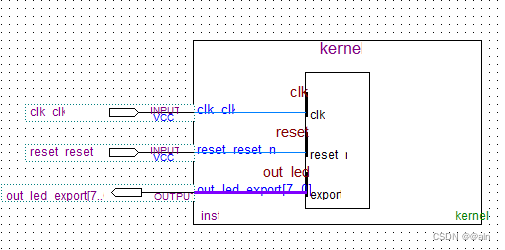

①在 Quartus-II 中新建一个原理图

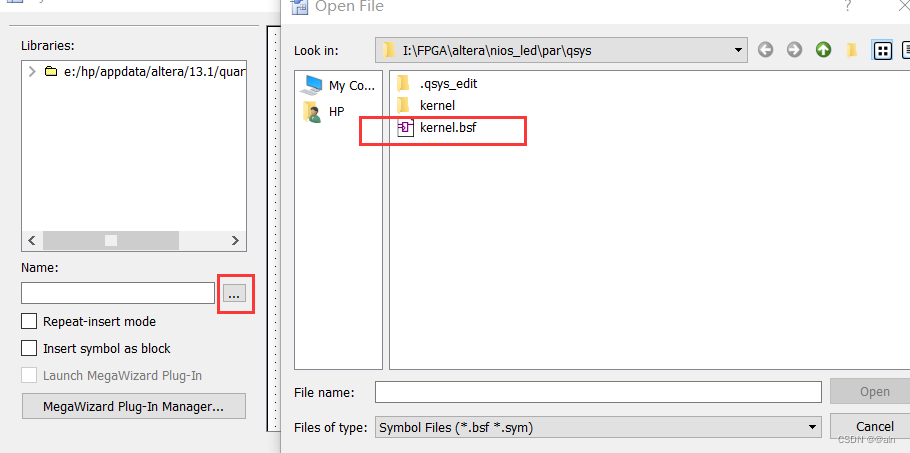

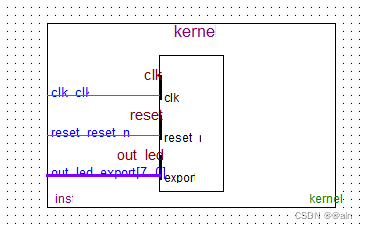

②在该原理图(BDF)文件中添加 Qsys 生成的系统符号

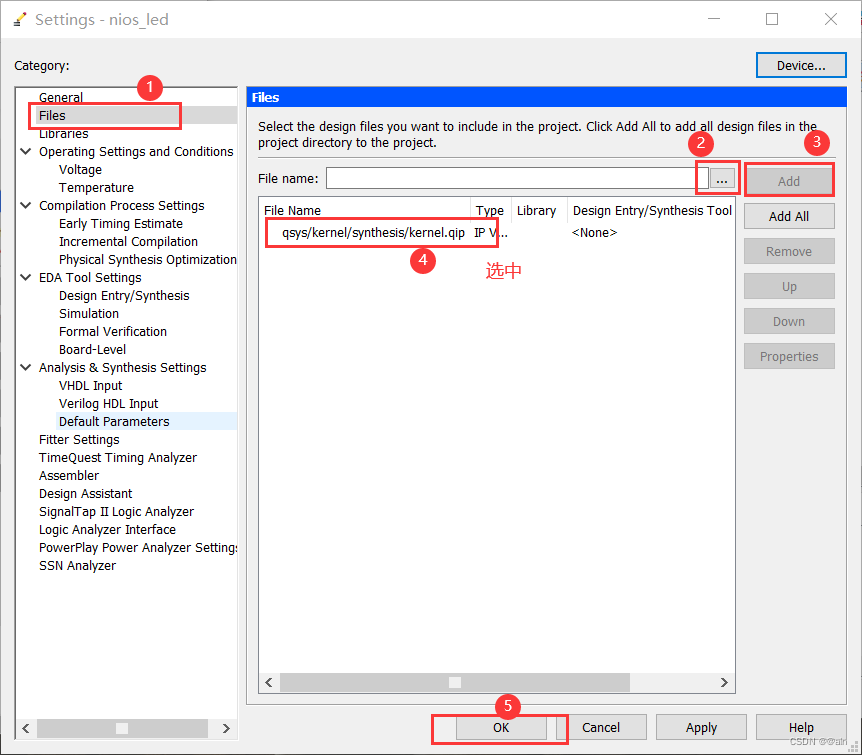

③点击 Assignments-Settings,添加 kernel.qip 文件

④在 kernel 模块内点击鼠标右键选取 Generate Pin for Symbol Ports 生成管脚,然后将管脚命名如下

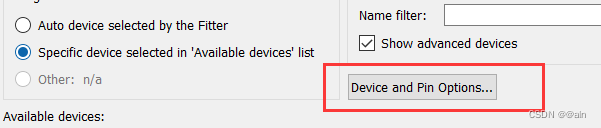

⑤菜单里选择 Assignments-device,然后如下图所示点击 Device pin options

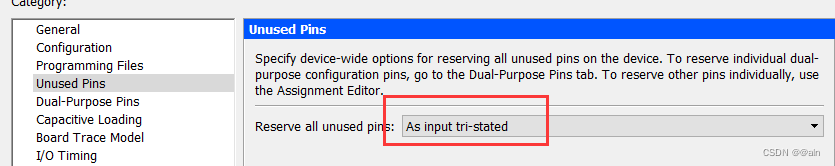

⑥进行 unused pin 设置,可能会收到外部信号的干扰,将未用引脚设置为 As

input tri-stated

(编译工程)

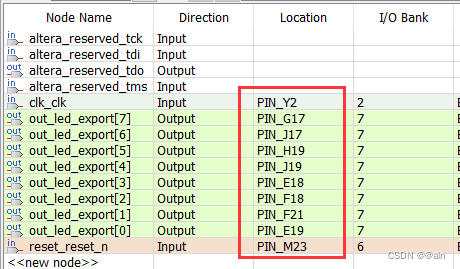

⑦分配物理针脚

(再次编译工程,至此完成项目的硬件设计)

5.4设计

①在 Quartus-II 界面,点击Tools,然后点击 Nios II Software Build Tools for Eclipse 打开 Nios II SBT for Eclipse。启动 Workspace 选择当前的项目目录,点 OK。

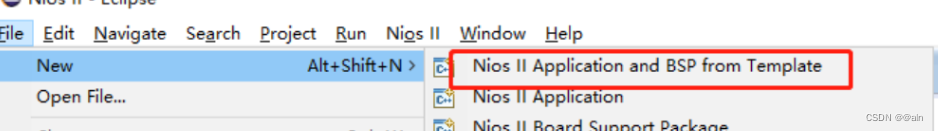

②创建工程

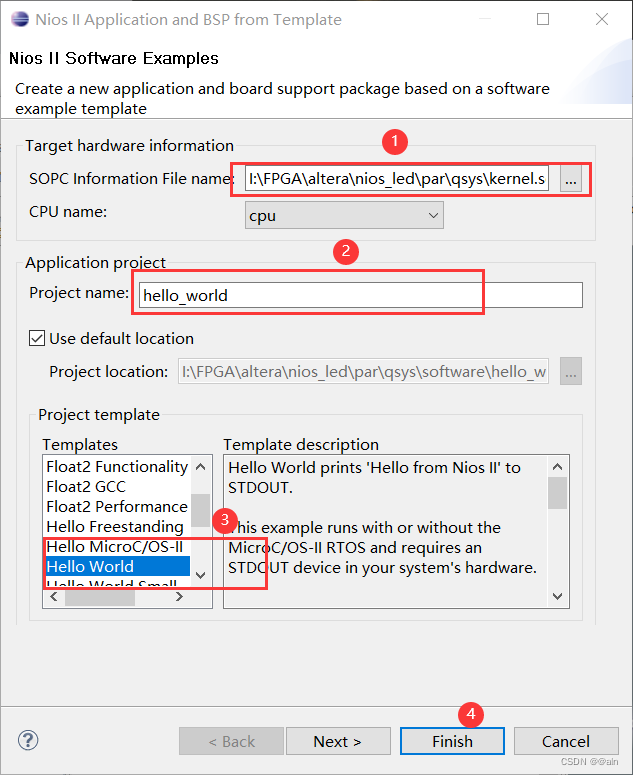

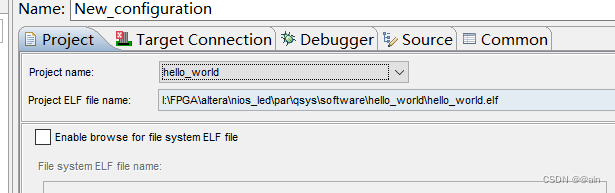

③在 ”SOPC Information File name” 窗口中选择 kernel.sopcinfo 文件,以便将生成硬件配置信息和软件应用关联,CPU 栏会自动选择”CPU”。在 ”Project name” 输入 ”hello_world” ,Project template选择 Hello World。

④将 hello_world.c 中的程序修改为流水灯控制程序,保存。

#include "system.h"

#include "altera_avalon_pio_regs.h"

#include "alt_types.h"

const alt_u8

led_data[8]={0x01,0x03,0x07,0x0F,0x1F,0x3F,0x7F,0xFF};

int main (void) {

int count=0;

alt_u8 led;

volatile int i;

while (1)

{

if (count==7)

{count=0;}

else

{count++;}

led=led_data[count];

IOWR_ALTERA_AVALON_PIO_DATA(PIO_LED_BASE, led);

i = 0;

while (i<500000)

i++;

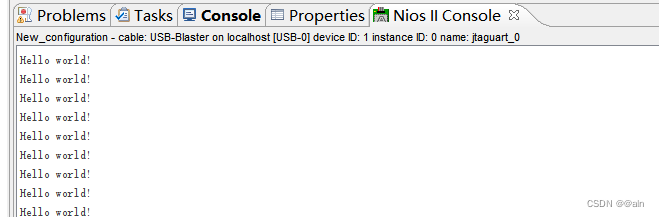

printf("Hello world!\n");

}

return 0;

}

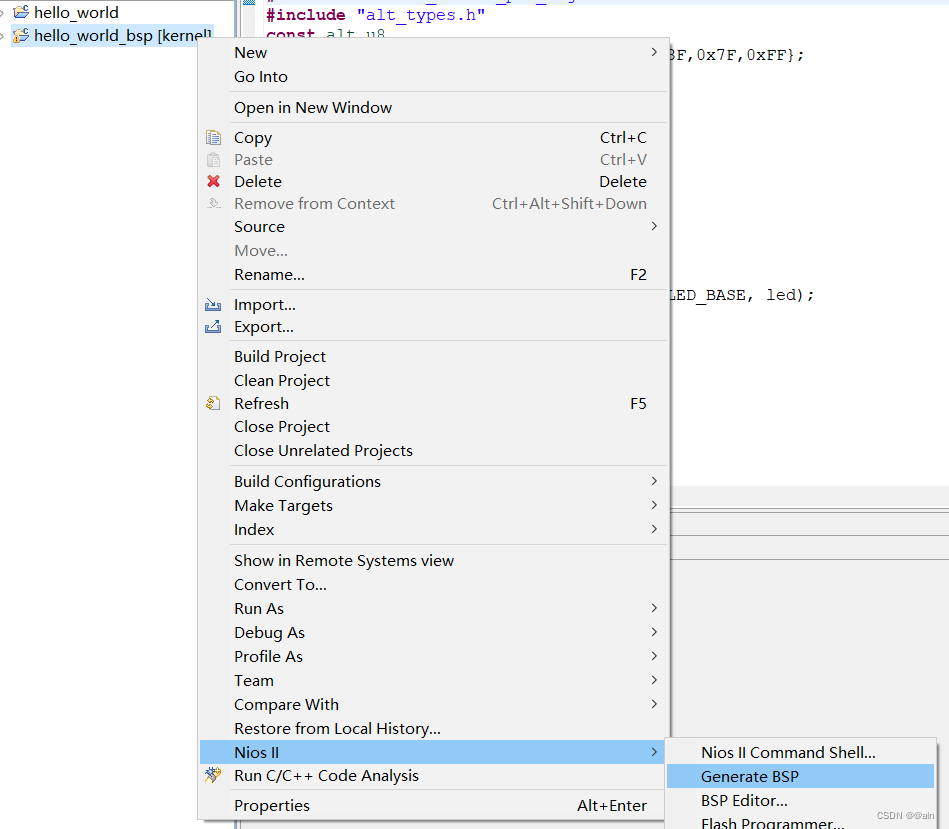

⑤选择hello_wold_bsp,右键后,选择Nios II中的Generate BSP

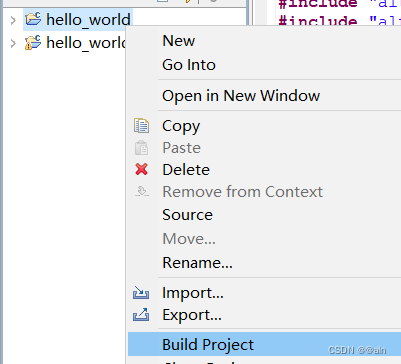

⑥右键单击项目名称,在弹出的菜单中选择 Build Project

5.5测试

①连接 JTAG 到开发板,确定 A.已正确安装驱动。B. 防火墙不会影响到 JTAG

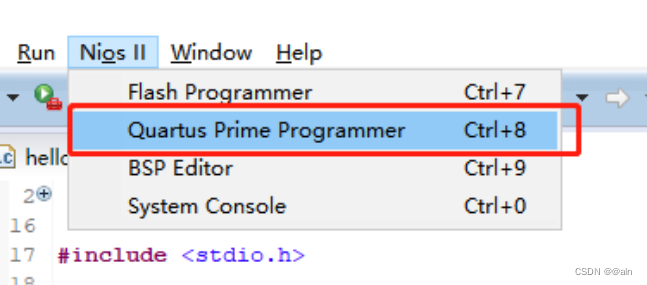

的正常工作。最后给开发板上电。 如下图所示,启动 Quartus Prime Prog。添加下载文件。然后点击 Start 开始下载,下载成过后关闭,回到 Eclipse 主机面

②运行/调式程序

③菜单栏中选择 Run →Run Configurations,配置 Run Configurations,选择project

④转到”Target Connection”标签栏,点击右侧的 Refresh

Connections 将 USB-Blaster 加入,如下图所示。

⑤Apply 后,Run。下载完成后,可以看见 Console 里打印信息

⑥开发板的 LED 灯循坏闪烁

6、总结

除了掌握 Quartus Prime、Platform Designer 和 Nios II SBT 的基本操作外,随着不断发展 SOPC 设计技能,可能会接触到更复杂的配置和体系结构。比如集成多个 IP、自定义接口或实现高级控制逻辑。而且为了充分利用 Nios II 软核的能力,了解其架构和功能非常重要。这其中会涉及到探索可用的各种处理器核心类型、了解系统外设的作用以及开发使用 Nios II 指令集的专业知识。最后在实验的过程中也需要养成良好的编码实践,例如模块化设计、文档编写和版本控制。这将有助于我编写高效、易于维护的代码,并能轻松地对项目进行修改和更新。

7、参考

https://blog.csdn.net/Mouer__/article/details/123856392

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?