前言

本次实验在quartus18.1中进行编写实现。程序烧录在Intel DE2-115开发板上进行验证。

一、加法器原理

在通过quartus编程在Intel DE2-115板子上实现一位全加器和四位全加器之前我们需要先了解其原理。

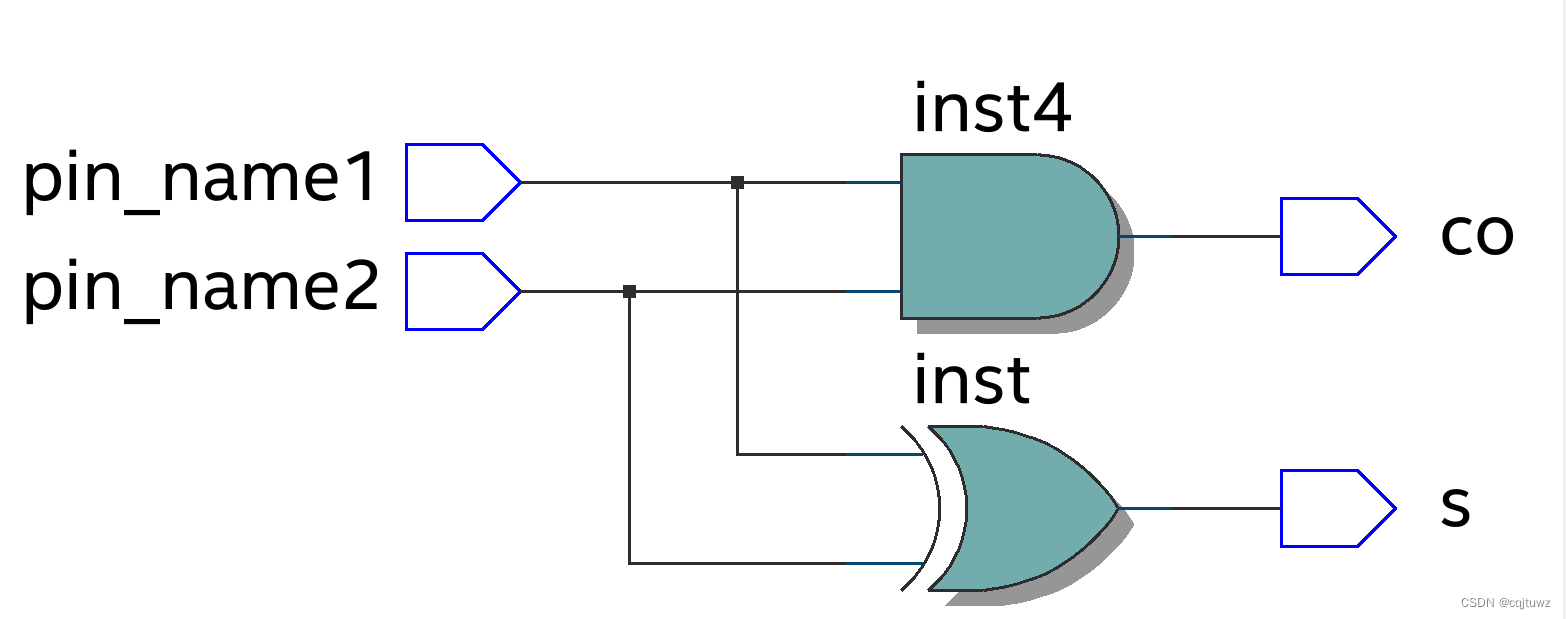

半加器

**原理:**半加器是指对输入的两个一位二进制数相加(A与B),输出一个结果位(SUM)和进位(C),没有进位的输入加法器电路,是一个实现一位二进制数的加法电路。

电路图:

真值表:

| 被加数A | 加数B | 和SUM | 进位C |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

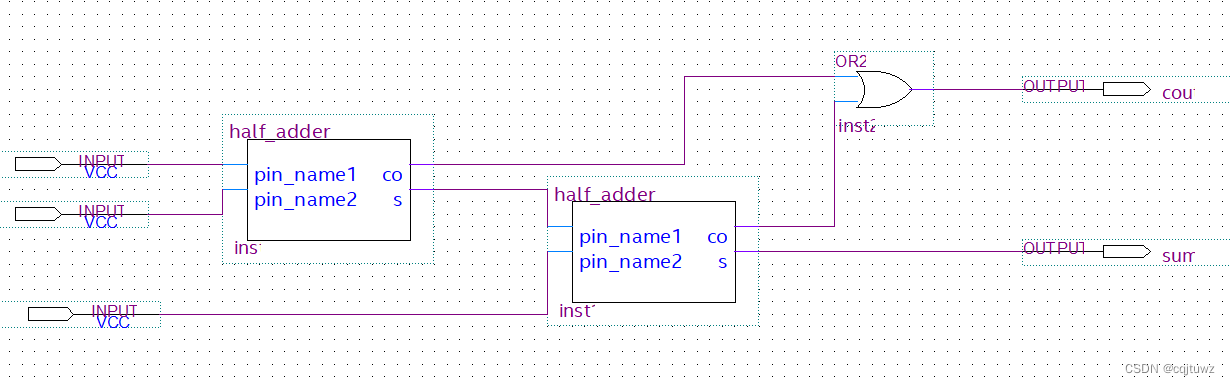

**原理:**在一位全加器是在半加器的基础上添加一个输入信号c表示前一位的进位情况,将半加器运算的结果再与信号c进行一个半加器的运算。

电路图:

真值表:

| Ain | Bin | Cin | Cout | Sum |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 1 | 1 |

输出表达式:

Sum=Ain⊕Bin⊕Cin

C o u t = ( A i n ⊕ B i n ) ⋅ C i n + A i n B i n = ( A i n & B i n ) ∣ ( B i n & C i n ) ∣ ( A i n & C i n )

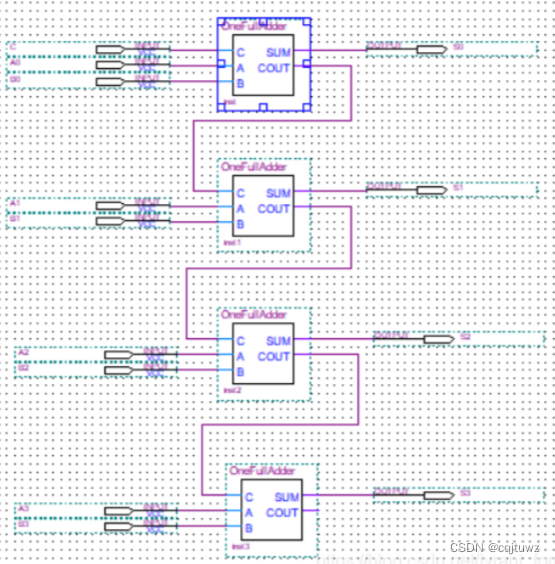

四位全加器

原理: 四位全加器是利用四个全加器,一一将前一个的输出进位参与到后一个的输入进位中进行运算,实现全加器。

电路图:

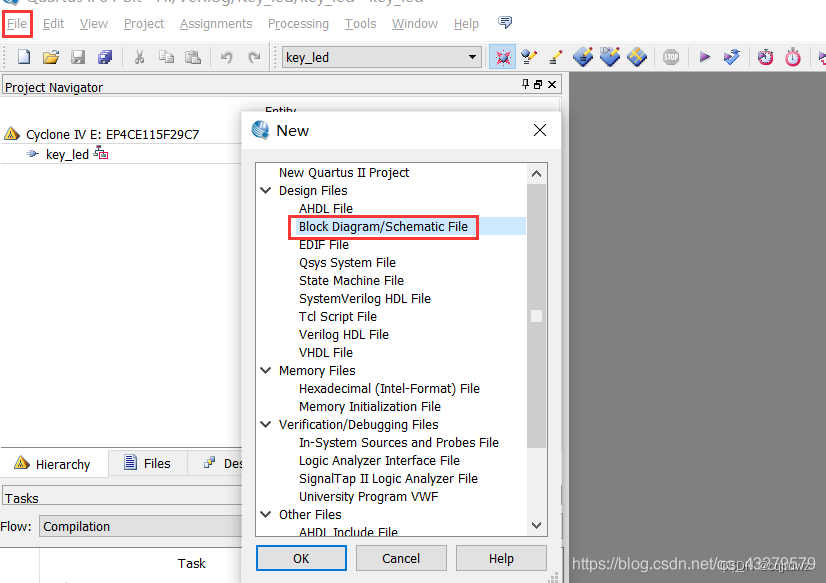

二、一位全加器的实现

一位全加器的原理图实现

1、先实现半加器

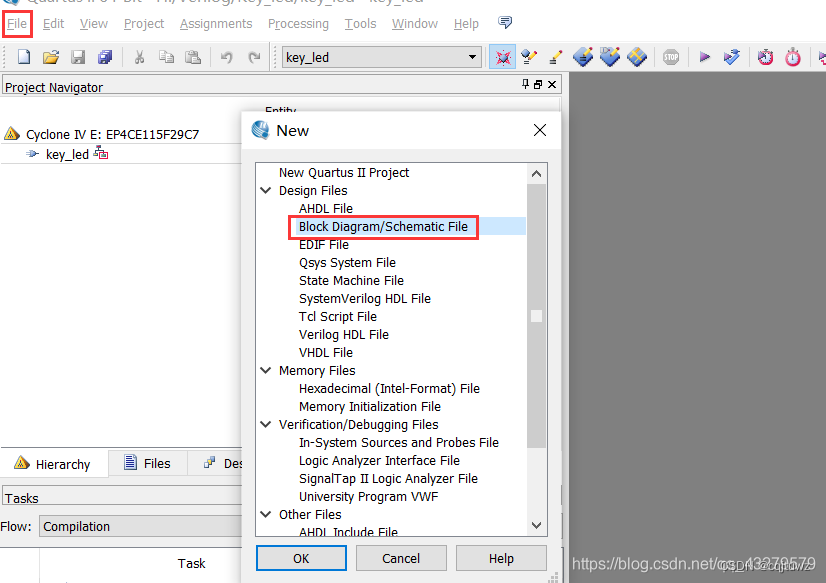

首先选择File->New,进入后选择Block Diagram/Schematic File

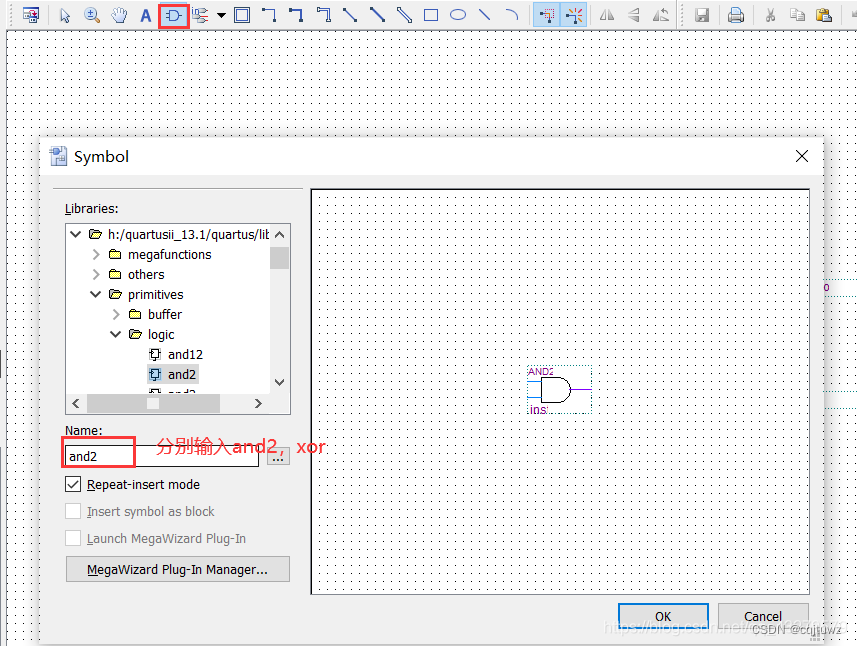

选择元件

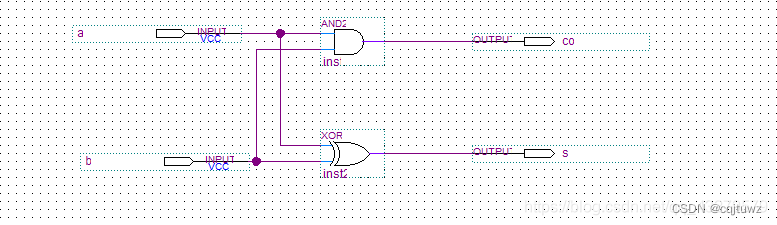

添加输入输出,完成效果

保存文件,并编译

通过tool->Netlist Viewers->RTL Viewer,查看电路图

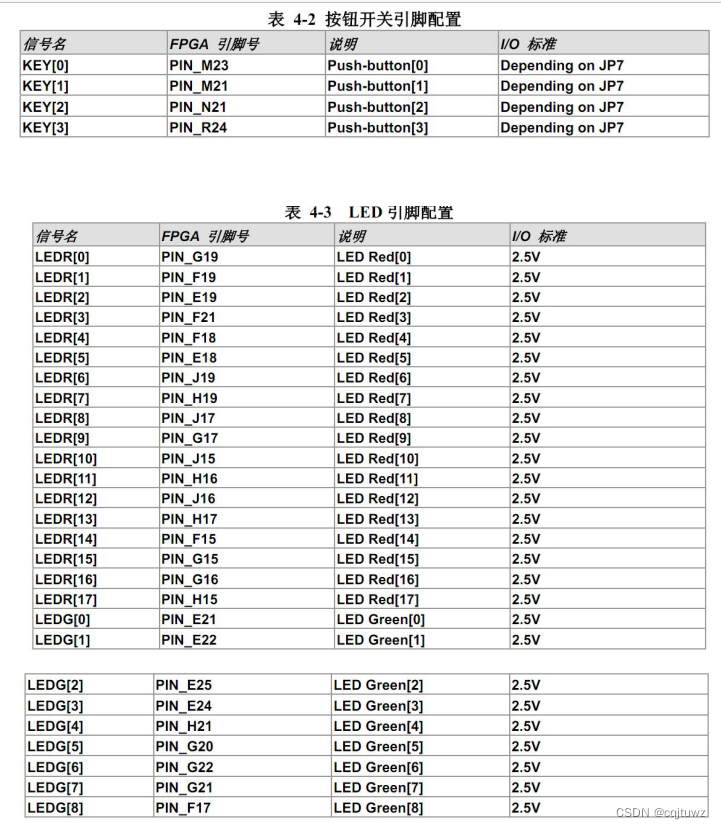

芯片引脚配置表

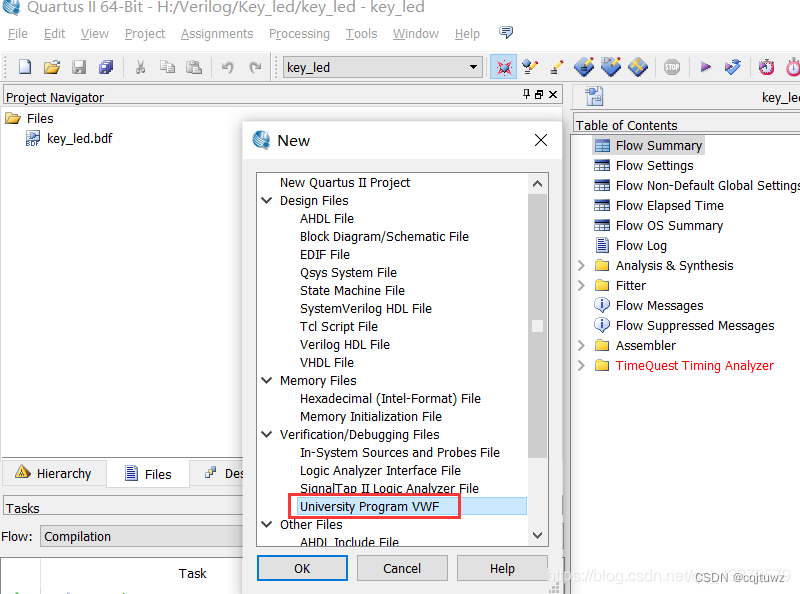

创建一个向量波形文件,选择菜单项 File→New->VWF

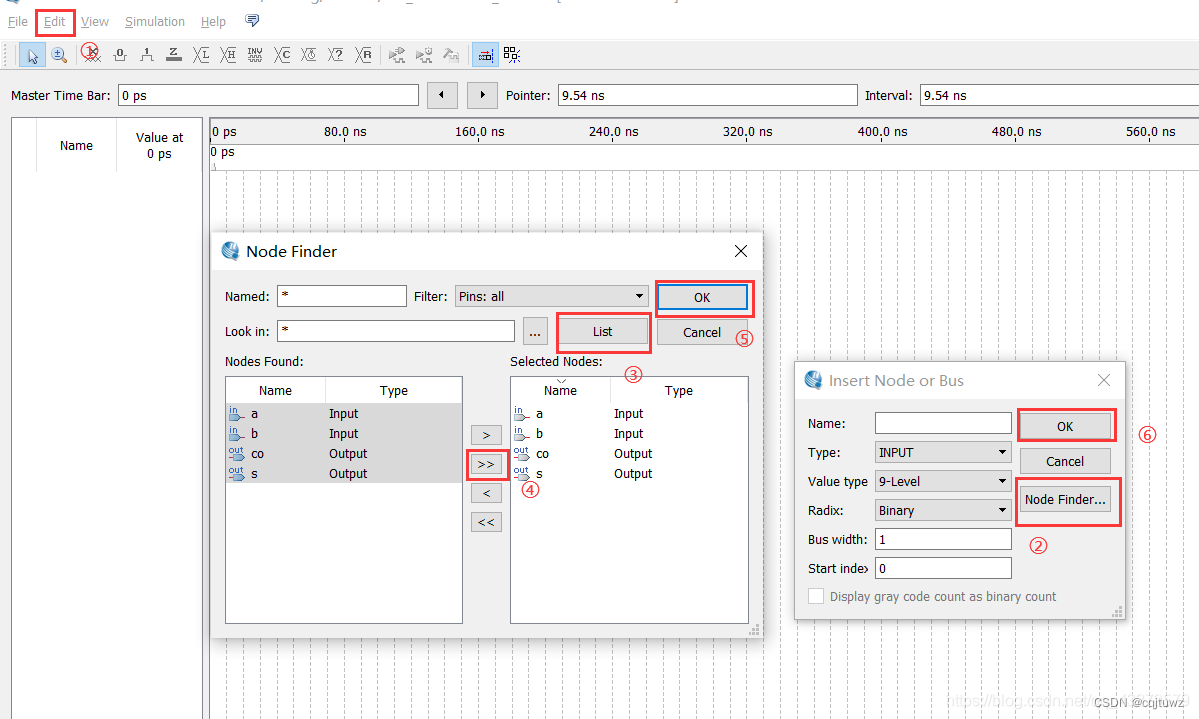

双击左边空白栏,弹出信号窗口,将所有的信号都添加,最后点击OK。

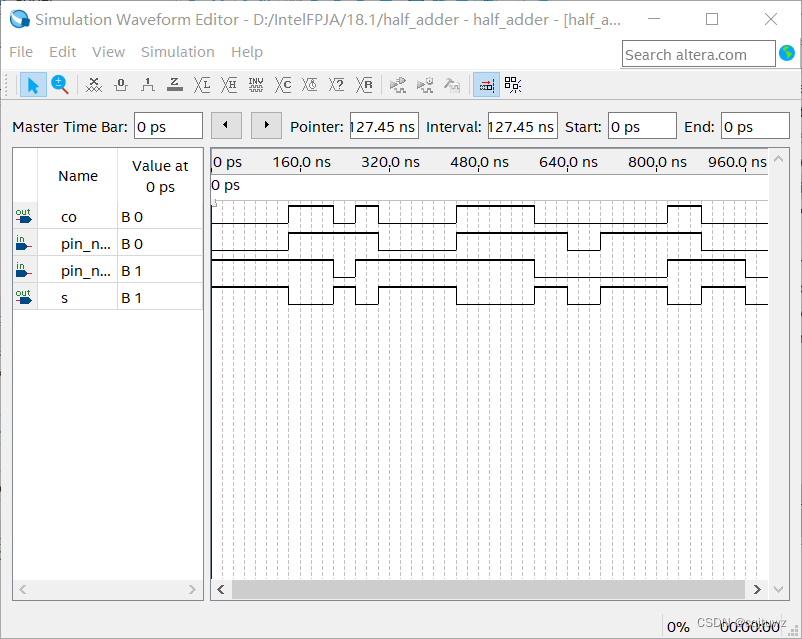

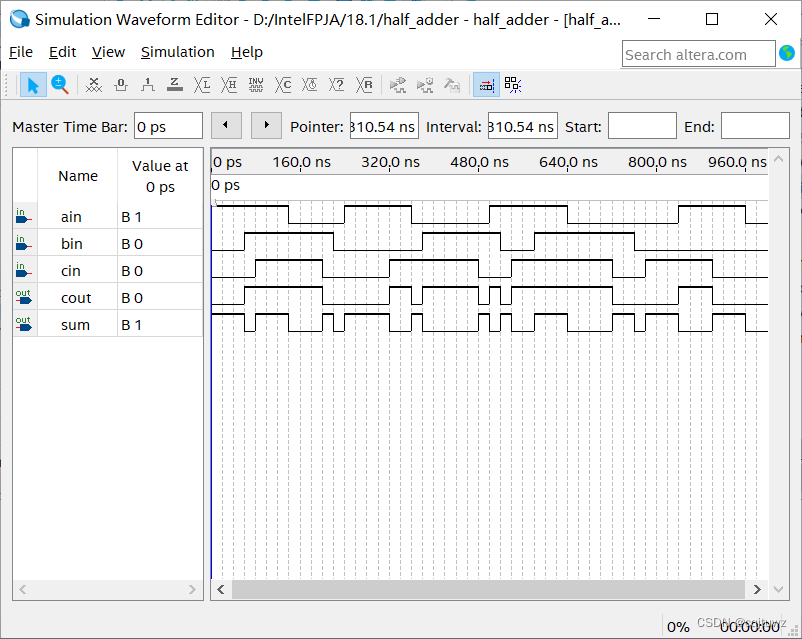

设置好输入信号的高低电频后,开始仿真。仿真结果如下:

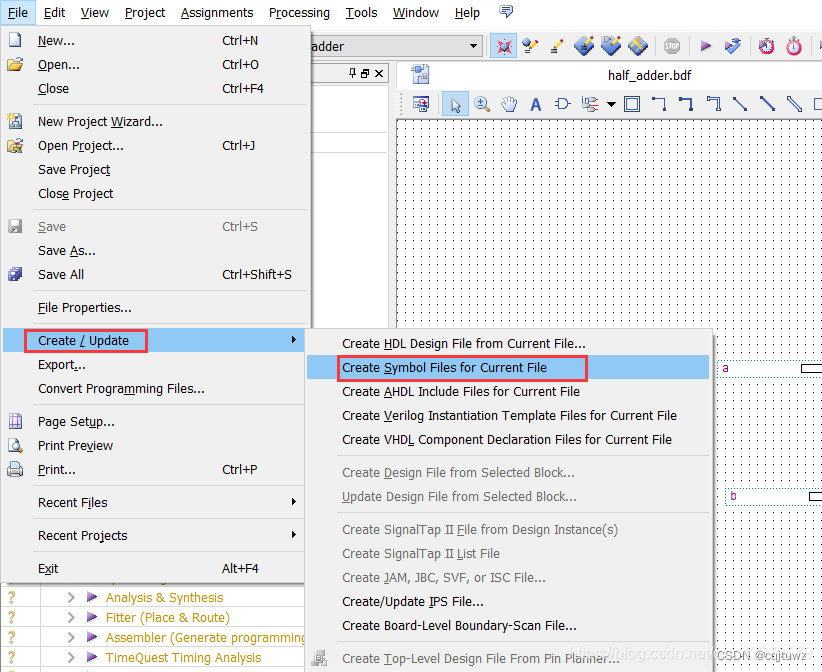

与半加器真值表进行对比,发现符合半加器的原理。说明半加器设计成功。此时就可以通过一下操作将半加器设置为可调用的元件。保存名称为half_adder。

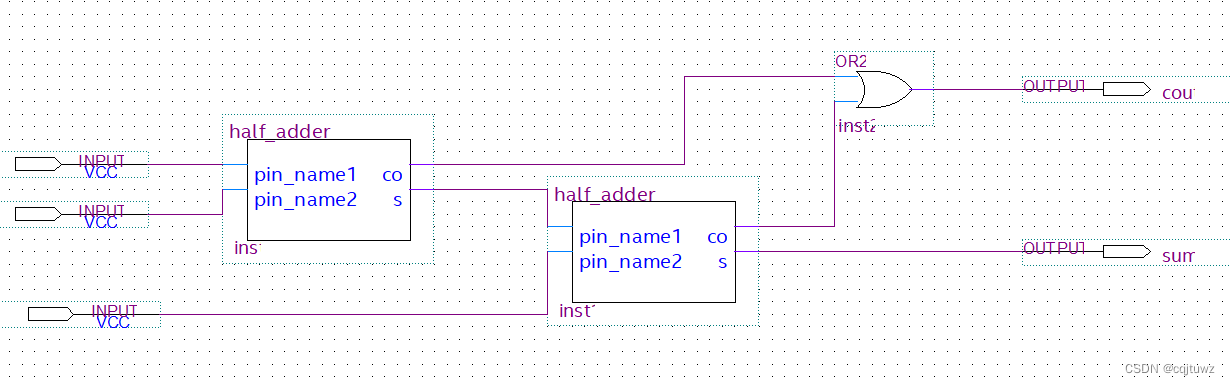

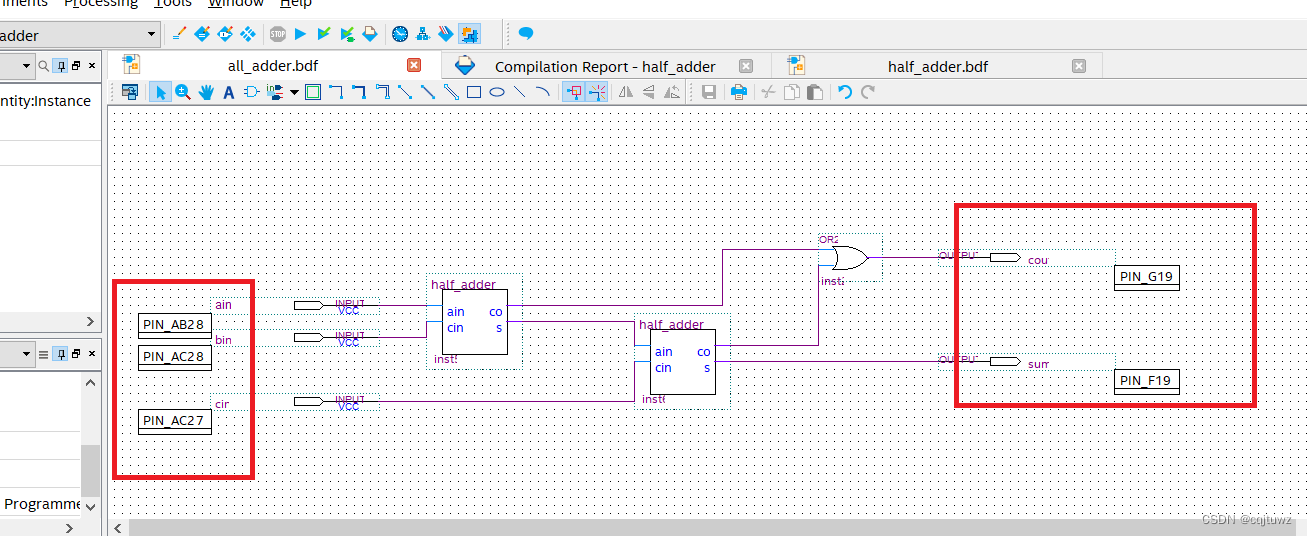

2、利用设计好的半加器设计一位全加器

再安装上述新建一个绘图文件,选择File->New,进入后选择Block Diagram/Schematic File。

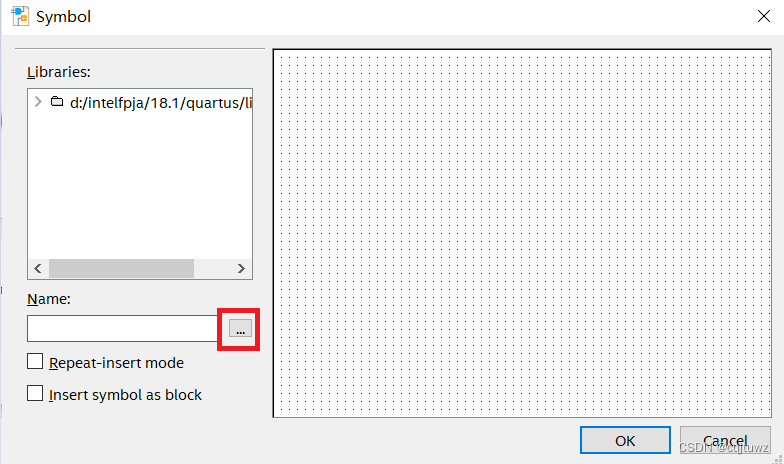

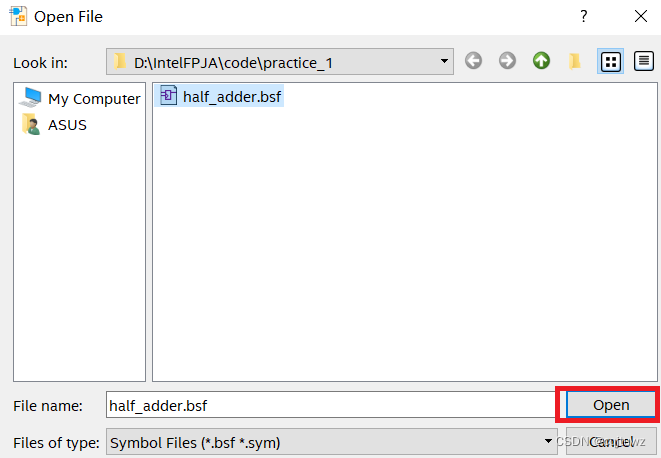

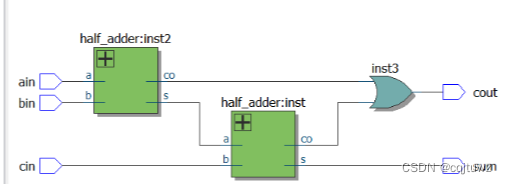

添加刚刚创建好的half_adder元件和基本的元件or2。

按照下图进行设计电路图。

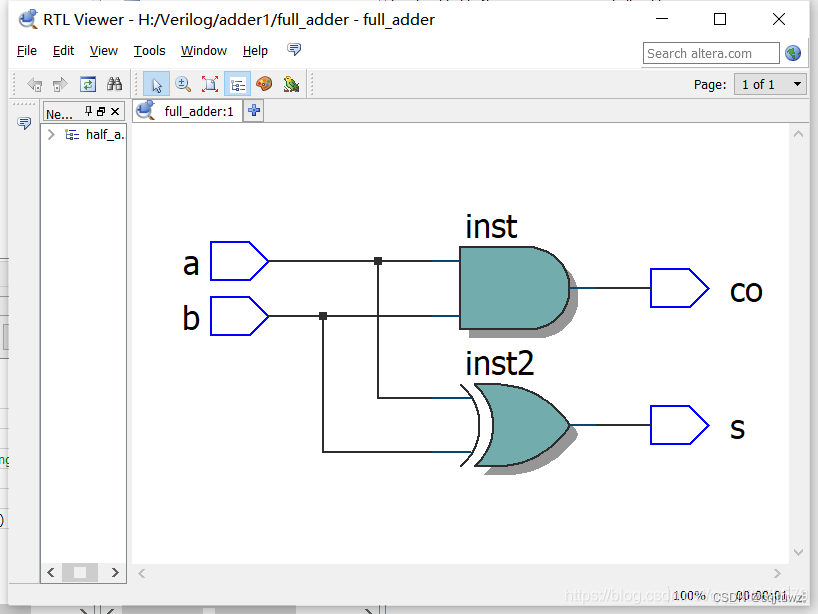

完成后,同样可以通过tool->Netlist Viewers->RTL Viewer查看设计好的电路图

最后进行仿真,结果如下:

对照真值表,发现我们设计的全加器符合其逻辑。

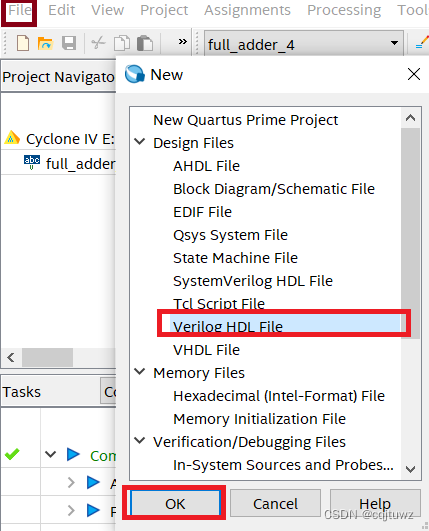

一位全加器的Verilog代码实现

按照上文方法,创建一个项目。并新建一个verilog HDL File文件

在新建的verilog HDL File中编写以下代码:

module full_adder(

//输入信号,ain表示被加数,bin表示加数,cin表示低位向高位的进位

input ain,bin,cin,

//输出信号,cout表示向高位的进位,sum表示本位的相加和

output reg cout,sum

);

reg s1,s2,s3;

always @(ain or bin or cin) begin

sum=(ain^bin)^cin;//本位和输出表达式

s1=ain&cin;

s2=bin&cin;

s3=ain&bin;

cout=(s1|s2)|s3;//高位进位输出表达式

end

endmodule

编写代码完成后,编译通过即可进行仿真对照。

程序烧录验证

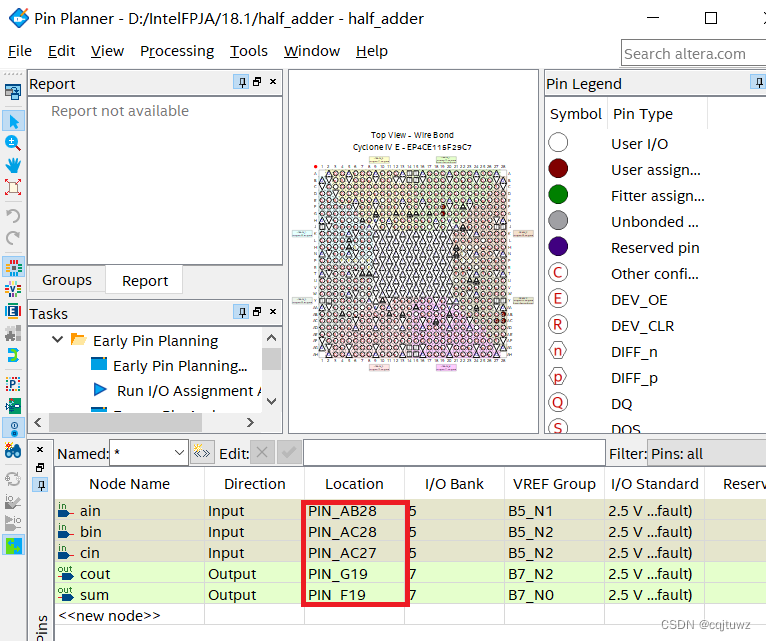

编译通过后,点击Assignments->Pin planner进行输入信号与输出信号的引脚绑定。

引脚绑定时小参考上文芯片引脚配置表。配置结果如下

如果是原理图进行实现的话,绘制的原理图会出现以下变化,输入输出旁边会标注刚刚绑定的引脚编号。

绑定完成后需要再进行一次编译

而后再编译一次。

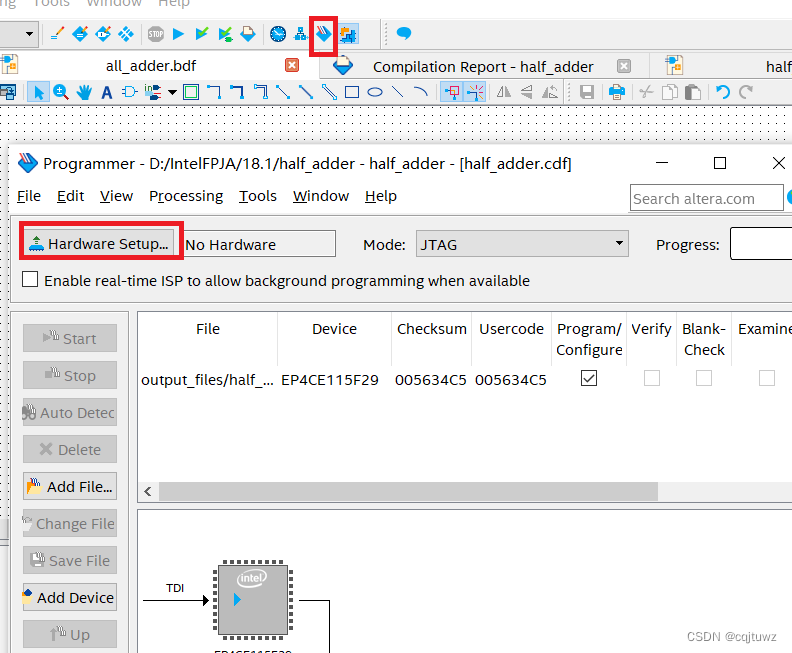

此时就可以将Intel DE2-115开发板通电接上电脑了。

点击下图中上方框选的图标,在弹出窗口中点击Hardware setup 。

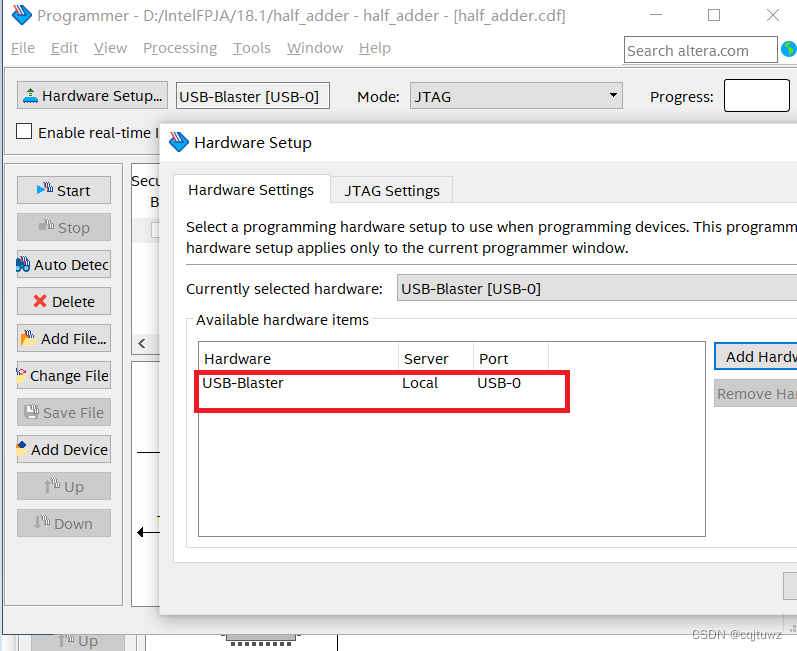

选择好下图中的移动接口,没有这个接口要到在设备管理器中找到加感叹号的USB-blaster设备,并在一下路径下18.1/quatus/drivers/USB-blaster添加驱动。

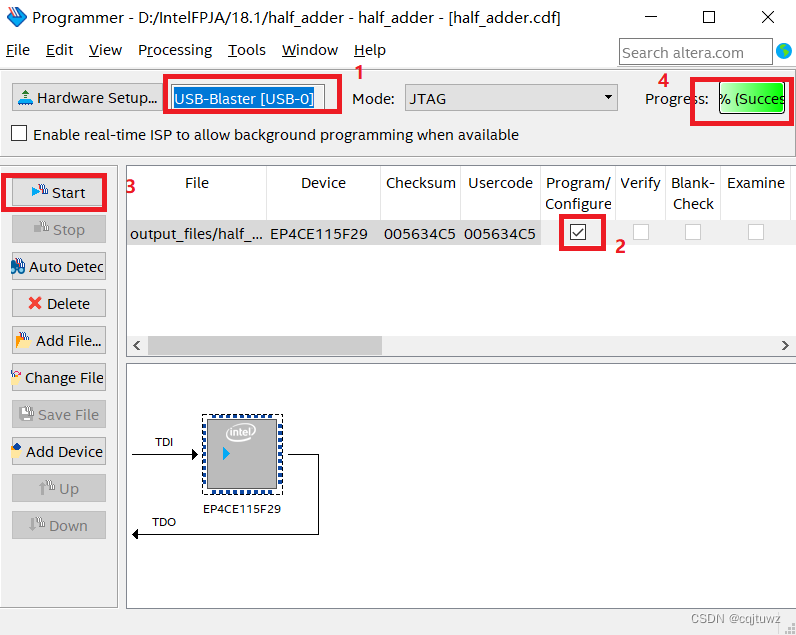

回到上一级菜单,选中以下2框选处,点击start开始烧录。若4处出现success表示烧录成功。

上板结果:

三、四位全加器的实现

四位全加器的原理图实现

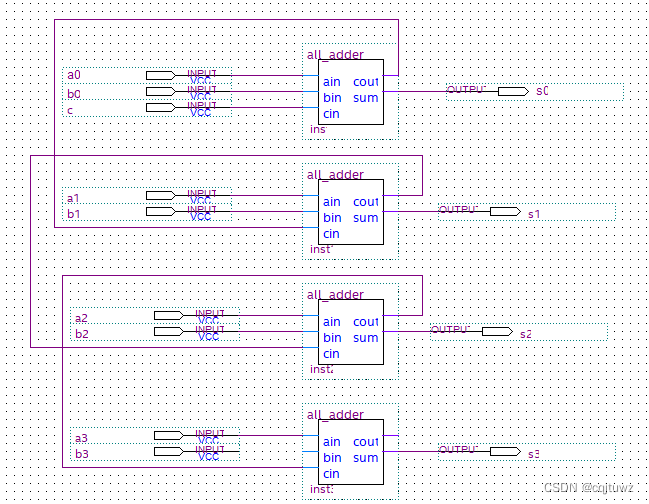

四位全加器是由四个一位全加器组成,因此可以将之前画好的一位全加器设置为可调用的元件并命名为all_adder。

并新建一个项目,如刚刚创建好的可调用元件all_adder,设计一下电路。

再进行仿真,将仿真结果与真值表哦进行对比验证即可。

四位全加器的Verilog代码实现

四位全加器实现verilog代码

module full_adder_4(a,b,cin,cout,sum);

input [3:0] a,b;

input cin;

output [3:0] sum;

output cout;

assign {cout,sum}=a+b+cin;

endmodule

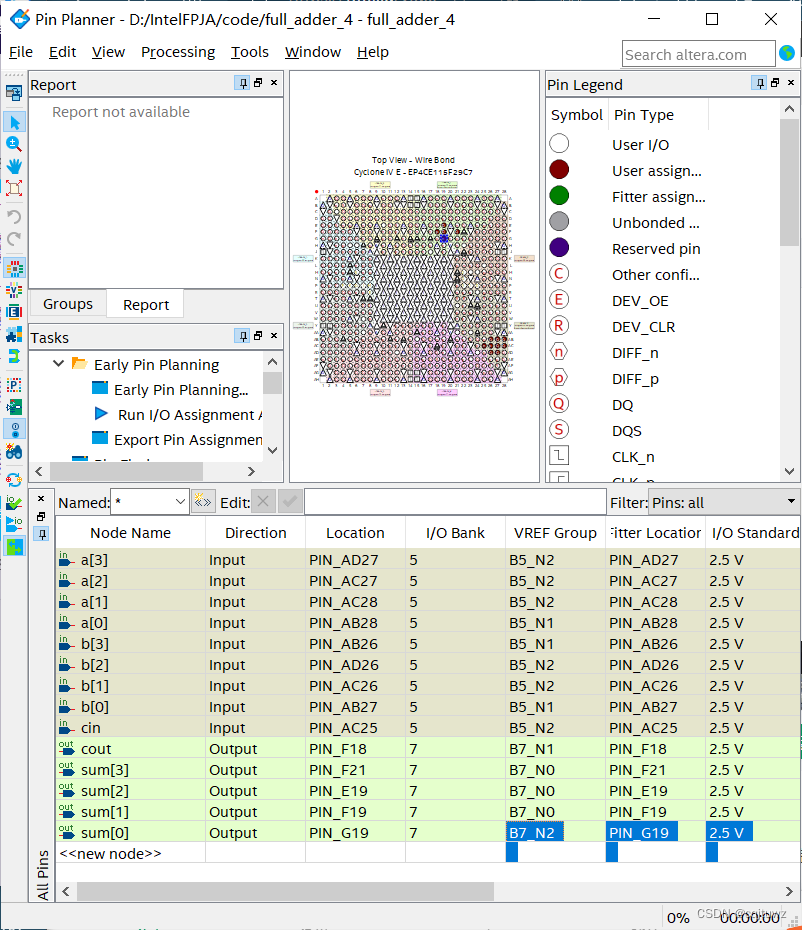

编译通过后,根据引脚配置表和LED配置表进行引脚绑定,绑定如下:

完成后,在进行一次编译,编译无误后即可按照上文所述的方式进行程序烧录。

最后运行结果如下:

错误解决方案

总结

本文主要介绍了半加器,一位全加器,四位全加器的原理及电路图。并使用quratus使用原理图和verilog编程两种方式实现了半加器、一位全加器、四位全加器。并在Intel DE2-115开发板上进行了烧录验证。

6978

6978

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?