一、PWM

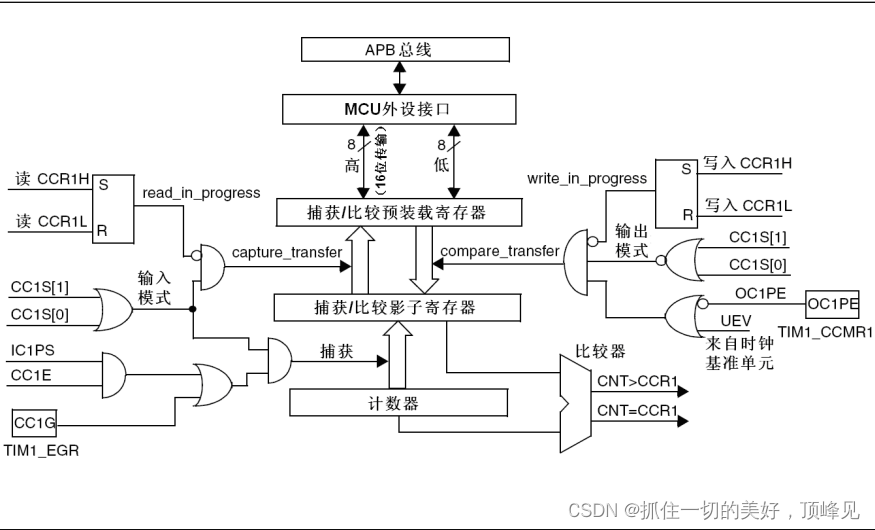

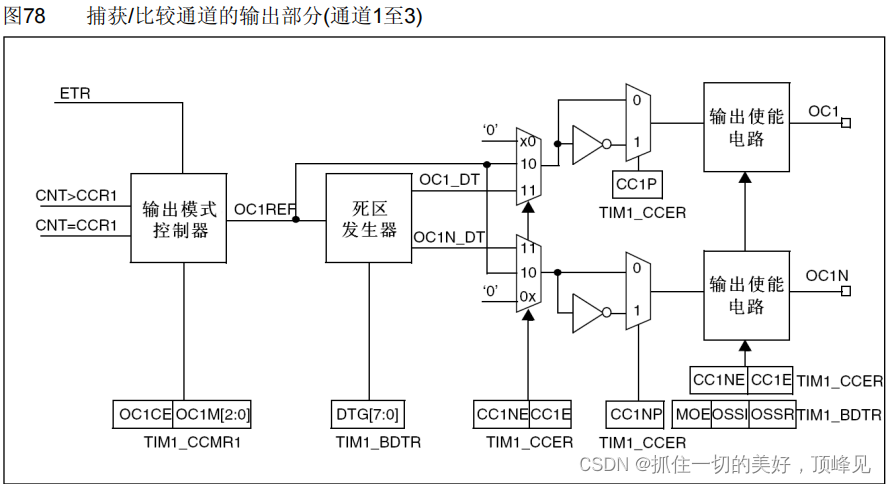

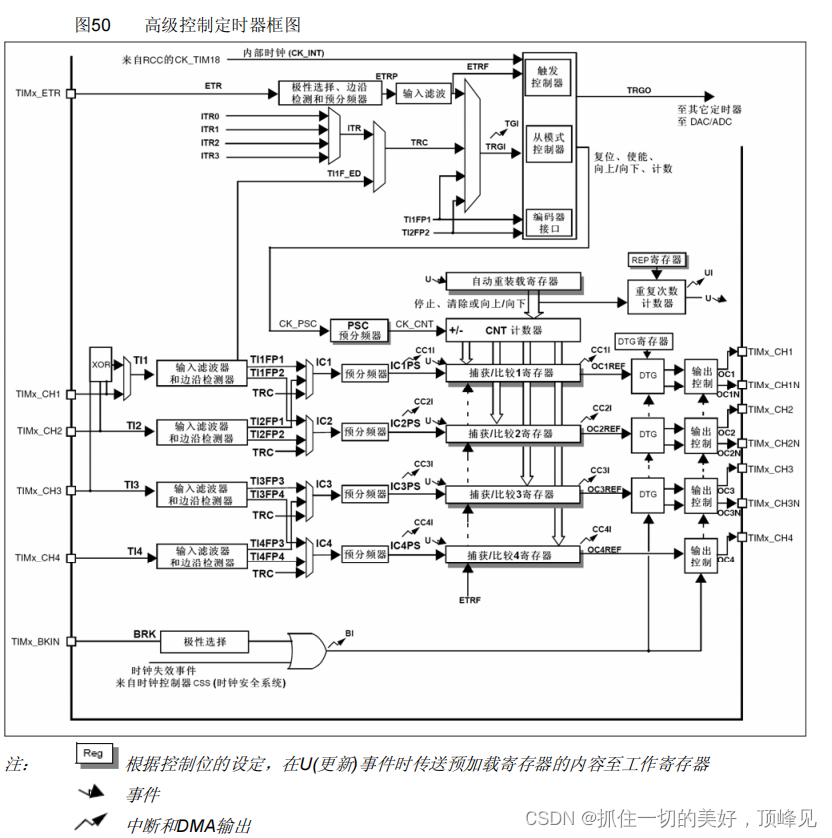

1、框图

- OC(Output Compare)输出比较

- 输出比较可以通过比较CNT和CCR寄存器值的关系,来对输出电平进行置1、置0或翻转的操作,用于输出一定频率和占空比的PWM波形

- 每个通用定时器和高级定时器都拥有4个输出比较通道

- 高级定时器的前三个通道额外拥有死区和互补输出的功能

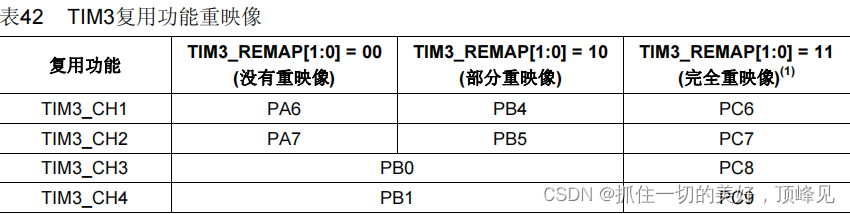

二、TIM定时器映射

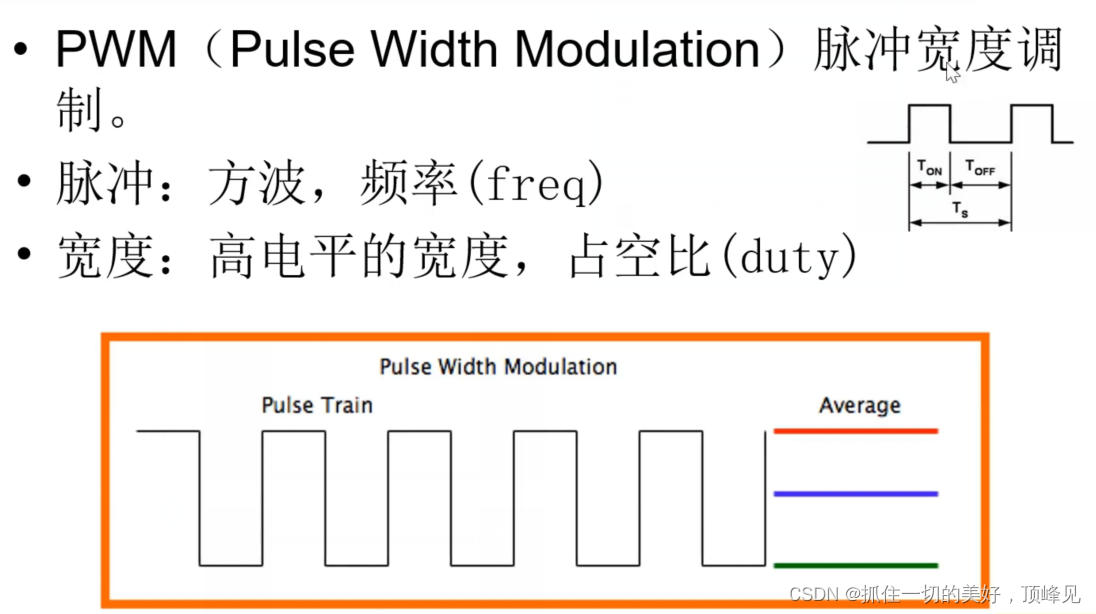

三、pwm介绍

SYSCLK(系统时钟)、 HCLK(由 AHB 预分频器直接输出得到)、 PCLK2(外设时钟,由 APB2 预分频器输出得到)、 PCLK1(外设时钟,由 APB1 预分频器输出得到) 这四个时钟的配置一般是: PCLK2 = HCLK= SYSCLK=PLLCLK = 72MHz, PCLK1=HCLK/2 = 36MHz。这个时钟配置也是库函数的标准配置,我们用的最多的就是这个。

使用的是PWM1模式

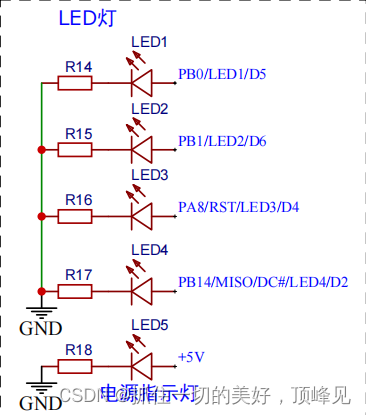

开发板使能的灯是PB1

PB1对应的TIM3_CH4,位于APB1总线,而GPIOB位于APB2总线

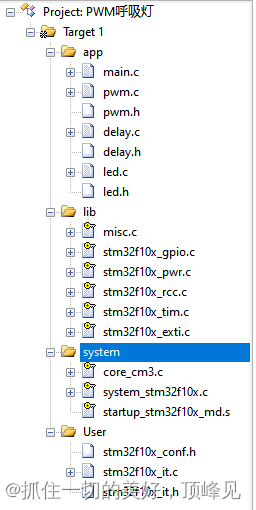

二、主要文件

三、PWM初始化

1、使能P

STM32F10xPWM控制原理与PB1定时器3实例

STM32F10xPWM控制原理与PB1定时器3实例

本文介绍了STM32F10x中PWM的工作原理,使用TIM3定时器的PWM1模式,详细讲解了TIM3_CH4的配置、GPIO设置、预分频计算、计数器模式及代码实现,展示了如何通过C语言控制PB1实现PWM波形输出。

本文介绍了STM32F10x中PWM的工作原理,使用TIM3定时器的PWM1模式,详细讲解了TIM3_CH4的配置、GPIO设置、预分频计算、计数器模式及代码实现,展示了如何通过C语言控制PB1实现PWM波形输出。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3582

3582

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?