重点概述:1.流水线原理与评价;2.流水线阻塞;3.异常与中断;4.流水线优化

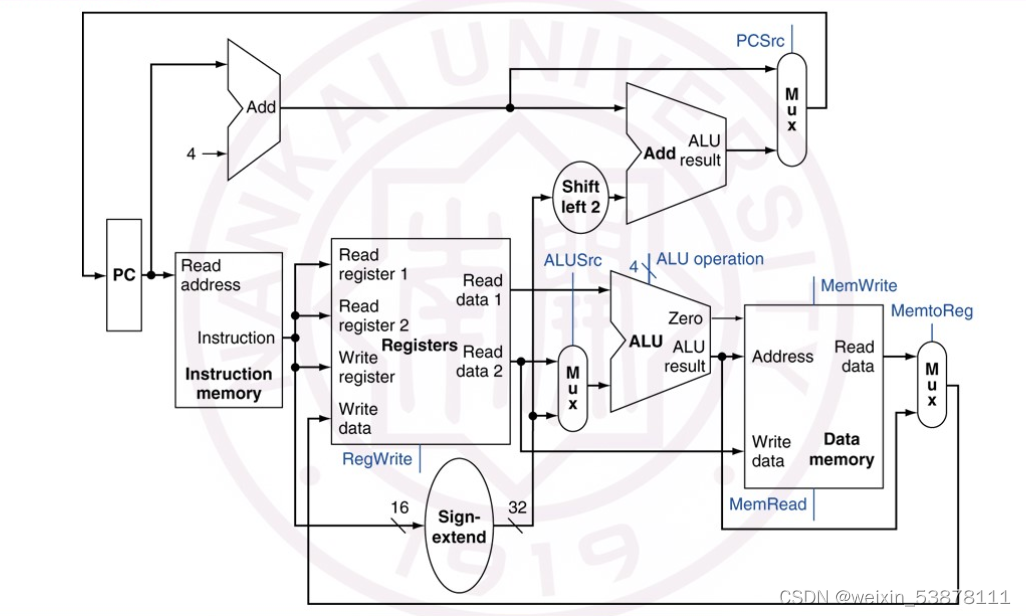

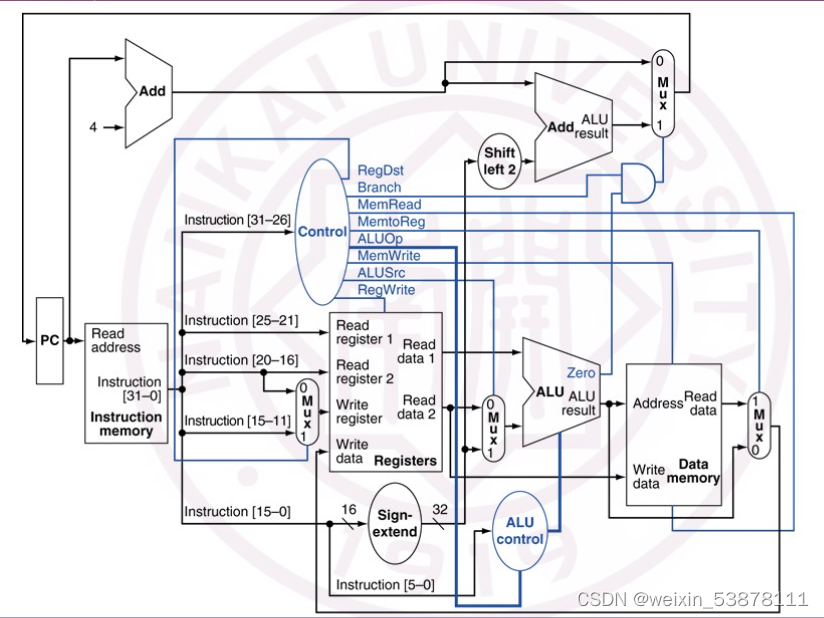

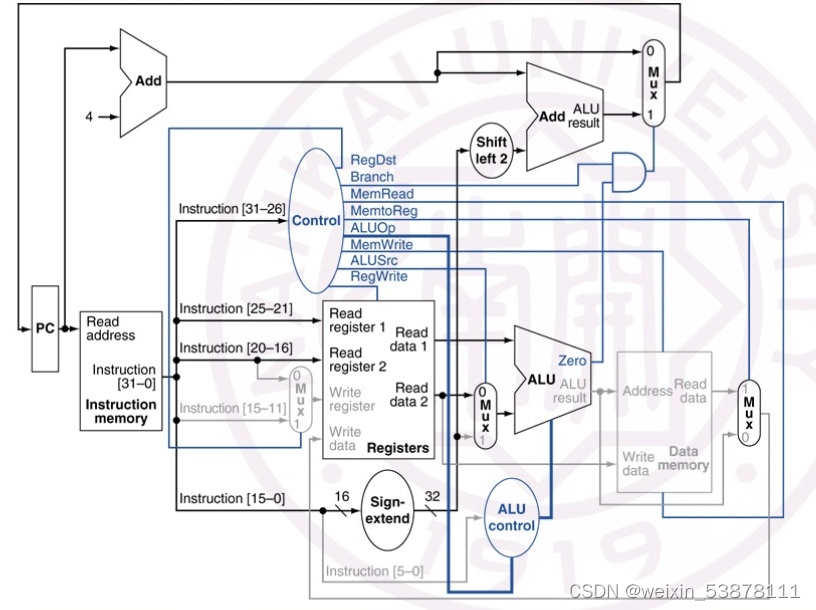

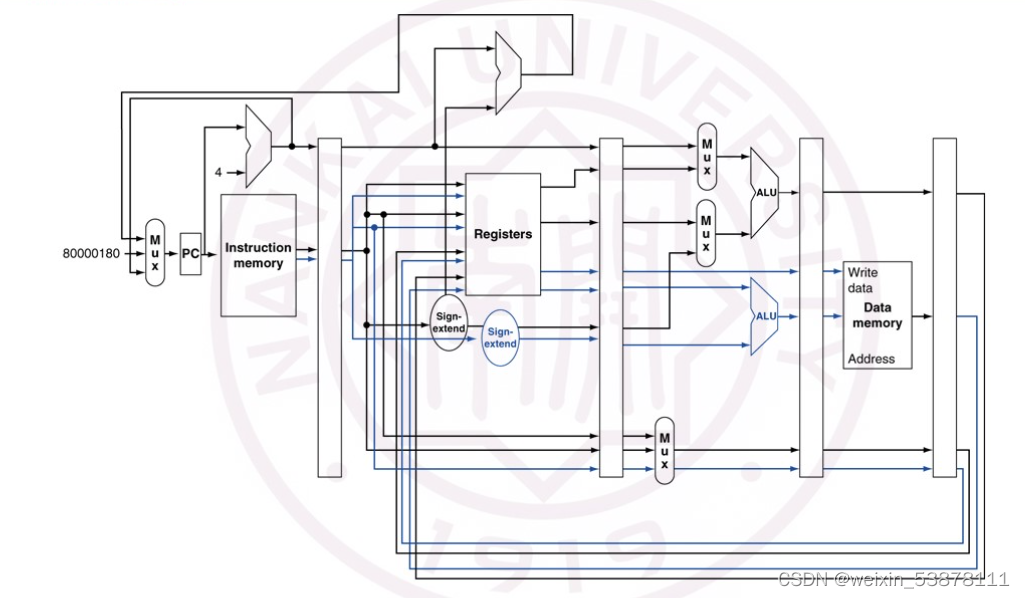

数据通路

PC:程序计数器,存放下一条将要被执行指令的地址的寄存器

寄存器堆:包含一系列寄存器的状态单元,即寄存器集合(*寄存器可以实现在同一时钟周期内读入写出,前半周期写,后半周期读)

控制信号

ALU控制:

根据funt字段和ALUop字段能生成四位的ALU控制信号。

主控制单元:

R型指令数据通路:

(1)从指令存储器取出指令,PC自增

(2)从寄存器堆读出寄存器rs、rt,同时主控制单元计算各控制信号状态

(3)ALU根据funct字段确定ALU功能,对从寄存器读出的数据进行操作

(4)将ALU结果写回寄存器rd

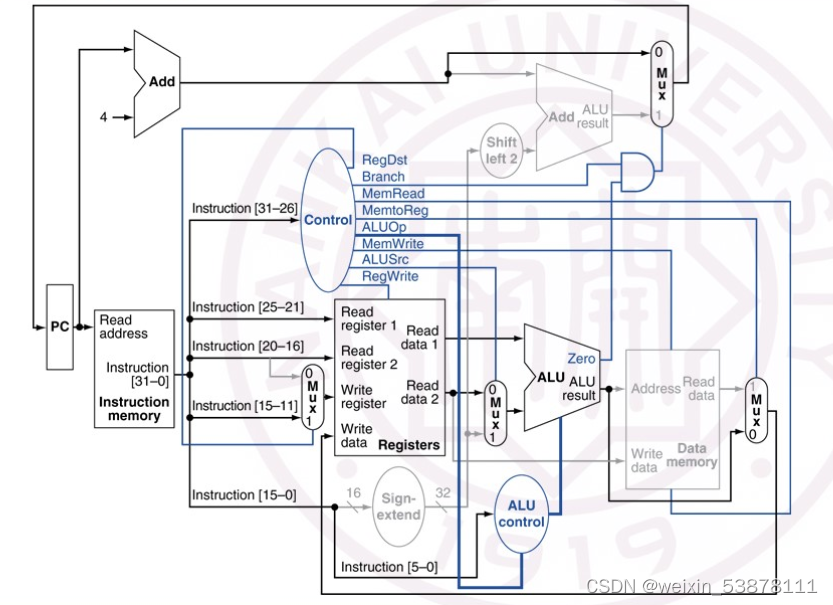

lw指令数据通路:

(1)从指令存储器取出指令,PC自增

(2)从寄存器堆读出寄存器rs,同时主控制单元计算各控制信号状态

(3)ALU将从寄存器读出的值与符号拓展后的指令低16位相加

(4)将ALU结果作为数据存储器的地址,从数据存储器读出目标数据

(5)存储单元数据写入寄存器堆

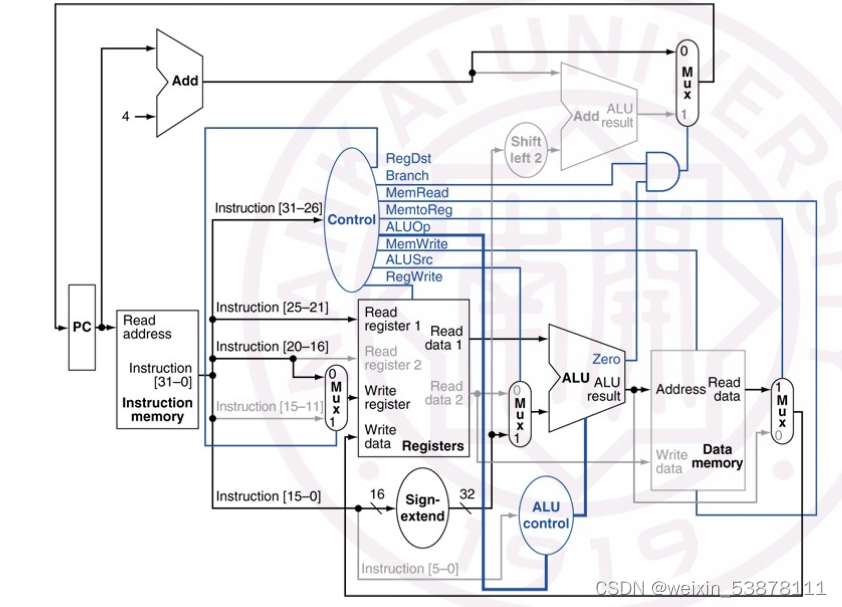

BEQ指令数据通路:

(1)从指令存储器取出指令,PC自增

(2)从寄存器堆读出寄存器rs、rt,同时主控制单元计算各控制信号状态

(3)ALU将从寄存器堆读出的两数相减。PC+4的值与符号拓展并左移2位后的指令低16位相加,结果就是分支目标地址

(4)根据ALU的零输出决定哪个加法器的结果存入PC

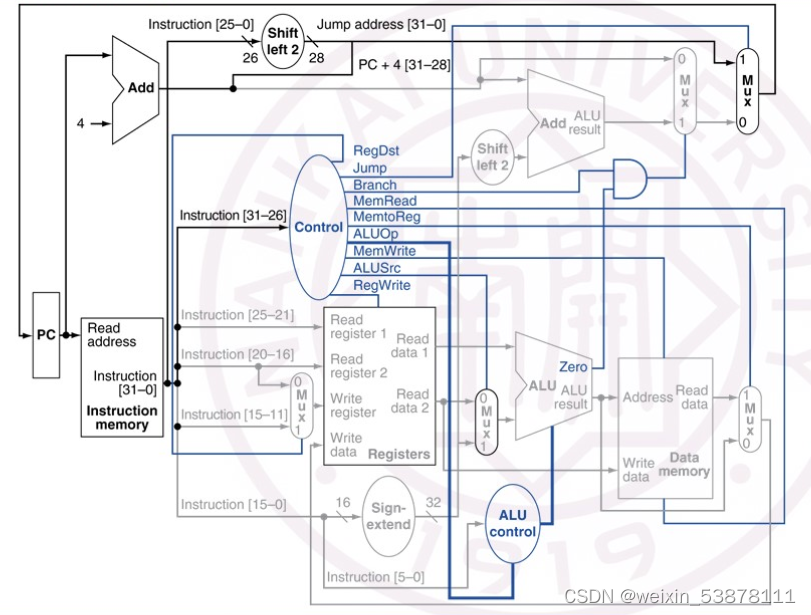

JMP数据通路:

单周期的处理器,时钟周期对所有指令等长,这样时钟周期要由执行时间最长的那条指令决定。

流水线(重点)

pipelining,一种实现多条指令重叠执行的技术

- IF:从指令存储器中读取指令

- ID:指令译码的同时读取寄存器

- EX:执行操作或计算地址

- MEM:从数据存储器中读取操作数

- WB:将结果写回寄存器

流水线多周期CPU的时钟周期必须能够满足最慢操作的执行需要。

指令执行时间(流水线)=指令执行时间(非流水线)/流水线级数理想情况且有大量指令的情况下,流水线所带来的加速比与流水线的级数近似。(为什么不是越长越好?功率限制,流水线越长,功率越高)

流水线所带来的性能提高是通过增加指令的吞吐率,而不是减少单条指令的执行时间

流水线冒险

- 结构冒险。因缺乏硬件支持而导致指令不能在预定的时钟周期内执行的情况。(例:存储器数量不够的限制)

- 数据冒险。因无法提供指令执行所需数据而导致指令不能在预定的时钟周期内执行的情况。一般是由于一条指令依赖于更早的一条还在流水线中的指令造成的。解决办法:旁路。从内部寄存器或存储器中提前取出数据。但是无法完全解决取数-使用型数据冒险,此时不得不使用流水线阻塞(气泡法)。考点:重新安排指令顺序避免数据冒险。

- 控制冒险。分支冒险,因为取到的指令不是需要的。解决办法:1)阻塞;2)预测

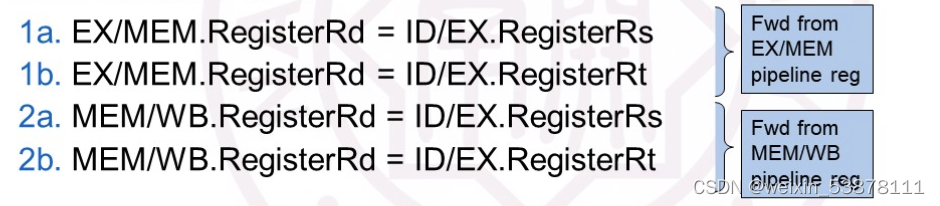

如何检测数据冒险的发生?

还需要检测RegWrite信号是否有效。

缓存寄存器,用于实现流水线通路,IF/ID ID/EX EX/MEM MEM/WB

流水线控制信号也保存在缓存寄存器(流水线寄存器)中,在译码阶段生成放入ID/EX流水线寄存器,每个流水集使用对应的控制信号,并将剩余信号传递到下一个流水极。

如何阻塞?通过识别ID级的冒险,可以在流水线插入一个气泡,把ID/EX流水线寄存器的EX、MEM、WB级的控制信号都置为0.

当分支到达MEM级时才知道分支结果,分支冒险中的丢弃指令意味着将流水线的IF、ID、EX级别的指令都清除(flush)。分支执行能提升到ID级,减少分支延迟。

异常与中断

内部:异常;外部:中断

异常发生时,EPC(异常程序计数器)保存出错指令的地址,并将控制权交给操作系统的指定地址。

处理异常:1.MIPS用状态寄存器(Cause寄存器)记录异常产生的原因。

2.向量中断。由异常原因决定中断控制转移地址的中断。控制权被转移到由异常原因决定的地址处,由一个中断向量表指出异常处理地址。

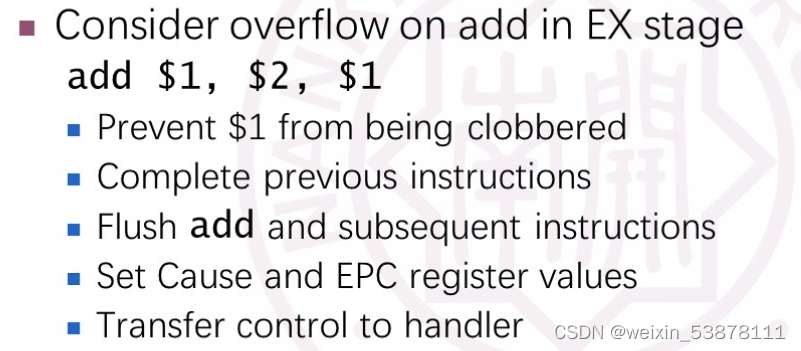

流水线异常和中断处理步骤:

同时出现多个异常?对异常划分等级,在大多数MIPS中硬件对异常进行排序从而使得最先发生溢出的指令被中断。不同异常发生在不同流水级,如果在Cause寄存器中保存多个异常,应当优先处理优先级最高的异常,之后继续导致硬件中断从而处理后面的异常。

流水线优化

指令级并行:1.增加流水线深度以重叠更多指令;2.复制计算机内部部件数量,使得每个流水级可以启动多条指令,*多发射。静态多发射和动态多发射:静态多发由编译器组织打包指令到发射槽,由编译器处理冒险;动态多发由CPU在执行阶段进行决策,CPU负责解决冒险,也称为超标量。

VLIW:超长指令字,不等同于静态多发。

静态双发射的数据通路,主要是:指令存储器额外的32位输出;寄存器堆多出的两个度端口一个写端口;一个额外的ALU进行地址计算。

提交单元:位于动态流水线和乱序流水线中的一个单元,用以决定何时可以安全地将操作结果送至程序员可见的寄存器和存储器;

保留站:功能单元的缓冲区,用于保存操作数和操作;

重排序缓冲区:动态调度处理器中用于暂时保存执行结果的缓冲区,等到安全时才将其中结果写回寄存器或存储器。

3228

3228

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?