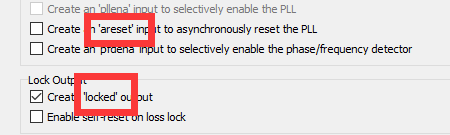

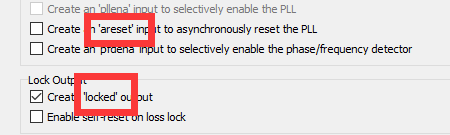

使用pll时的两个信号areset和locked。

areset 异步复位选项,对pll进行复位,高电平有效。

locked 锁定信号,用于检测锁相环是否已经锁定,锁定时,locked信号就变为高电平,表示输出的时钟是可用的,在调试过程中使用这个信号可以很好的观察时钟

FPGA学习记录——pll中的areset信号和locked信号

于 2022-01-15 19:28:34 首次发布

使用pll时的两个信号areset和locked。

areset 异步复位选项,对pll进行复位,高电平有效。

locked 锁定信号,用于检测锁相环是否已经锁定,锁定时,locked信号就变为高电平,表示输出的时钟是可用的,在调试过程中使用这个信号可以很好的观察时钟

2058

2058

2843

2843

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?