1.问题

在实际应用中发现使用PLL产生的locked信号与PLL产生的不同频率输出时钟信号是不同步的,即可以理解为PLL输出的locked信号与PLL输出不同频率时钟信号为异步关系,所以在使用locked作为多个时钟驱动模块的复位信号时,需要做异步复位同步释放的处理。

2.问题仿真

调用Xilinx PLL IP核,输入时钟40Mhz,输出40MHz、80MHz、90MHz、100MHz和120MHz,仿真图如下:

可以看出locked信号和clk_100m信号是异步关系。

3.解决方案

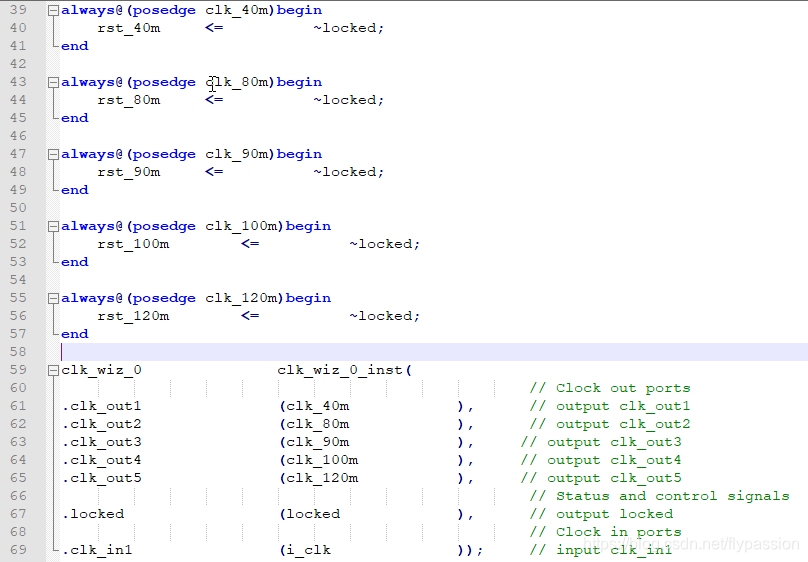

采用异步复位,同步释放,其实就是跨时钟域信号处理,使得各个时钟模块的使能信号和各个驱动时钟同步,提高代码质量。部分代码如下(确保输出的时钟和对应的复位信号同步):

仿真图如下:

从仿真图可以看出,经过处理之后的各个时钟及其所对应的复位信号是同步的,这样就解决了不同时钟信号和locked作为复位信号不同步的问题。

802

802

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?