转自:http://www.360doc.com/content/13/0509/20/9072830_284220258.shtml

今天对PLL中areset和locked详细查了下资料,发现网上这方面的资料很少,所以自己认真读了下Documentation---ug_altpll.pdf,现在我将我学到的内容总结如下:

areset简而言之就是高电平有效,对pll进行复位。

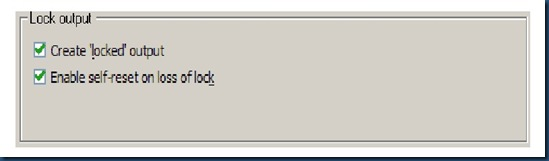

下面我们主要来认识一下locked信号:

Locked这个输出到底是干嘛用的呢,pdf中这样写道:

The ALTPLL megafunction allows you to monitor the PLL locking process using a lock signal named locked and also allows you to set the PLL to self-reset on loss of lock.

原来这Locked信号是用来观察pll输出时钟是否和输入时钟锁定。当锁定时,这个Locked信号就变为高电平。

但pdf中又这么写道:

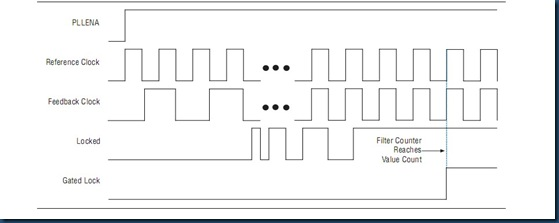

The locked signal might toggle as the PLL begins tracking the reference clock. To avoid such a false lock indication, use a gated lock signal.

当这个pll刚开始跟踪输入时钟时这个Locked信号又可能会发生跳转,为了避免这种错误的指示,我们就使用gated lock信号。这个gated lock信号其实和locked信号是同一个,locked信号多了个计数功能后就叫做gated lock了。

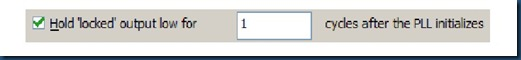

You must specify the number of PLL input clock cycles to hold the locked signal low after the PLL is initialized

就是在pll被初始化之后,让gated lock依旧保持低电平多少个周期,以此来解决下面图片中的问题:

这图片中locked在pll开始跟踪输入时钟的时候一直在抖动,而gated lock因为设置了上面周期后,开始阶段始终为low,直到到达counter值后变为高电平,这就避免了locked的抖动。所以gated lock信号更加稳定。

这个时钟周期怎么算呢,如下:

To calculate the number of clock cycles needed, you must know the maximum lock time of the PLL, and the period of the PLL input clock. The lock time of the PLL is listed in the “PLL Timing Specifications” section of the DC & SwitchingCharacteristics chapter of the device handbook. The period of the PLL input clock is user-specified. For example, if the maximum lock time of a PLL is 1ms,and its input clock frequency is 100 MHz which corresponds to a 10 ns clock period, you calculate the value of the gated lock counter, by dividing 1 ms by 10 ns. The result is 100,000 clock cycles. 这个我就不解释了,大家自己看吧,很容易理解的。

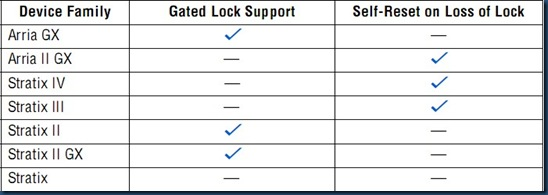

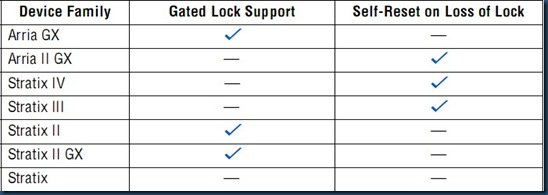

不同器件类型对gated lock和self-reset的支持情况不一样

转载于:https://www.cnblogs.com/kybyano/p/8271229.html

922

922

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?