问题1,新建差分走线类

问题2,差分走线间距与普通走线间距冲突

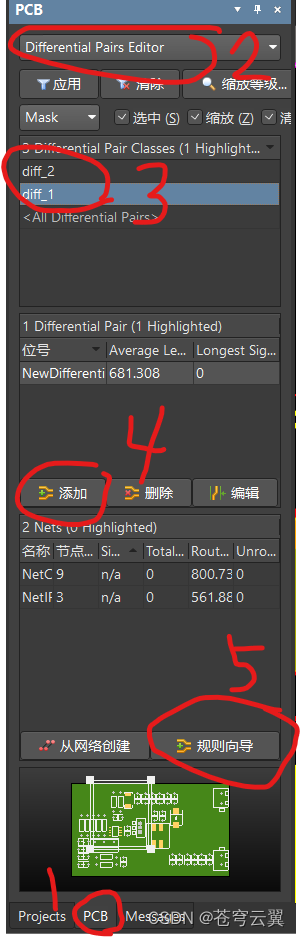

1,新建差分走线类:在panels打开PCB——选择Differential Pairs Editor——新建差分类别——为差分类别添加成对的网络——新建差分规则

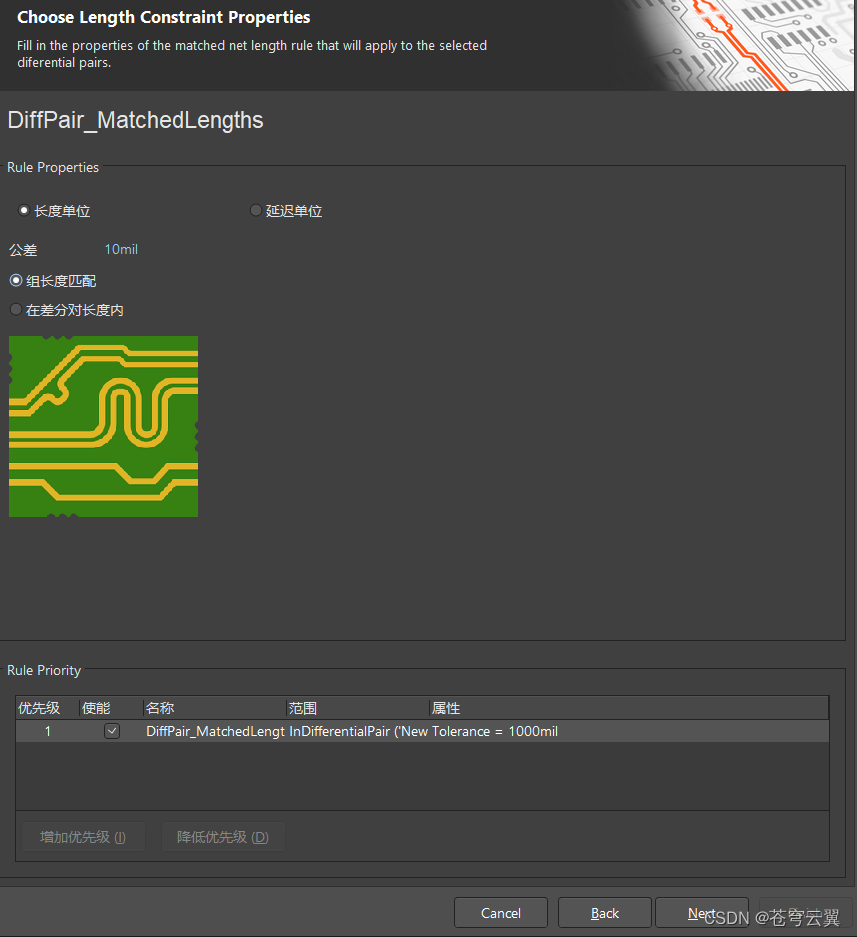

公差选择10mil

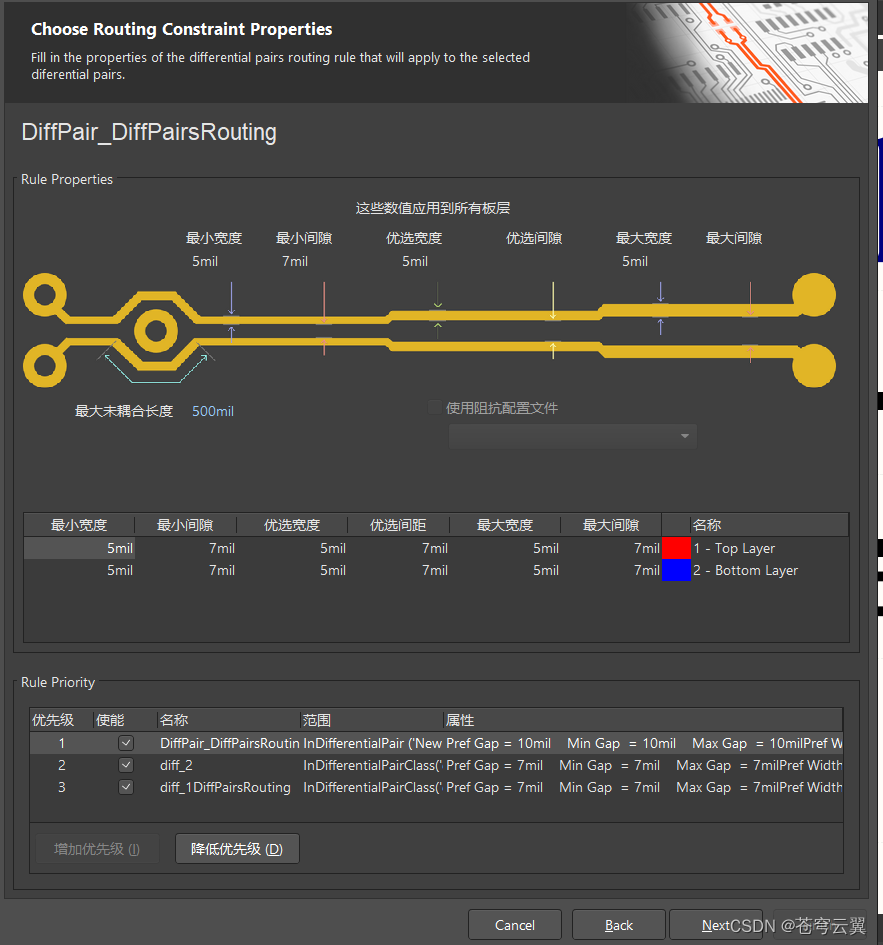

默认100欧姆的差分规则5mil/7mil

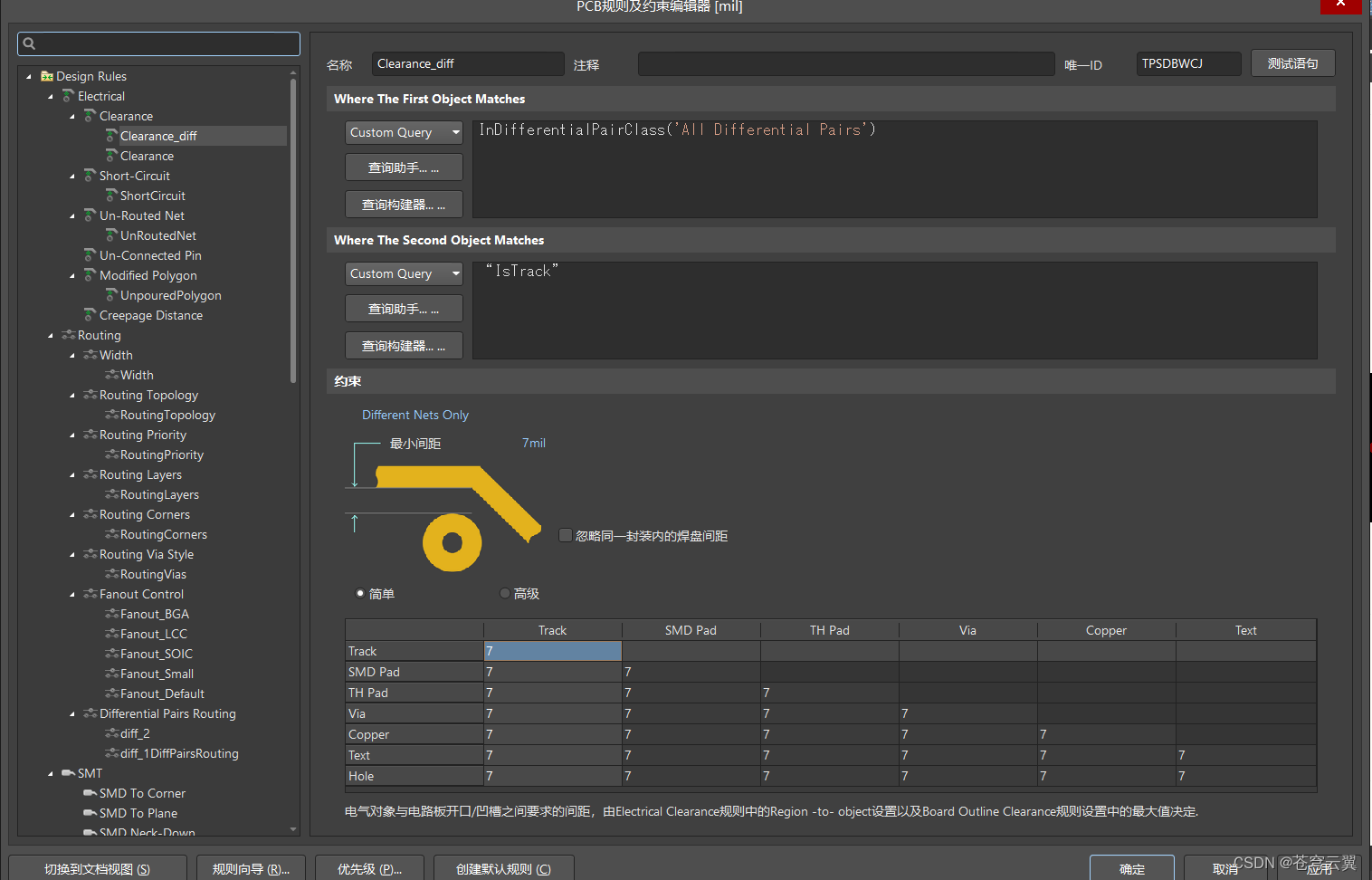

2,间距冲突

在规则里新建一个规则,并将其优先度置于最前。设置第一个目标为所有差分网络,即“ InDifferentialPairClass('All Differential Pairs') ”,第二个目标为走线,即 “IsTrack” ,然后将二者之间的所有间距规则都改为7mil。

报错小结:因为有一根线需要调整位置,重新更新网表后,发现原来布好的差分线却报错了?!原因是因为,重新更新网表后,之前在PCB中设置的差分类别都被覆盖了,所以DRC没有检测到差分类别就报错了。查找了网上发现是现在的这种画图的思维存在bug:“

- 印象最深刻的错误是差分规则的创建引起的错误。目前网络所能查到的差分规则创建方法(除官网)都是基于PCB 编辑下,利用手动输入差分网络进行分类配对,创建差分线相关的规则参数。这样做其实是错误的,如果这样做,那么原理图每更新一次网表到PCB时都会要手动选择多次是否删除差分类或组。实际上很多使用者,在导入网表时直接就选择了更新网表选项。这样所有的差分类都会删除,到最后的DRC检验时就会找不到差分规则而不报错。或者说误报。

”

参考一位博主Bob_bate的文章

关于Altium Designer 差分线规则设置的方法纠偏_ad中的差分对在原理图中label需要改变吗-CSDN博客

340

340

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?