SDA

- System Management I2C serial data. This signal provides a data line for a twowire serial management bus.

RES0, RES1

– These are reserved pins and are left unconnected by the IO Mezzanine module and the carrier card.

GND

– This is signal ground

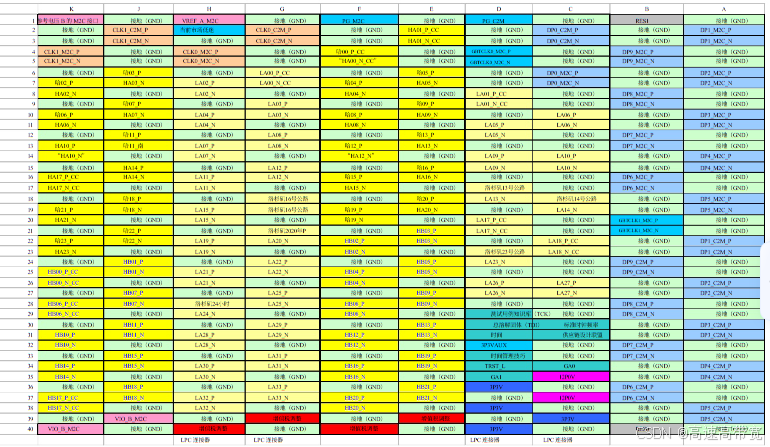

四:管脚规则

Rule 5.1:

Signal assignment for high-pin count connector shall be defined

as shown in Table 2.

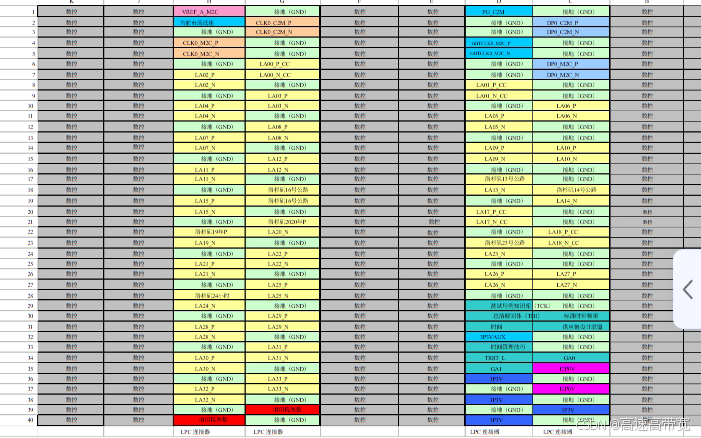

Rule 5.2:

Signal assignment for low-pin count connector shall be defined as

shown in Table 3.

Observation 5.1:

Rows A through to Row K are associated with the high

pin count connectors.

Observation 5.2:

Rows C, D, G, and H are the only rows associated with

the low-pin count connectors.

Observation 5.3:

Signal names with ‘C2M’ indicate that the signal is

driven by the carrier card and received by the IO mezzanine module

Observation 5.4:

Signal names with ‘M2C’ indicate that the signal is

driven by the IO mezzanine module and received by the carrier card

Observation 5.5:

The postfix ‘_P’ on a differential signal pairs, indicates

the positive component of a differential signal

Observation 5.6:

The postfix ‘_N’ on a differential signal pairs, indicates

the negative component of a differential signal

Observation 5.7:

The postfix ‘_L’ on a single ended signal,

‘PRSNT_M2C_L’ and ‘TRST_L’ indicate that these are active low signals.

Recommendation

5.1:

Signals with a ‘_CC’ postfix should be used as the

preferred signals for clocks in source synchronous applications and should

be connected to pins on the FPGA, which are identified for this purpose

五:用户自定义管脚

LA[00..33]_P, LA[00..33]_N

- These signals are arranged as differential pairs with signals having the ‘_P’ postfix representing the positive component and signals with ‘_N’ postfix representing the negative component.

HA[00..23]_P, HA[00..23]_N

- These signals are arranged as differential pairs with signals having the ‘_P’ postfix representing the positive component and signals with ‘_N’ postfix representing the negative component.

HB[00..21]_P, HB[00..21]_N

- These signals are arranged as differential pairs with signals having the ‘_P’ postfix representing the positive component and signals with ‘_N’ postfix representing the negative component.

六:用户自定义管脚规则

Rule 5.3:

Pins with a LA or HA prefix shall use the signaling standard

associated with ‘Bank A’ and can use the reference voltage on pin

‘VREF_A_M2C’.

Rule 5.4:

Pins with a HB prefix shall use the signaling standard associated

with ‘Bank B’ and can use the reference voltage on pin ‘VREF_B_M2C’.

Rule 5.5:

Pins with a L prefix shall have connector contacts populated in

the low-pin and high-pin count connectors.

Rule 5.6:

Pins with a H prefix shall have connector contacts populated only

in the high-pin count connector.

Rule 5.7:

The high-pin count connector shall support 160 single-ended user

defined signals; or 80 differential user defined signals.

Rule 5.8:

The low-pin count connector shall support 68 single-ended user

defined signals; or 34 differential user defined signals.

Rule 5.9:

The FMC User Defined signals in Bank A shall tolerate signal

levels from -300mV to VADJ + 300mV.

Rule 5.10:

Neither the carrier nor the mezzanine module shall generate

signals outside the range of -300mV to VADJ + 300mV signal levels on the

user defined signals in Bank A.

Rule 5.11:

The FMC User Defined signals in Bank B shall tolerate signal

levels from -300mV to VIO_B_M2C + 300mV.

Rule 5.12:

Neither the carrier nor the mezzanine module shall generate

signals outside the range of -300mV to VIO_B_M2C + 300mV signal levels

on the user defined signals in Bank B.

Rule 5.13:

A minimum of no user defined signals shall be supported by this

standard.

Rule 5.14:

A maximum of 160 user defined signals shall be supported this

standard.

Permission 5.1:

Any number of user defined pins may be connected on the

FMC module or FMC carrier card.

Rule 5.15:

The user defined signals on Bank A shall be assigned starting

with the lowest ordinal in the LA group and used in ascending order. This

will be followed by signals with the lowest ordinal in the HA group and

used in ascending order.

Rule 5.16:

The user defined signals on Bank B shall be assigned starting

with the lowest ordinal in the HB group and used in ascending order.

Rule 5.17:

If an odd number of signals are assigned in Bank A or Bank B

then the ‘_P’ signal shall be populated in preference to the ‘_N’ signal.

Permission 5.2:

Bank A and Bank B may be populated independently.

Permission 5.2:

To maximize signal integrity, the LA signals should be

fully populated and then HA and HB should be populated in the same ratio

of their maximum.

Recommendation 5.3:

When signals are routed differentially each pair

should provide a differential impedance of 100Ω +/- 10%

Recommendation 5.4:

When signals are routed single ended each signal

should provide an impedance of 50Ω +/- 10%

Observation 5.8:

To maximize compatibility between mezzanine modules

and carrier cards, the LVDS and LVTTL signaling standards should be the

preferred choice.

Observation 5.9:

To maximize the performance of data buses located on

the user defined pins, the skew between user defined pins should be keep to

a minimum. The skew should be less that 10% of the targeted unit interval,

UI for the data rates on the pins. Table 4 provides examples of times for

targeted data rates.

2399

2399

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?