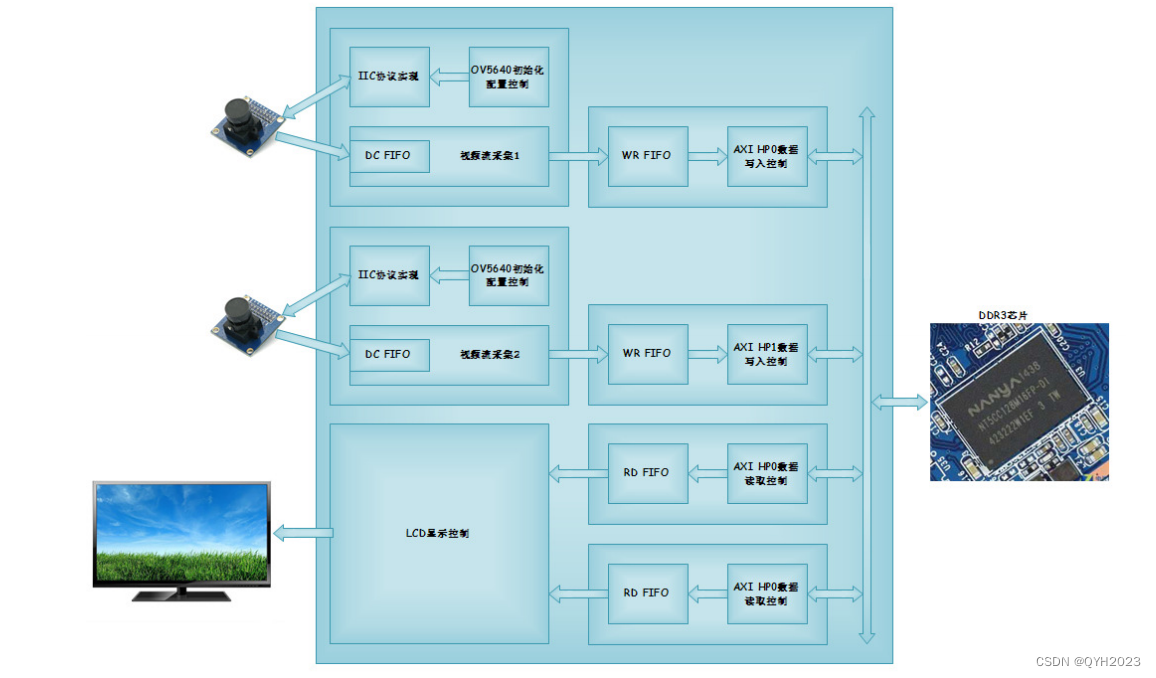

1、视频采集系统的整体架构

上电初始,FPGA 通过 IIC 接口对 CMOS Sensor 进行寄存器初始化配置。这些初始化的基本参数,即初始化地址对应的初始化数据都存储在一个预先配置好的 FPGA 片内 ROM 中。(这些初始化的参数来源于CMOS Sensor芯片手册,这里使用的是OV5640摄像头,要学好FPGA芯片手册一定要会看)

在初始化配置完成后,CMOS Sensor 就能够持续输出标准 RGB 的视频数据流,FPGA 中对 CMOS Sensor 输出的同步信号,如时钟、行同步信号和场同步信号进行检测,从数据总线上获得实时采集到的图像数据。采集到的视频数据先通过一个 DC FIFO,将原本 25MHz 频率下同步的数据流转换到 50MHz 的频率下。(为了提高数据传输速率,并与系统组件适配)

采集到的图像视频流,再送入 WR FIFO 中,这个 FIFO 中的视频数据若达到16(*64bit)个,就会被连续读出并产生 AXI HP总线时序,将这16个数据写入到 DDR3 中。

控制模块产生AXI HP总线读地址和读数据时序,读出DDR3中的视频流数据,并缓存在RD FIFO中供LCD显示器控制使用。LCD显示器控制产生LCD驱动时序,将视频流数据送往 LCD 显示。

2、视频采集系统工程代码模块设计

| 模块名称 | 功能描述 |

| Zstar_zynq_ps | 该模块是 Zynq PS(Processor System) IP 核的例化,AXI HP 总线的配置引出和系统所需时钟和复位都是来自于这个 Zynq PS。 |

| Image_controller | U2 和 U4 都例化了这个模块。该模块实现 IIC 接口对 OV5640 的初始化、OV5640 输出图像的采集和缓存等。 这个模块内部主要有 4 个子模块。I2C_OV5640_Init_RGB565.v 模块实现 IIC的接口协议和初始化配置,其下有两个子模块:I2C_Controller.v 模块实现IIC的读写控制时序,I2C_OV5640_RGB565_Config.v 模块则产生IIC寄存器初始化配置的地址和数据。image_capture.v 模块实现图像采集和缓存功能。 |

| Axi_hp0_wr | U3 和 U5 都例化了这个模块。 该模块内部例化了用于缓存写入 DDR3 数据的 FIFO,并实现了AXI HP 总线的写通道时序,完成数据通过 AXI HP 总线写入 DDR3 的操作。 |

| Axi_hp0_rd | U7 和 U8 都例化了这个模块。 该模块内部例化了用于缓存从 DDR3 中读出数据的 FIFO,并实现了 AXI HP总线的读通道时序,完成通过 AXI HP 总线从 DDR3 读出数据的操作。 |

| lcd_driver | 该模块驱动 LCD,同时产生控制逻辑读取 DDR3 中缓存的 2 个摄像头实时视频图像。 |

| led_controller | 该模块控制 LED 闪烁,指示工作状态。 |

3、板卡选择

这里我使用的板卡是特权同学的Zstar,型号是xc7z020。

接下来我将逐个讲解工程模块,包括所用到的原理以及Verilog代码。大家有问题可以私信我。

3758

3758

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?