项目场景:

意在做一个粘连检测功能的工装测试板,模拟产品的继电器异常粘连、L、N短路;用来测试粘连检测功能板是否有效。

实现过程

1.实现模拟继电器粘连检测:分别用两个继电器控制L/N吸合,用来模拟继电器粘连,再用一个继电器并在L、N的输出脚,模拟L、N短路,

2.既然是模拟三个故障,由于模拟的是强电,并且是两两互斥,所以使用故,一个三路互锁电路,不仅在软件上形成互锁,在硬件上也实现互锁;

3.理论成立,画板

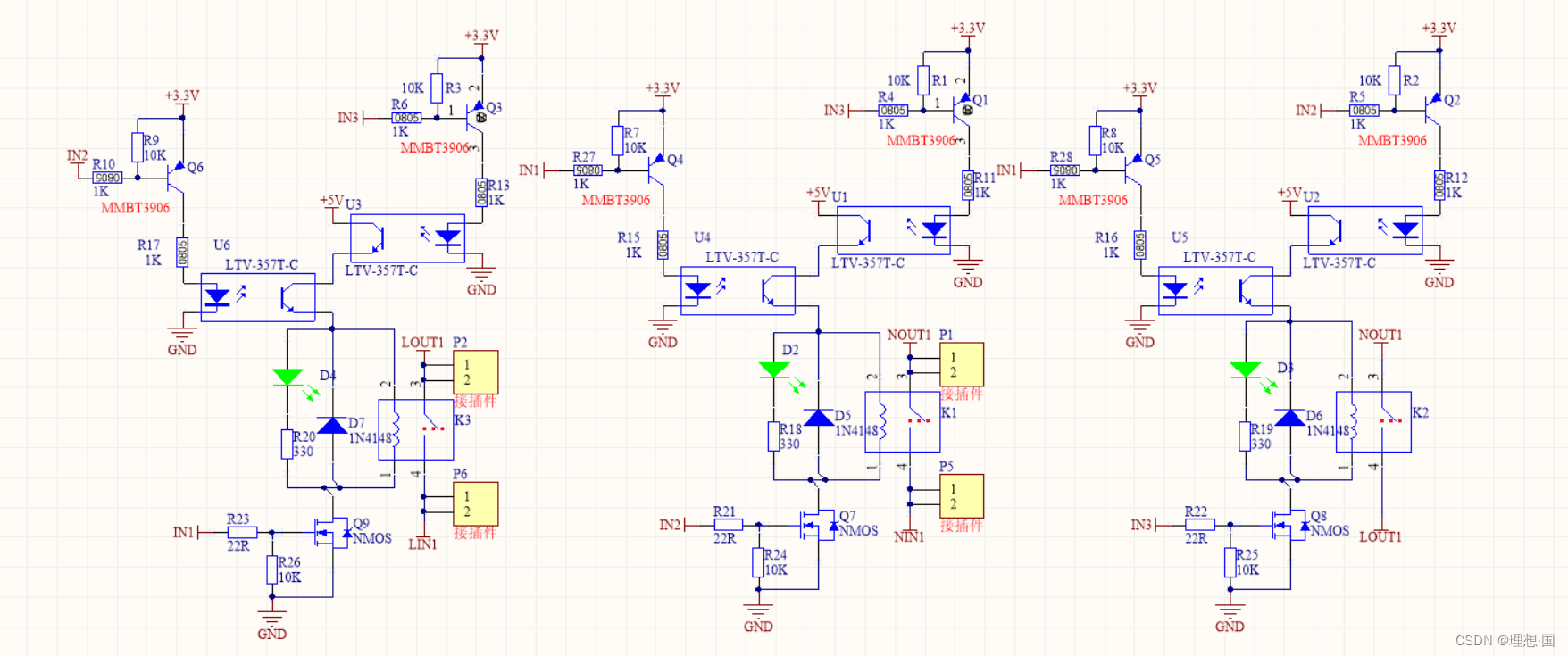

第一版原理图如下:

结果:直接炸机,三个继电器在一上电瞬间全部吸合,导致LN直接短路,保险丝烧断

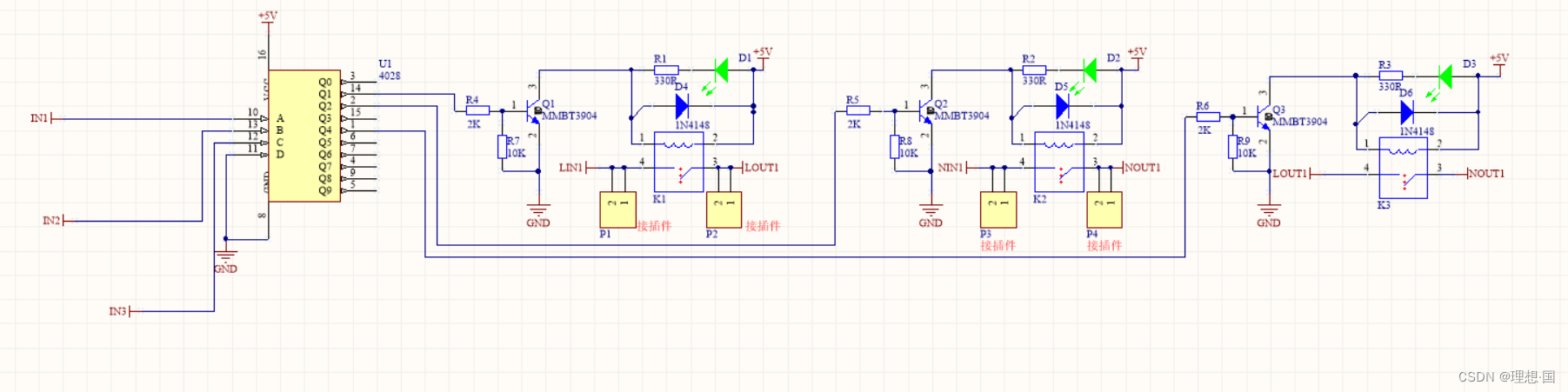

第二版原理图如下:

有了第一版的教训,直接用弱电,不加强电,上电一瞬间,所有继电器有误触发的情况发生;故分析原因,重新改原理图

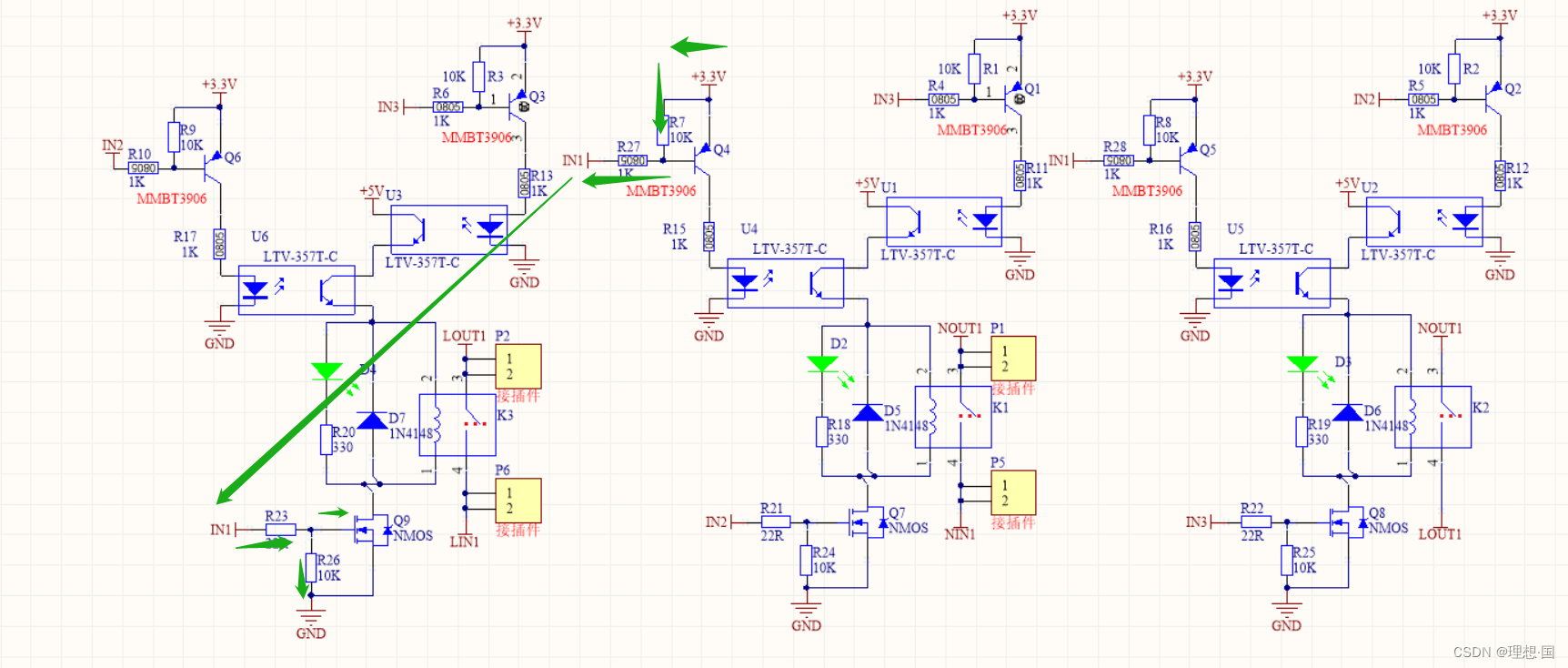

第三版原理图如下:

分析后有了第三版原理图,已经正式发布使用;

虽然是一个很简单的东西,但是却改了第三版才做好,所以说,硬件还是得细心,稍有不慎,就会炸机;

原因分析:

第一版炸机原因分析:

1、由于初衷是三路互锁,就想着用Pmos分别去控制三个继电器,三个pnp三极管去做互斥,理论上分开谈论这个电路是可行的,但是三路互锁就出现问题了;

如上图,+3.3V通过电阻R7流经R27 再到IN1的驱动电阻R23再到地;计算可以得到Q9的Vgs为+1.55V左右,所以Q9得以导通,再回头看Q4,Q4的栅极电压也为+1.55V左右,符合三极管的导通条件,故也导通,这样下来,我们的三路本意为两两互斥,但是由于设计问题,导致两两互相反馈,所以继电器全部吸合,导致LN直接短路,然后炸机!!!

第二版改版原因分析:

由于第二版想着用集成芯片数字电路直接做三路互锁,由于CMOS(芯片功能就不一一介绍啦)芯片有四个输入口,我们这里只用到了三路,故第四路接地(担心它浮空状态,电压不稳,造成的误触发),问题就处在这儿了,我能想到空着可能会电压不稳导致误触发,就没想到一上电的时候,单片机还没有控制电路,也相当于悬空状态,所以第二版电路画完之后,用弱电上电之后,所有的继电器有那么一瞬间的误触发;没办法,又得整改!!!

第三版原因分析:

直接在cmos芯片的输入脚加上下拉电阻,简单粗暴!上电运行稳定!

总结:

电路实现功能不仅仅要看某一个部分、而是要全局考量,每增加一个连接点,都可能出现和你想法相悖的情况,所以在打板之前不仅仅要在DRC其布局布线,还要考虑各种可能出现的情况,包括原理图、器件选型等:

硬件是一个长期积累的过程,可以在一个地方摔倒一次、两次,但是不能摔倒第三次;硬件工作任重而道远,加油!!!

我是理·想国,一个刚毕业的硬件小白

本文讲述了作者在设计一款粘连检测功能工装测试板的过程中,经历了三次迭代的历程。首次设计因三路互锁电路问题导致炸机,第二次尝试使用集成芯片但因上电瞬间误触发再次失败。最终,在第三版中通过在CMOS芯片输入脚添加下拉电阻解决了问题,实现了稳定运行。作者强调了硬件设计的细节重要性以及全面考虑的必要性。

本文讲述了作者在设计一款粘连检测功能工装测试板的过程中,经历了三次迭代的历程。首次设计因三路互锁电路问题导致炸机,第二次尝试使用集成芯片但因上电瞬间误触发再次失败。最终,在第三版中通过在CMOS芯片输入脚添加下拉电阻解决了问题,实现了稳定运行。作者强调了硬件设计的细节重要性以及全面考虑的必要性。

6220

6220

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?