FPGA,英文全称是 Field Programmable Gate Array,中文意思是现场可编程门阵列。基本架构:可配置逻辑模块(CLB: Configurable Logic Block)、开关矩阵(Switch Matrix,也称为 Switch Box)、互连线(Interconnect Wires)和输入 / 输出引脚。

通常应遵循的原则包括:

(1)需要实例化的输入 / 输出单元如 IDDR、ODDR、ISERDES、OSERDES 等尽可能

靠近设计顶层,尽管 IBUF、OBUF、IOBUF 和 OBUFT 可由综合工具自动推断出来,但

要确保 IOBUF、OBUFT 的使能信号和输入 / 输出信号在同一层次,以确保工具正确推断;

(2)时钟生成模块(通常采用 Clocking Wizard IP 生成时钟,不建议使用 MMCM 或

PLL 原语)放在顶层,方便其他模块使用时钟;

(3)在层次边界添加寄存器,对关键模块确保是寄存器输出,这样可将关键路径隔离。在单一层次或模块之内,对于修复时序违例及设计调试大有裨益;

(4)确保需要手工布局的模块在同一层次之内。

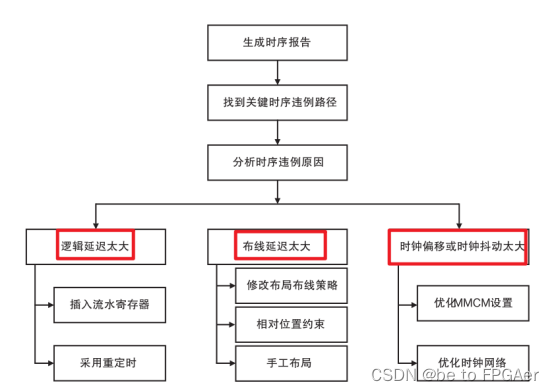

一般情况下,建立时间违例原因包括:逻辑延迟太大、布线延迟太大、时钟偏移或时钟抖动太大。

- 逻辑延迟太大,解决办法有两种:插入流水寄存器和采用重定时。前者需要修改代码,由于增加流水寄存器会导致从输入到输出所需的时钟周期个数发生改变,涉及多条路径的数据需要重新对齐,改动量可能会比较大;后者无须改动代码,但需要确定是在综合阶段设置重定时还是在布局布线阶段设置重定时,是全局设置(使用全局设置选项)还是局部设置(使用模块化综合技术)。

四大基本原则:

- 硬件原则

必须采用 HDL 可综合的部分进行电路设计,遵循可综合的代码规范。7 系列 FPGA 中的触发器复位信号只支持高有效,如果代码中的复位是低有效就会消耗额外的查找表(用于逻辑取反),而 UltraScale/UltraScale+ FPGA 中的触发器则既支持高有效又支持低有效;7系列 FPGA 中的 DSP48 不支持异步复位,因此,如果代码中描述的乘法器使用了异步复位,那么相应的触发器是无法被吸收到 DSP48 内部的。

综上所述,硬件原则要做到:

(1)使用可综合的 HDL 代码描述电路。

(2)先有电路,再写代码。

(3)RTL 代码风格与所选 FPGA 内部结构相匹配。

2、同步原则

广义同步时钟是指时钟组(一个时钟组至少有两个时钟)内的时钟之间有明确的相位关系。反之,若时钟组内的时钟之间没有明确的相位关系,则认为它们是异步时钟。

遵循“时钟个数尽可能少”的原则。

同步设计的优点:

- 同步设计可以有效地避免毛刺的影响,增强设计的稳定性。组合逻辑可能会产生毛刺,如果毛刺仅存在于同步时序的数据路径中,那么受时钟驱动的触发器就可以过滤掉毛刺,因为触发器仅在时钟有效沿才会有动作,从而消除其对电路的影响。但如果将该组合逻辑的输出也连接到触发器的控制端,如作为触发器的异步复位 / 置位信号,当毛刺足够宽时,就可能导致触发器误动作。即使毛刺的宽度不足以驱动异步置位 / 复位端,也会造成触发器不稳定,甚至激发其产生亚稳态。

- 同步设计可以减少外部环境对芯片的影响。芯片的实际工作环境可能要比我们的实验环境更为恶劣,这也是我们做高低温实验的一个主要原因:检测当前设计是否能在不同环境下正常工作。此外,长时间运行也会使芯片自身温度升高,电压变得不稳定,芯片内部延时可能会发生微小变化。如果采用异步设计,时序要求比较严苛的电路将无法正常工作,这是因为异步逻辑设计的时序正确与否完全依赖于每个逻辑元件的逻辑延时和布线延时。

- 同步设计更有利于静态时序分析( Static TimingAnalysis,STA)和验证设计的时序性能。这得益于同步设计的时序约束更为简单。即使对于同步跨时钟域路径,工具也可自动对其进行约束,当然有时会出现约束不合理的情形。

3、流水原则

流水线技术是有要求的:数据流是单向流动,不存在反馈支路。

流水线技术也体现了 FPGA 处理数据的特征:动态处理。增加流水寄存器会导致 Latency。

4、面积和速度的平衡与互换原则

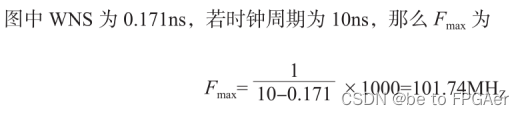

度指的是设计在 FPGA 上稳定运行时所能达到的最高频率,也就是我们常说

的 F max ,可间接地通过时序报告中的 WNS(Worst Negative Slack:建立时间最小裕量。FPGA性能指标:设计可运行的最高频率(Fmax )、输入到输出的时钟周期(Latency)、吞吐率(Throughput)、资源利用率和功耗(Power)。

为什么latency小流水线级数低,fmax降低?

如果流水级数较高的话,将任务进行划为小任务,同一个时钟周期的延时较小,此时支持的fmax可以设置较高,如果一个周期做多个操作,延时就比较大,这时fmax如果较高,容易造成时序违例。

2195

2195

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?