UVM的VCS编译错误

1.在做sub_system验证,把各个组件集成到env中时报了个错误。

(这个error不同与之前的complied error,出现在uvm tree完成后出现的。)

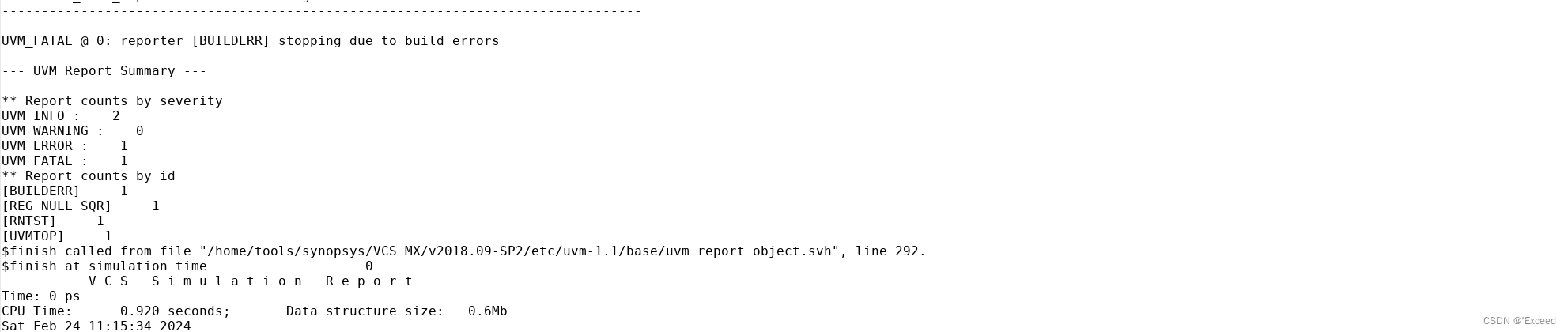

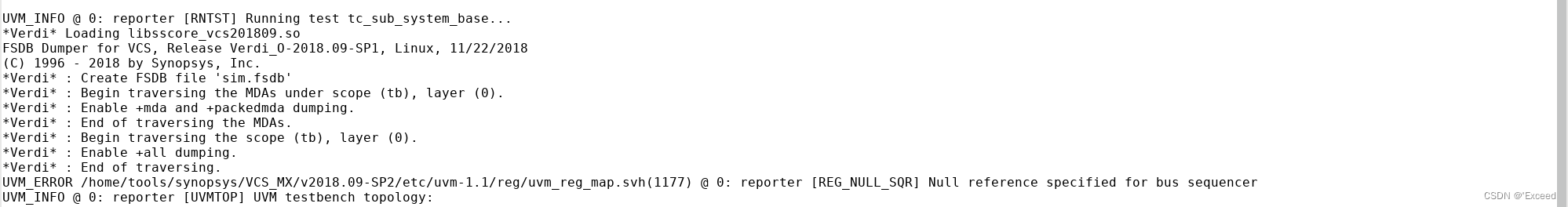

UVM_FATAL @ 0 : reporter [BUILDERR] stopping due to build errors.在打印的summary信息中发现,fatal之前应该还存在一个error,便在log中找到error的位置。如下:

UVM_ERROR @ 0 : reporter [REG_NULL_SQR] Null reference specified for bus sequencer.debug思路:首先,error类型是从来没有见过的类型,Null reference specified for bus sequencer。(没有为bus sequencer指定reference?)其次,在error出现之后还打印了整个UVM的拓扑结构,这个打印任务是在connect_phase中执行的,因此可以排除时build_phase中出现error。(在第一次debug时,没有确定好error的位置,大概存在于connect_phase.....,因此当时没有丝毫头绪)

在这个网站中找到了一点debug思路:How to use a register model from a virtual sequencer? - UVM (Pre-IEEE) Methodology and BCL Forum - Accellera Systems Initiative Forums

这个博主定位的问题是存在与virtual_sequencer对register model的映射上,于是便去寻找virtual_sequencer和register model的相关代码上。最终发现,register model和virtual_sequencer的映射没有问题,但是env中的connect_phase却是空的。。。。。。

error原因:virtual_sequencer内部的sequencer没有映射到env中。

function void sub_system_env :: connect_phase (uvm_phase phase)

super.connect_phase(phase);

endfunction于是,在virtual_sequencer中找到sequencer句柄:uart_sqr,spi_sqr。在把这个两个句柄映射到env中

function void sub_system_env :: connect_phase (uvm_phase phase)

super.connect_phase(phase);

//把v_sqr中的每个sequencer连接在env中例化后的uart_env和spi_env中

v_sqr.uart_sqr = uart_env_inst.uart_env.uart_agent.sequencer;

v_sqr.spi_sqr = spi_env_inst.spi_env.sequencer;

endfunction思考:这个确实是个新手会犯的错误,根本原因可能是对于uvm中每个component的所位于uvm_tree位置不清楚。virtual_sequencer本身就是集中了所有部件的sequencer,需要例化在sub_system_env中。但是例化后,virtual_sequencer内部的sequencer却没正确的映射,相当于sequencer就是不知道装在哪个武器上的弹匣。如果忽略了这个错误,就会出现自己明明写了sequencer,但是uvm却没有运行的问题。

388

388

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?