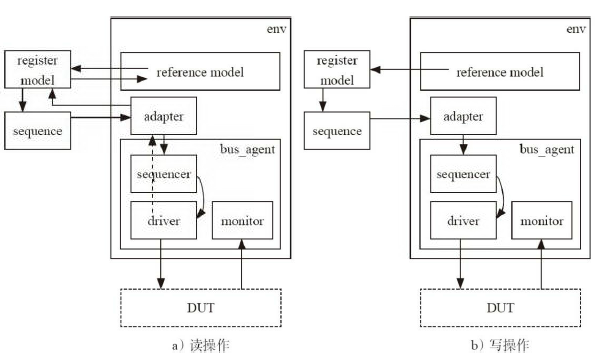

1.前门如下:

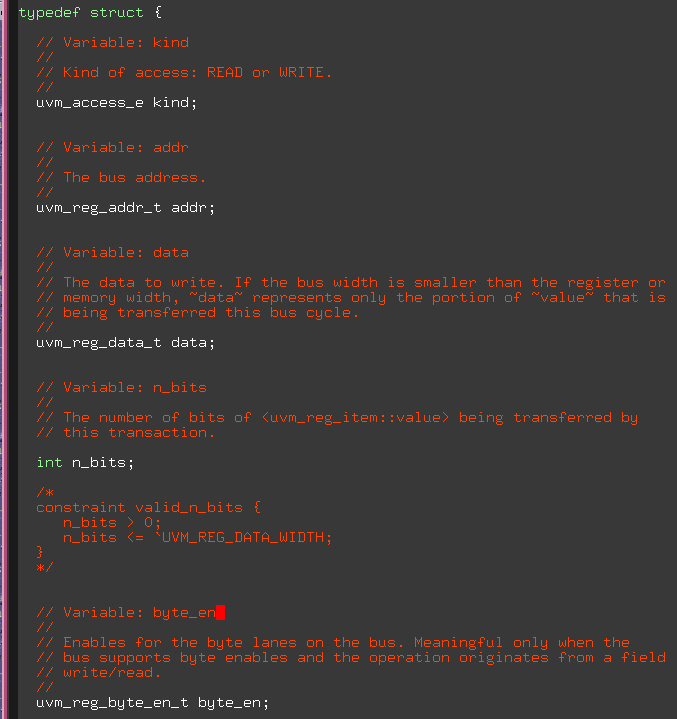

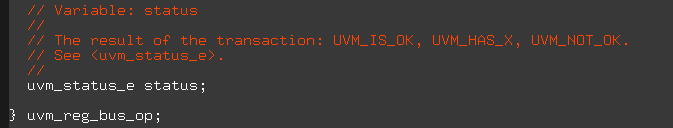

1)无论读写,寄存器模型都会通过sequence 产生一个uvm_reg_bus_op 的变量:

此变量中的信息要经过一个adapter 转换后交给bus_sequencer,随后交给bus_driver,实现前门操作。

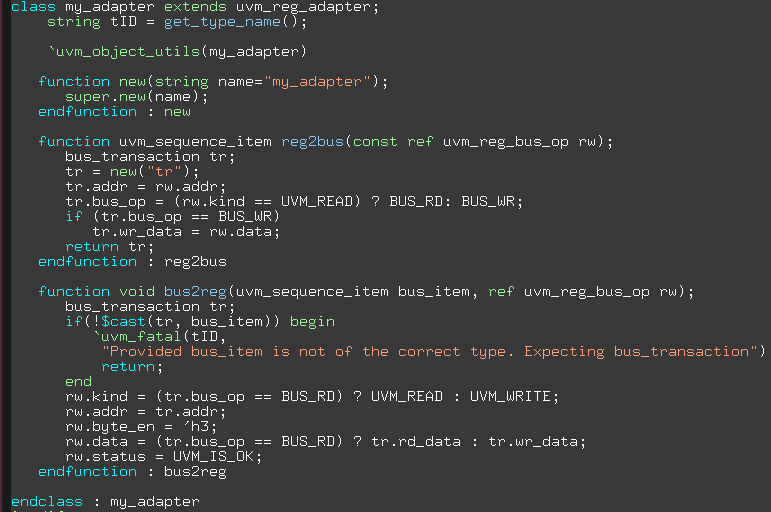

2.adapter:

1)定义好两个函数,reg2bus,寄存器模型通过sequence 发出的uvm_reg_bus_op 型的变量转换成bus_sequencer 能够接受的形式。

2)bus2reg:当监测到总线上有操作时,将收集的transaction 转换成寄存器模型能够接受的形式,以便寄存器模型能够更新相应的寄存器的值。

3)读操作是,bus_driver 能够获得要读取的值,将此值放入从bus_sequencer获得的bus_transaction中,那么bus_transaction就会有读取的值,经过adapter 的bus2reg传递,最终被寄存器模型获取。由于没有实际的transaction 传递,所以虚线。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1080

1080

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?