一、EPWM

EPWM:Enhanced Pulse Width Modulator,即增强型脉冲宽度调制器。

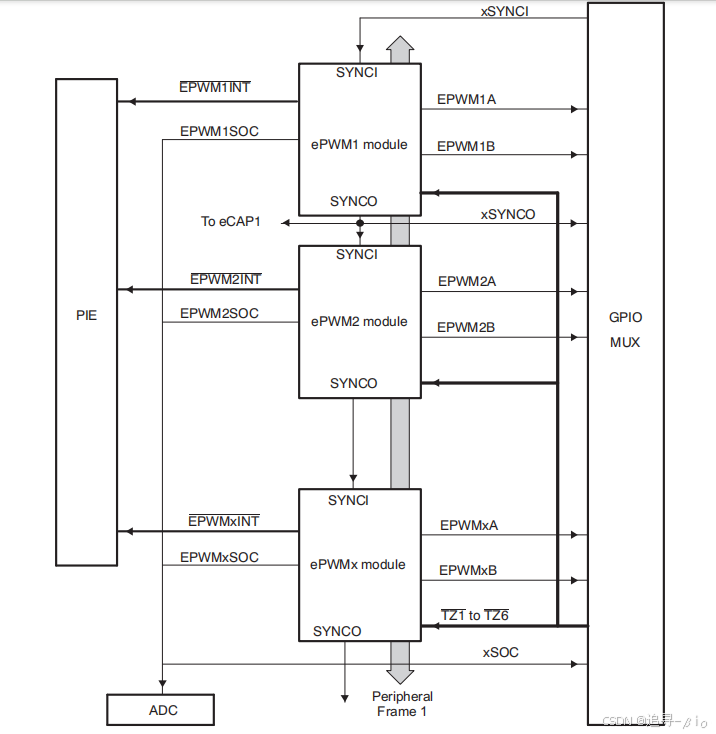

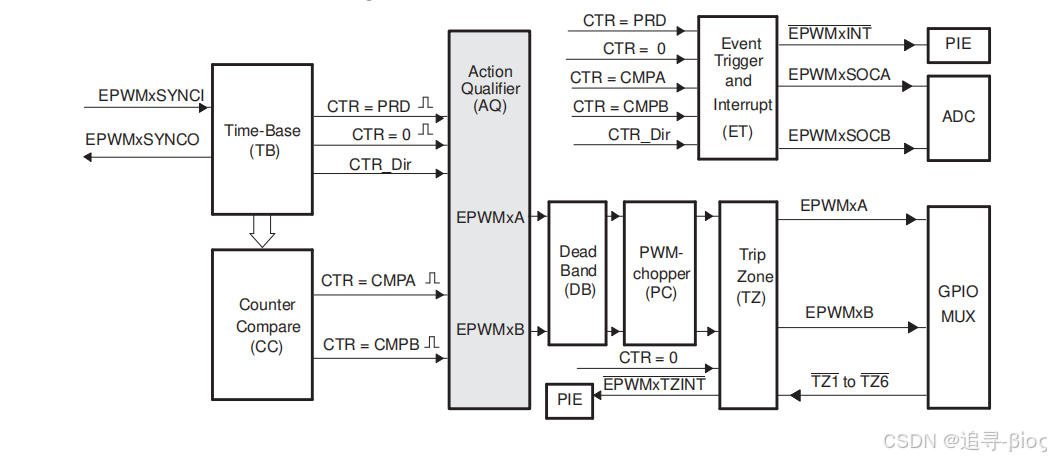

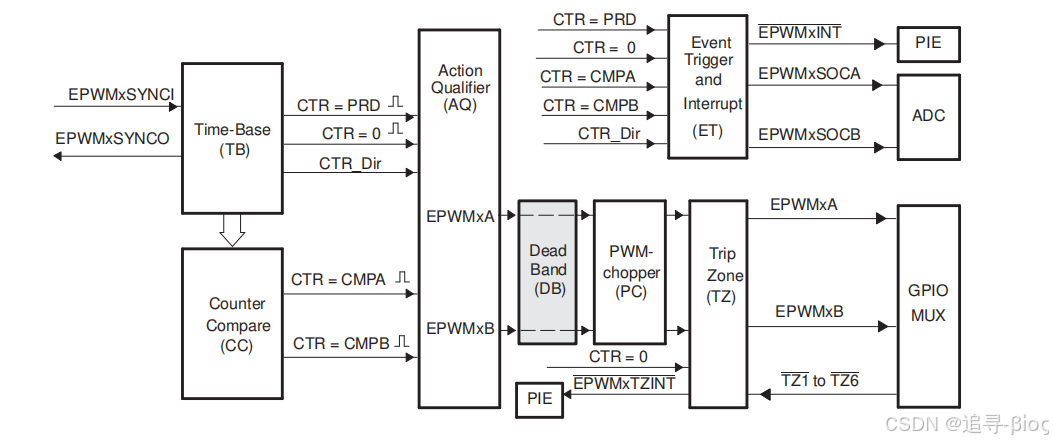

EPWM关联外设

EPWM模块化

1、EPWM 输出信号(EPWMxA和EPWMB)

2、Trip-zone 信号(TZ1 ~ TZ6)

这些输入信号能够将外部告警信息传递给epwm模块,通过配置GPIO外设异步输入。

3、时基同步输入(EPWMxSYNCI)和输出(EPWMxSYNCO)信号

同步信号连接于各个EPWM模块,由上图知,前一个EPWM同步输入作为后一个EPWM的同步输入。而只有EPWM1的同步信号输入来自时钟同步信号,另外,EPWM1SYNCO作为ECAP1(增强型捕获模块1)的同步输入。

4、ADC启动转换信号(EPWMxSOCA和EPWMxSOCB)

每个EPWM有两个ADC启动转换信号。任意一个EPWM都可以触发序列器启动转换。

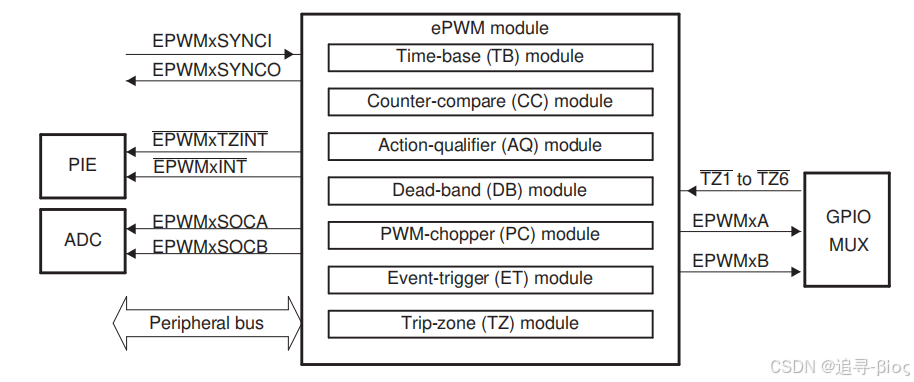

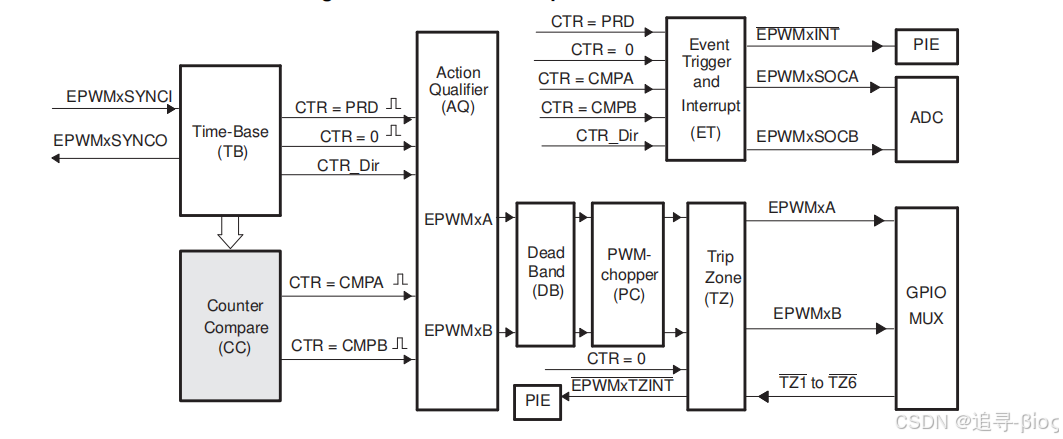

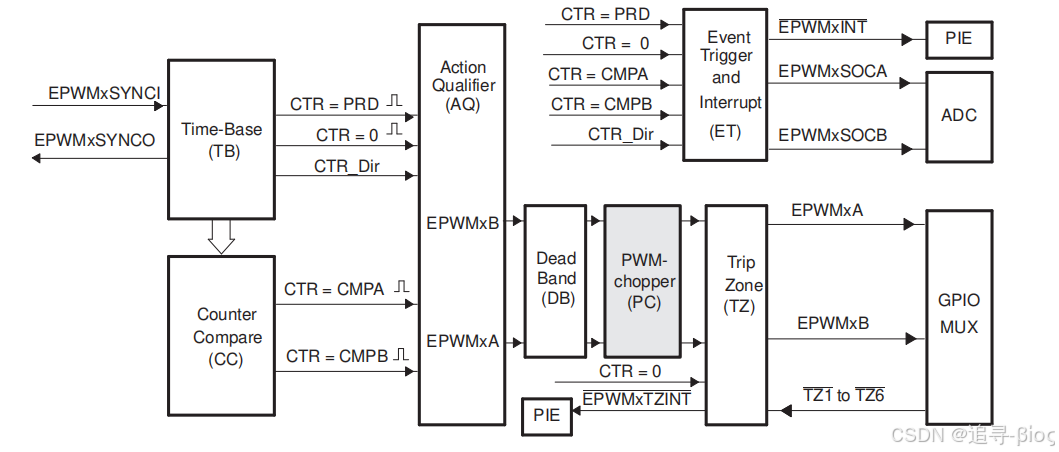

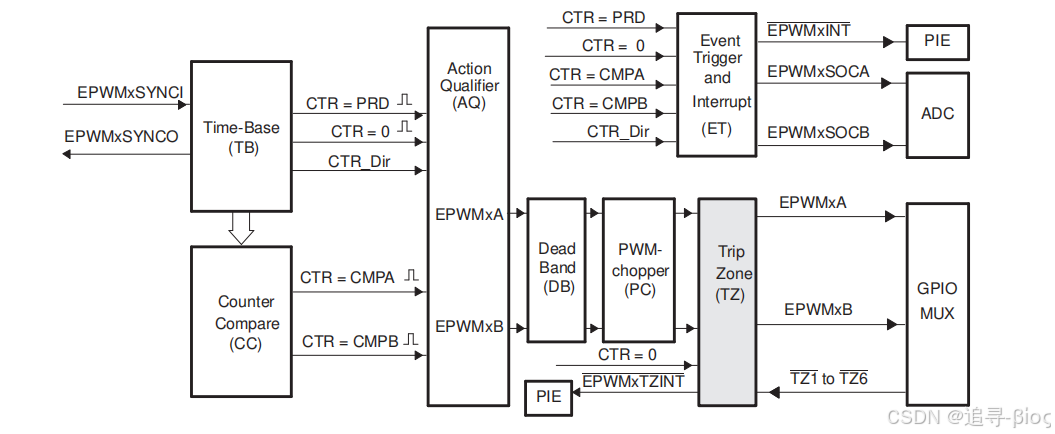

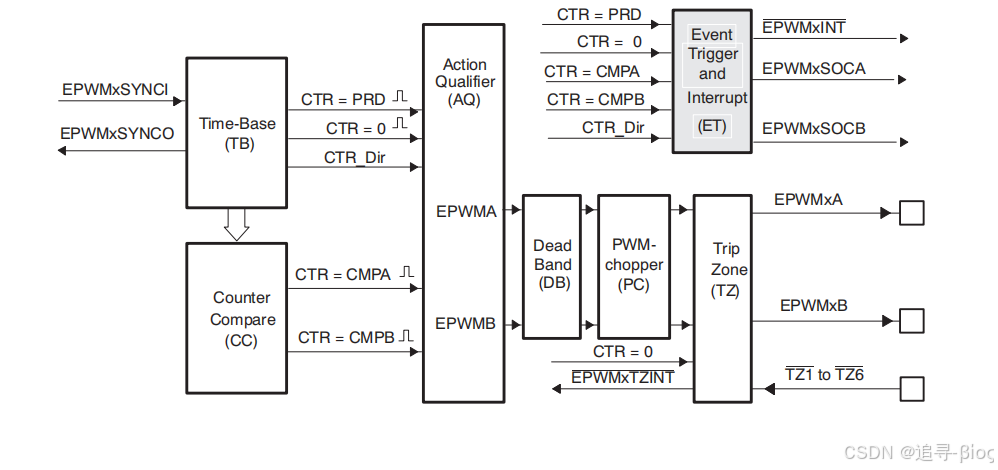

EPWM结构图

二、EPWM模块

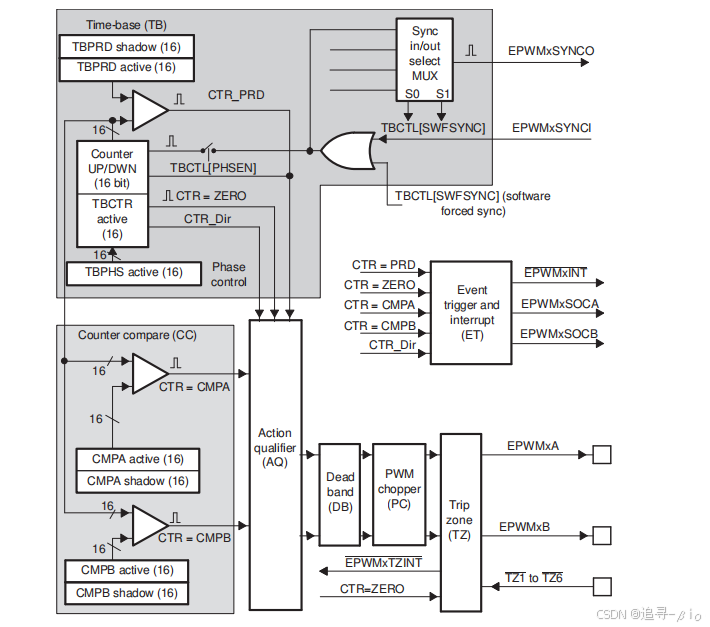

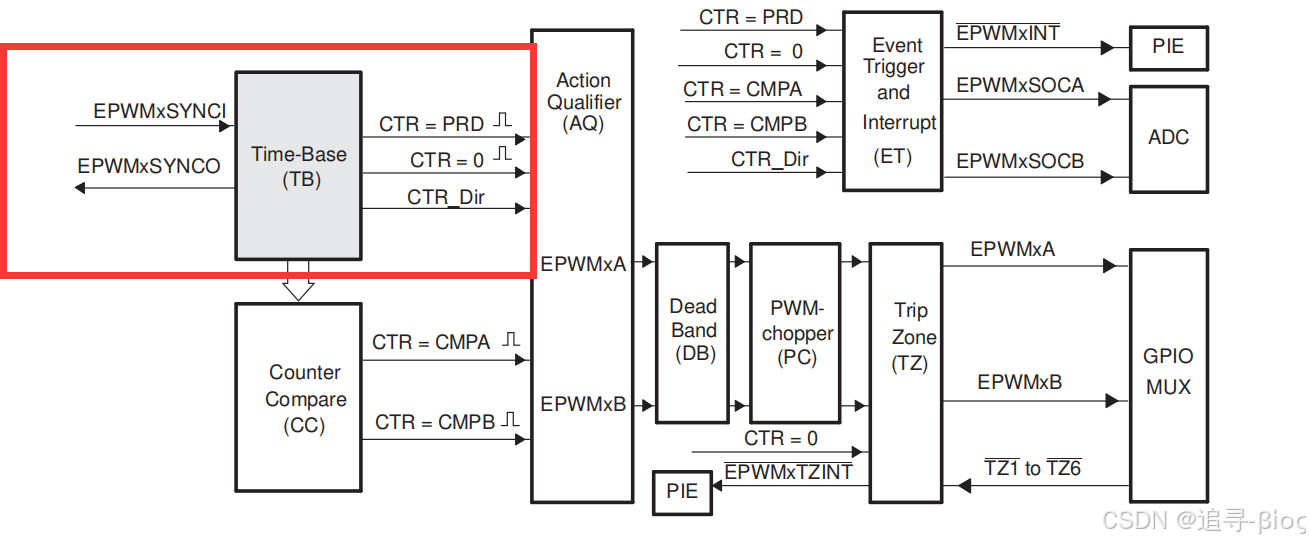

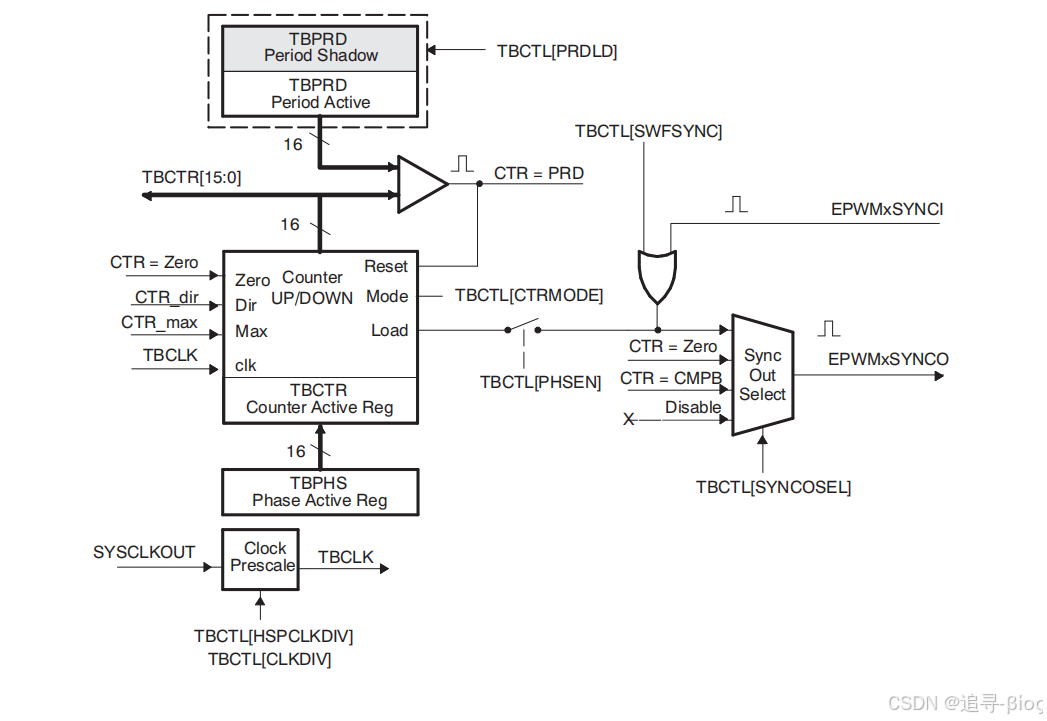

1、Time-base Submodule(TB,时基单元)

每个ePWM模块都有自己的时基单元,用来决定EPWM所有事件的时序。

时基单元结构图

EPWMxSYNCI:时基同步输入即输入脉冲,用于同步时基计数器与其他EPWM中较快的ePWM模块的计数器。对于EPWM来说,可以开启或者关闭同步功能,即可以接收或者不接收同步信号。对于EPWM1来说,它的同步信号来源于设备引脚输入,而不是EPWM。对于其他EPWM,如EPWM2接收EPWM1的同步信号,EPWM3接收EPWM2的同步信号,以此类推。

EPWMxSYNCO:时基同步输出即输出脉冲,用于同步时基计数器于其他EPWM中较慢的EPWM模块的计数器。产生输出脉冲的方式有三种:EPWMxSYNCI;计数器CTR值为0;计数器CTR值等于比较器B值。

CTR=PRD:时基计数器等于指定周期。

CTR=Zero:时基计数器等于0。

CTR=CMPB:时基计数器等于比较计数器B。

CTR_dir:时基计数方向,高电平表示计数器递增,低电平表示计数器递减。

CTR_max:用来指示时基计数器达到最大值0XFFFF。

TBCLK:时基时钟,由SYSCLKOUT分频得到,作为EPWM所有单元的时钟,决定了计数器的计数速率。

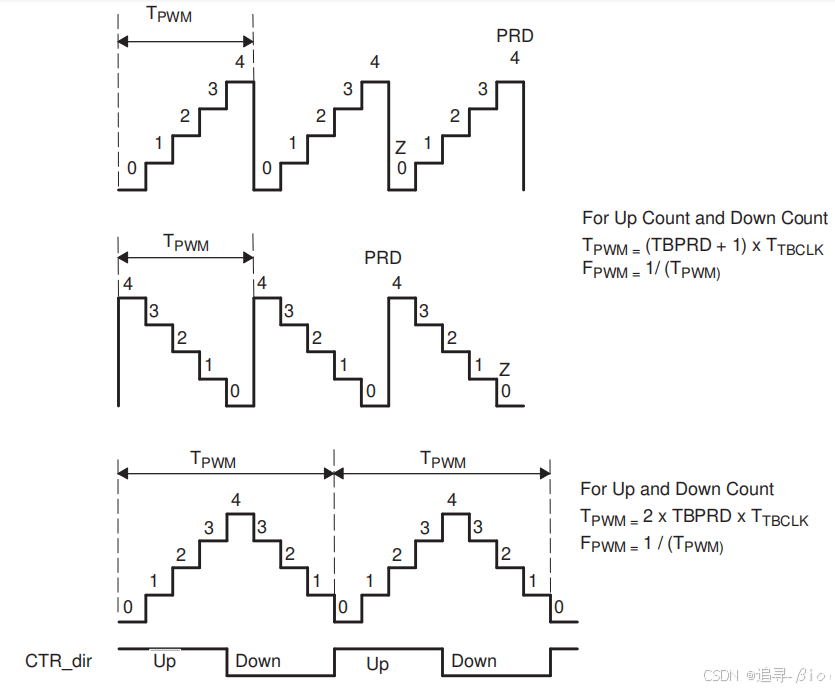

1.1 PWM周期/频率计算

PWM频率由时基周期TBPRD寄存器控制。时基计数器有三种模式:递增递减模式、递增模式、递减模式。

递增递减模式:时基计数器从0开始递增加到TBPRD,接着从TBPRD递减到0,如此反复。

递增模式:时基计数器从0递增到TBPRD,接着又从0递增,如此反复。

递减模式:计数器从TBPRD递减到0,接着又从TBPRD递减,如此反复。

1.2 时基周期影子寄存器

Active Register和Shadow寄存器定义:前者投入到实际硬件电路中运行,后者为前者提供一个暂时的空间,不会参与硬件电路运行。在一个关键时间点(如一个新周期的开始),后者会将其存放的内容传送到前者,防止由于前者被软件异步修改造成冲突错误运行。

两者的存储器地址相同,向哪个寄存器写入或者读取取决于TBCTL寄存器的PRDLD位,即要不要开启影子寄存器模式。

时基影子周期模式:当TBCTL.PRDLD=0时选择TBPRD影子寄存器写入或者读取。当时基计数器等于0时影子寄存器的内容传输到实际运行寄存器(TBPRD(Active)<-TBPRD(shadow))。

时基周期立即装载模式:当TBCTL.PRDLD=1时,直接写入或者读取Active TBPRD。

1.3 时基时钟同步

外部时钟使能寄存器中的TBCLKSYNC位可以同步所有使能的EPWM的TBCLK。当该位置起时,所有的EPWM的时钟从第一个上升沿开始。如果想完全同步,则每个EPWM的TBCLK需保持相等。

配置步骤:使能EPWM时钟--->清除同步时钟位---->配置EPWM------>置起同步时钟位。

注:先清除同步位是为了防止没有配置完成EWPM就开始同步运行。

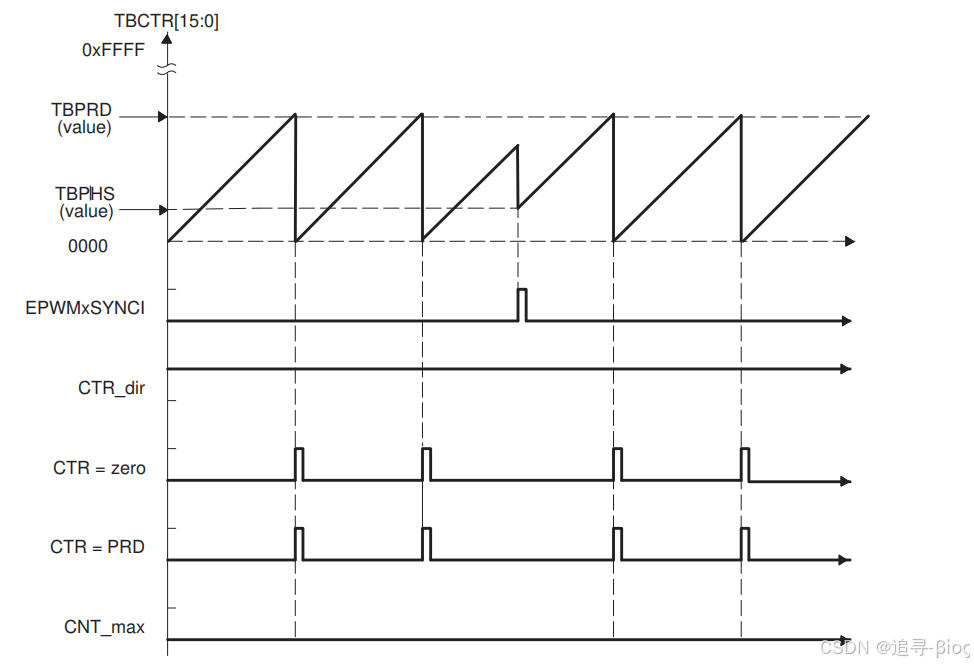

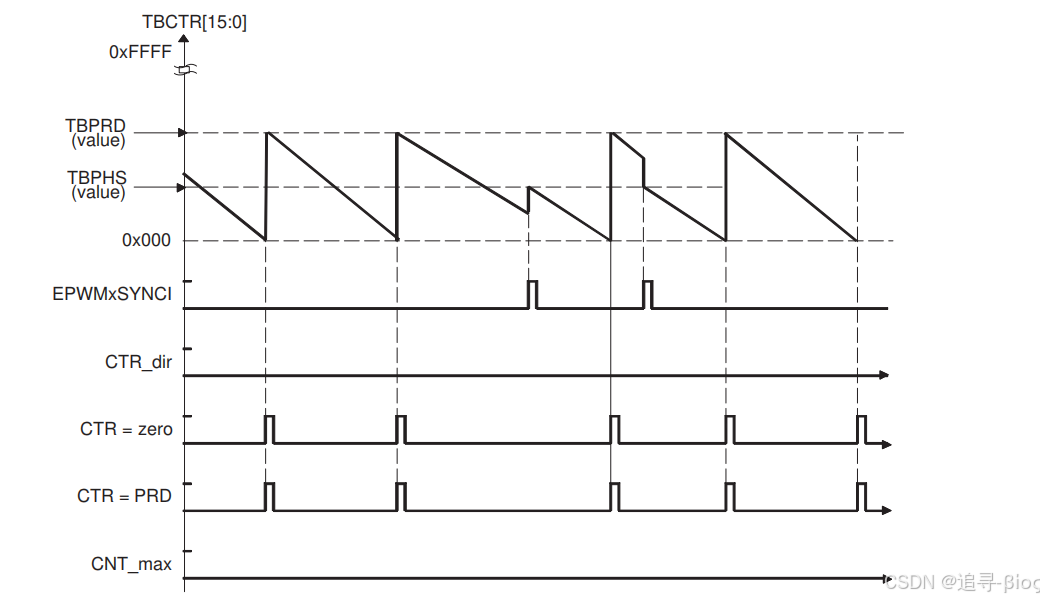

1.4 时基计数同步

每个EPWM模块可以配置为使用或者忽略同步输入信号。当TBCTL寄存器的PHSEN位置起时,如果发生如下事件,时基计数器TBCTR将自动装载TBPHS的内容。

同步输入信号(脉冲):当检测到同步脉冲时,会在TBCLK有效边沿处将TBPHS的值加载到TBCTR。该过程需要2个SYSCLKOUT(当TBCLK=SYSCLKOUT)或者1个TBCLK(当TBCLK!=SYSCLKOUT)的延迟时间。

软件强制同步脉冲:当写1到TBCTL.SWFSYNC位时,会触发一次软件强制同步。这个脉冲跟同步信号脉冲呈“或”关系。在递增递减模式下,TBCTL.PSHDIR位在同步事件即将产生时,能够立即改变时基计数器的方向,而在递增/递减模式下PHSDIR被忽略。

通过清零TBCTL.PHSEN位能够忽略同步输入信号。但是同步脉冲依旧能够顺着往下同步其他EPWM。

1.5 时基时钟

TBCLKSYNC位(属于系统时钟寄存器,而不是EPWM模块寄存器)能够同步所有使能的EPWM模块。当TBCLKSYNC=0时,所有EPWM的时基时钟都将停止。当TBCLKSYNC=1时,所有EPWM模块的时钟都将从上升沿开始。如果想实现完全同步,则分频系数(TBCTL寄存器)需保持一致。

注:如果实现同步时钟,需先TBCLKSYNC=0,等配置完成后再令TBCLKSYNC=1。

1.6 时基计数模式

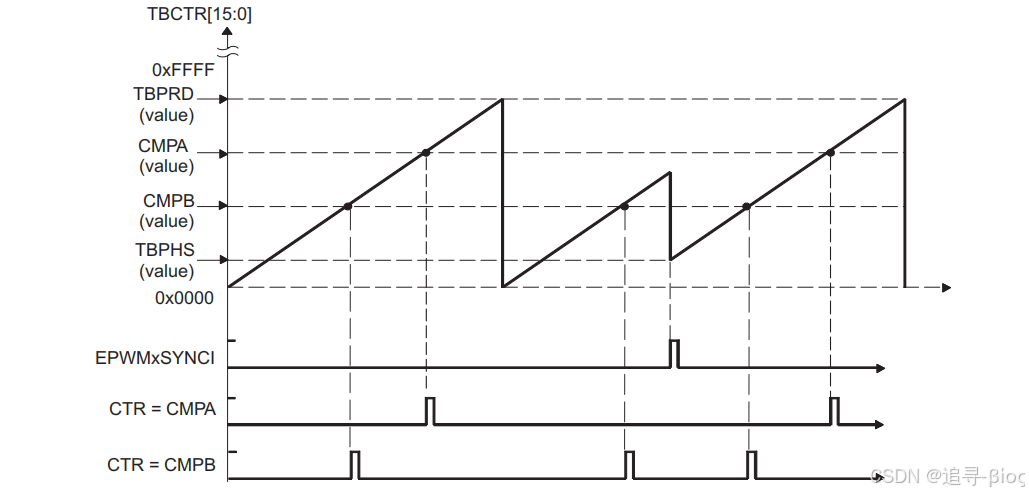

递增计数波形图

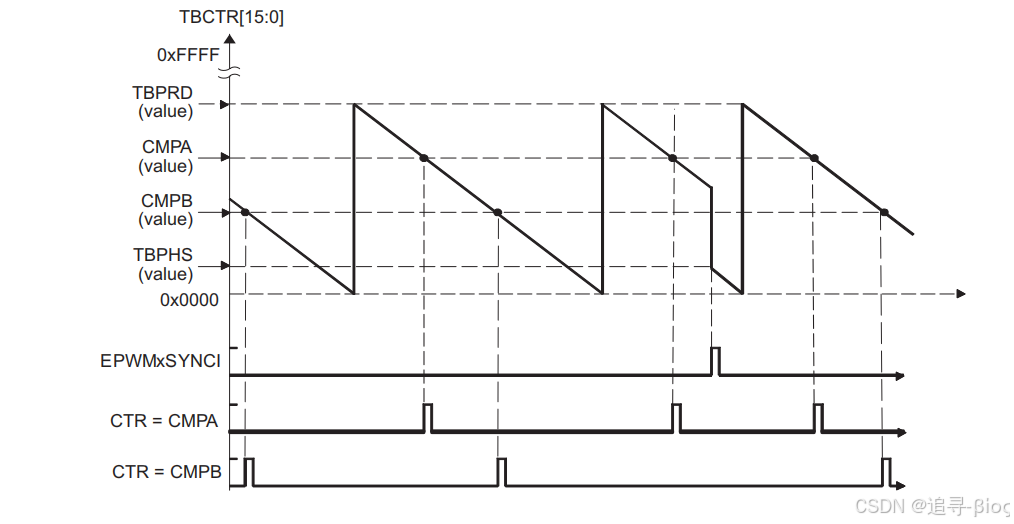

递减计数波形图

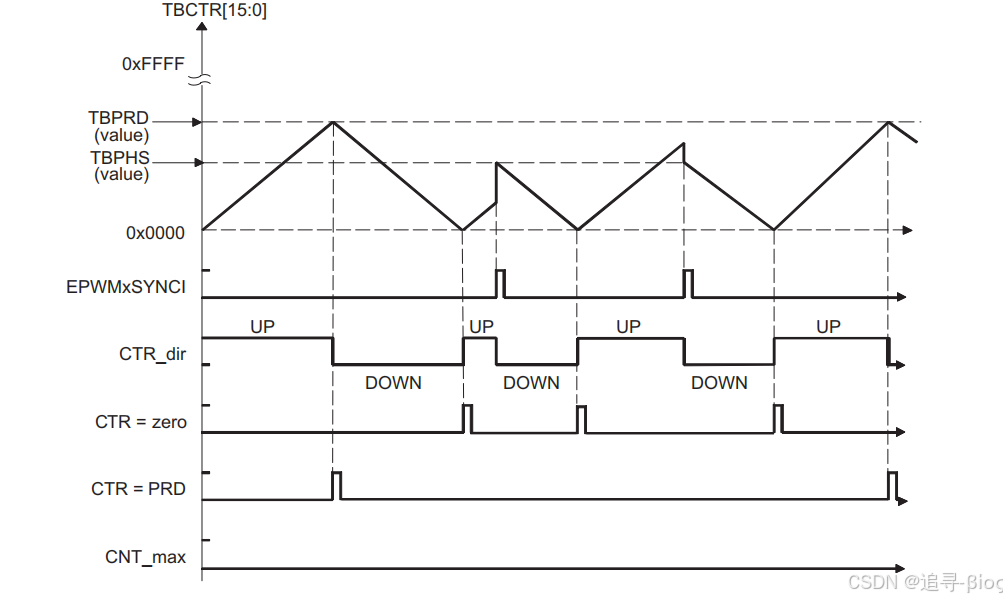

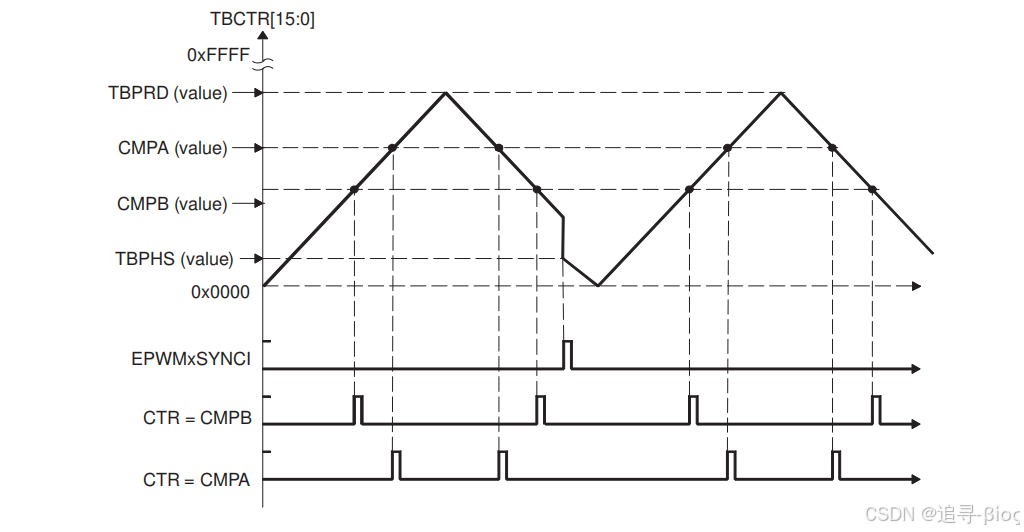

递增递减计数,PHSDIR=0同步事件递减计数

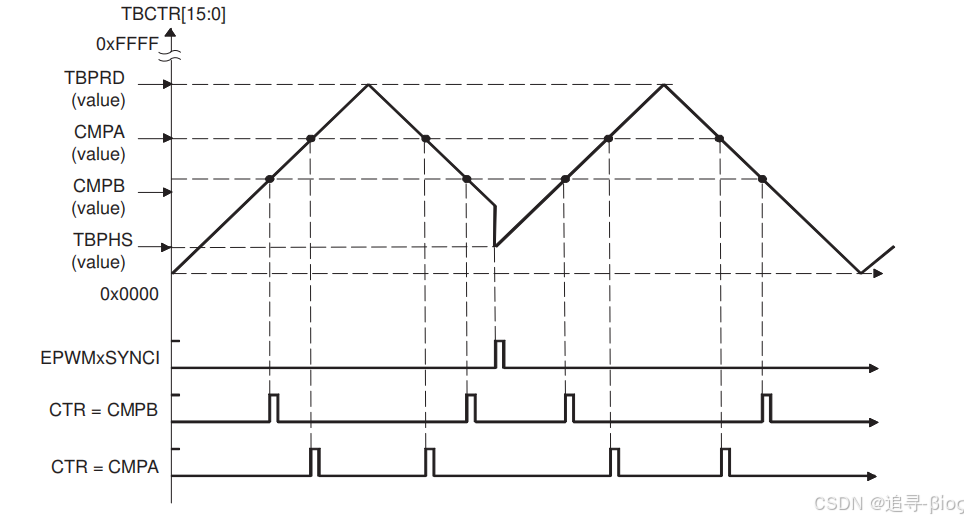

递增递减计数,PHSDIR=1同步事件递增计数

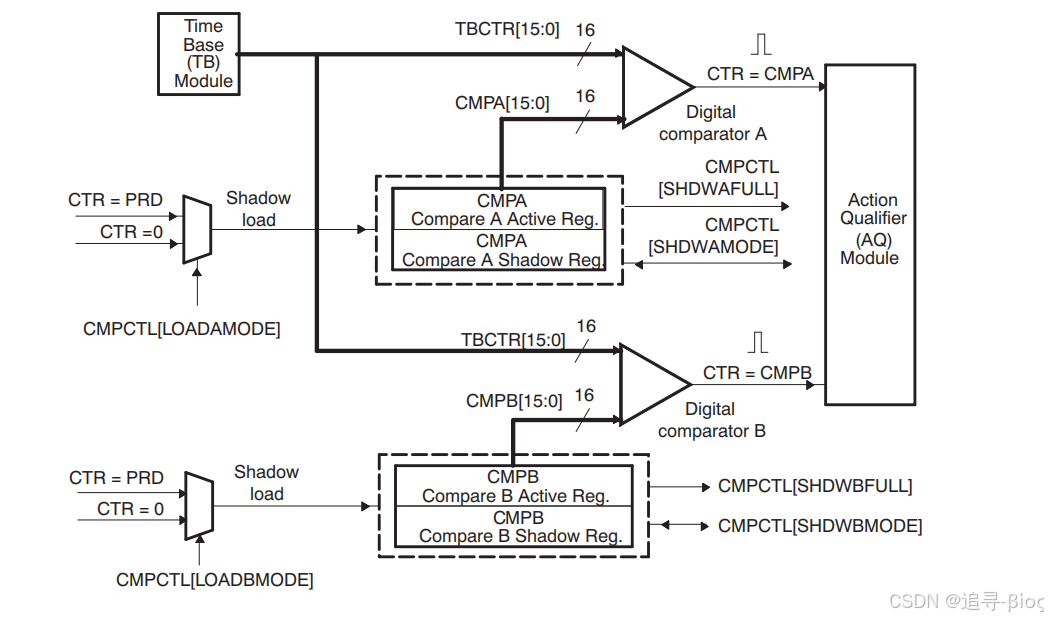

2、计数比较器单元

比较器结构图

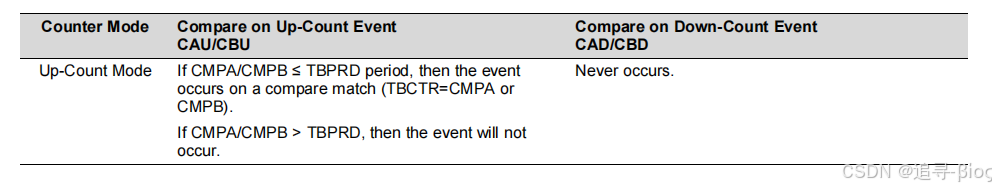

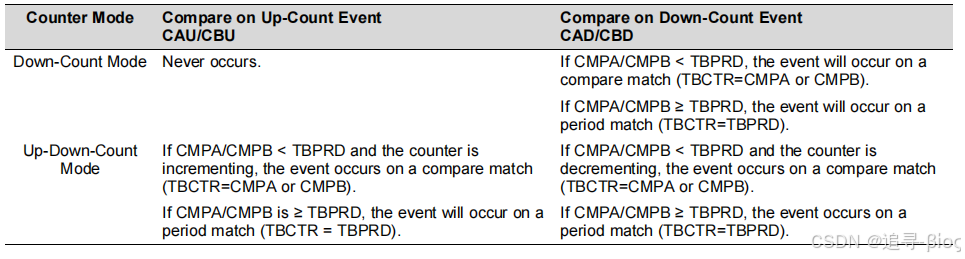

基于两个比较器CMPA和CMPB,比较器单元同来产生两个独立的比较事件。

对于递增或者递减计数模式,每个事件在每个周期只产生一次,而对于递增递减模式,如果比较器值在0x0000~TBPRD之间,则每个事件在每个周期产生两次,如果比较器值为0或TBPRD,则产生一次。

2.1 影子寄存器

比较器CMPA和CMPB都有一个影子寄存器,同理与TBPRD寄存器,防止寄存器值被软件异步修改造成错误。

通过CMPCTL.LOADAMODE来选择什么时候将影子寄存器的值加载到Active寄存器,如CTR=PRD/CTR=ZERO/CTR=PRD、CTR=ZERO。

2.2 计数模式波形

递增模式下的比较计数

注:由于同步信号事件会造成TBCTR计数的不连续,会导致比较事件被跳过。

递减模式下的比较计数

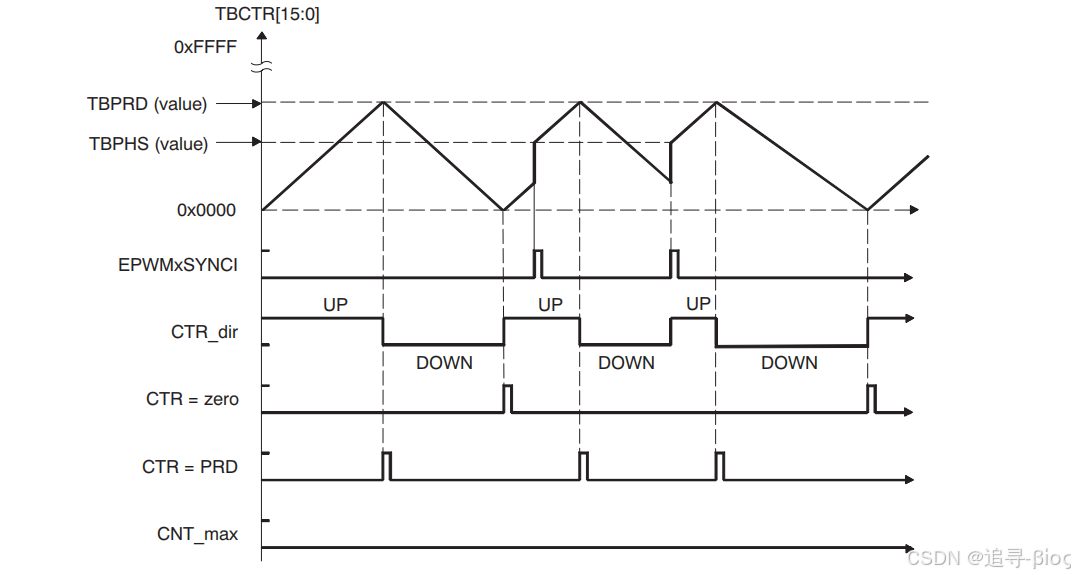

递增递减比较模式,PHSDIR=0同步递减

递增递减比较模式,PHSDIR=0同步递增

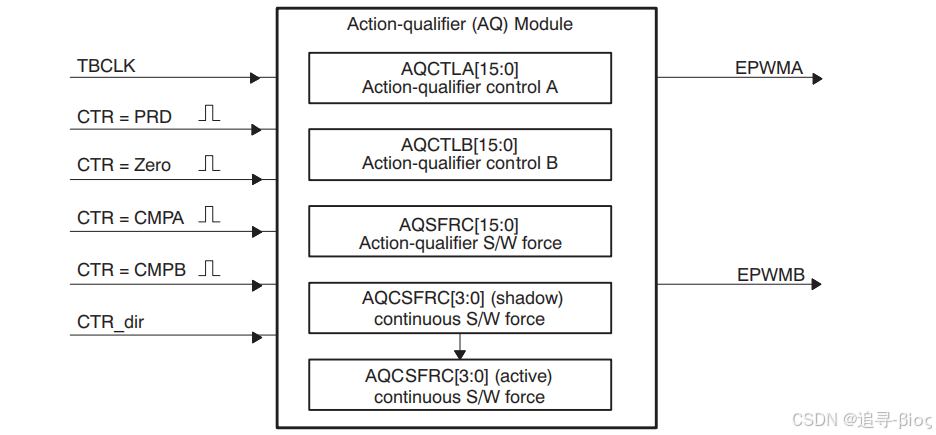

3、动作限定单元(Action-Qualifier Submodule)

该单元用于动作产生,在CTR=PRD/ZERO/CMPA/CMPB时,产生如拉高、拉低、翻转信号的动作;当事件同时发送时,分配优先级。

AQ单元基于事件触发逻辑,可以看作一个由事件控制的开关。当事件产生时,AQ单元控制两路输出EPWMxA和EPWMxB。

动作限定单元输入输出

注:计数器方向会进一步限定事件输入,使得在递增递减时可以独立产生动作。

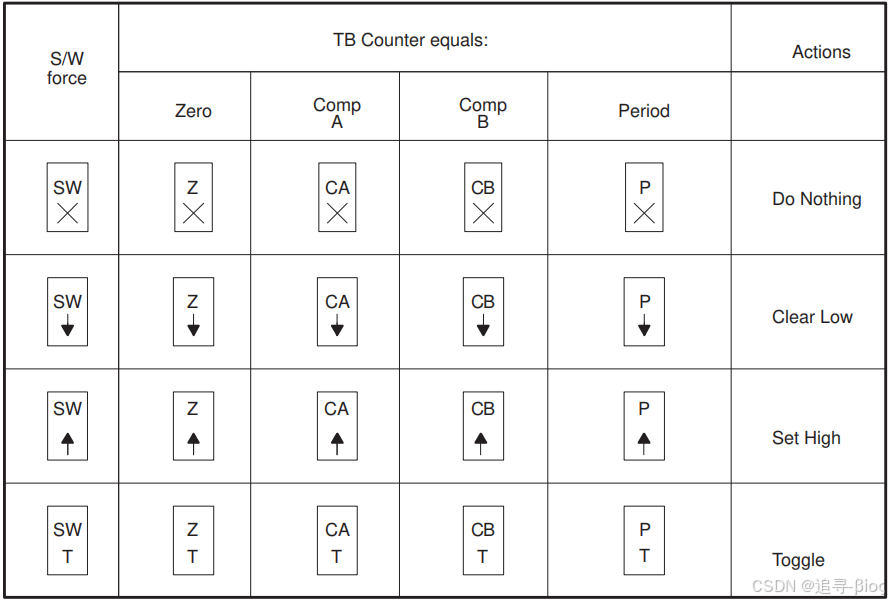

促使EPWMxA和EPWMxB产生的动作:拉高、拉低、翻转、保持不变。

EPWMx和EPWMxB动作图

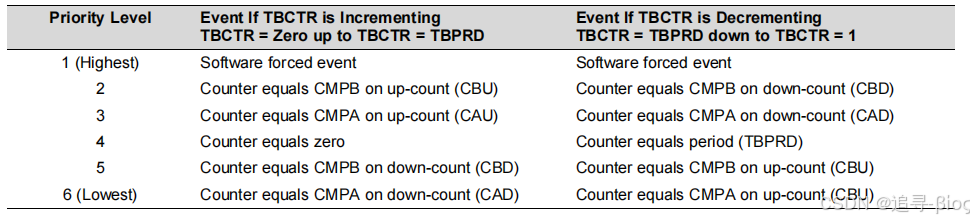

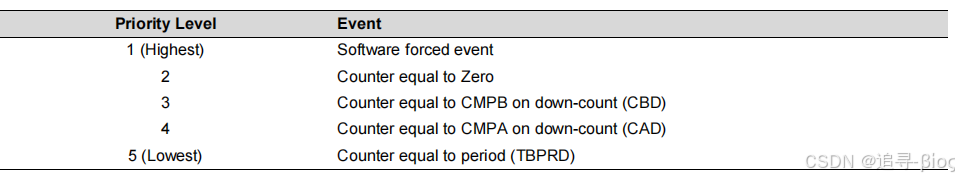

3.1 动作限定事件优先级

在同一时刻,AQ单元可能接收到多个事件,此处有硬件分频优先级。一般来说,较晚发生的事件具备较高优先级,软件强制事件具备最高优先级。

递增递减模式下优先级

递增模式下优先级

递减模式下优先级

另外,可以设置CMP的值大于周期值。

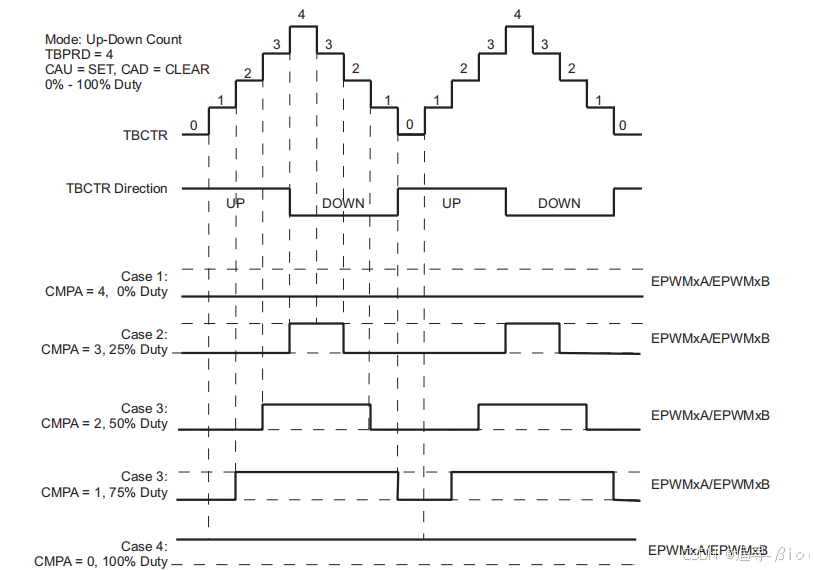

3.2 波形配置

注:在实际应用情况下,新写入的值发挥作用会延迟一个TBCLK或者原先的值发挥作用会需要一个额外的TBCLK。

例如,如果想CMPA/CMPB=0,那么就写大于或等于1的值到CMPA/CMPB寄存器。如果想CMPA/CMPB=TBPRD,那么就写小于或等于TBPRD-1的值到CMPA/CMPB寄存器。这表示当PWM周期很短时,总有至少一个TBCLK周期的脉冲,容易被系统忽略。

递增递减同步波形

由图可知,EPWMA和EPWMB在CTR=CMPA的后一时刻发送变化。

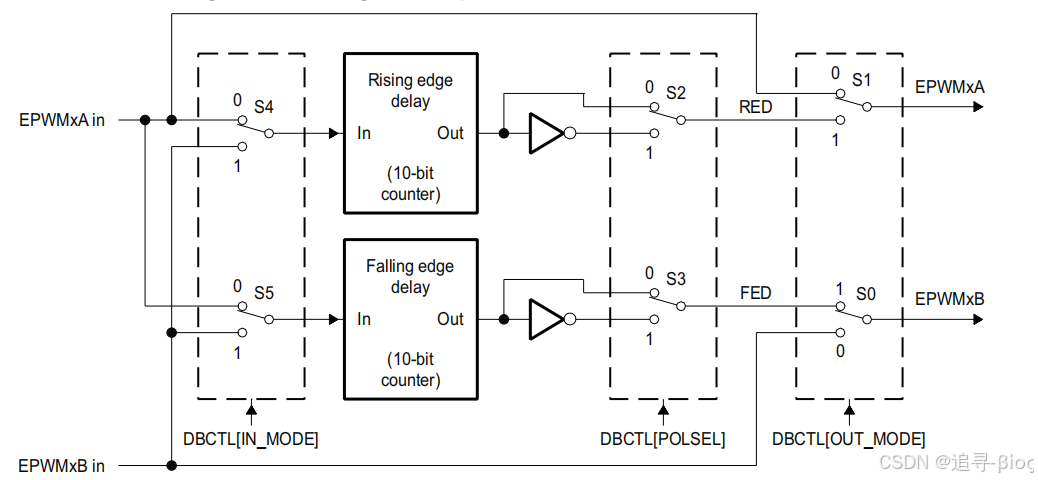

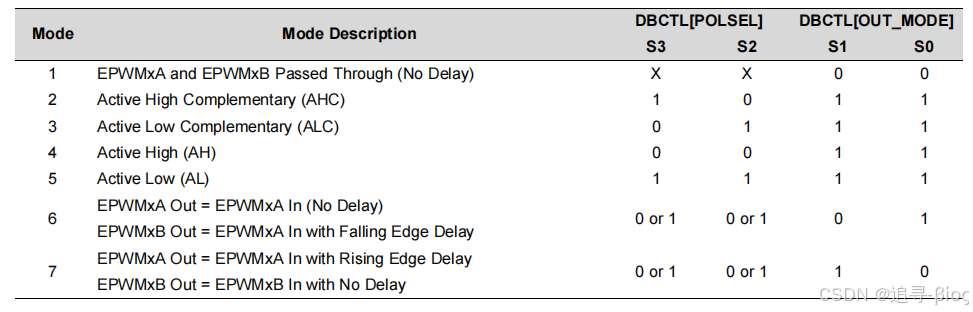

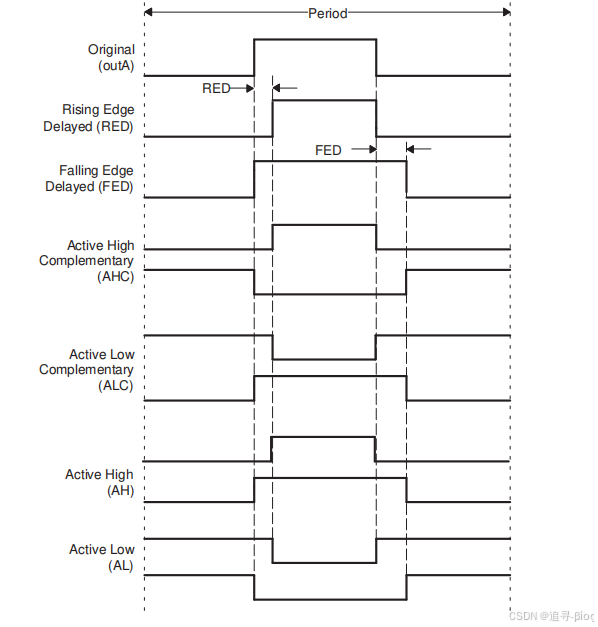

4、死区单元

该单元用于产生边缘延迟的带极性控制的死区。死区的重要功能有:从单个EPWMxA输入产生具有死带关系的信号对(EPWMxA和EPWMxB),如同为高,同为低,高电平互补,低电平互补,上升沿延迟,下降沿延迟。

死区单元有两组独立的选项:

输入源选择:

死区的输入信号为来自AQ单元的EPWMxA和EPWMxB输出。通过配置DBCTL.IN_MODE位,可以对输入信号进行选择处理。

如 EPWMxA是下降沿和上升沿延迟的源(默认模式);EPWMxA 为下降沿延迟源,EPWMxB为上升沿延迟源;EPWMxA 为上升沿延迟源,EPWMxB为下降沿延迟源;EPWMxB是下降沿和上升沿延迟的源。

输出模式控制:

通过配置DBCTL.OUT_MODE位来决定是否要上升沿延迟、下降沿延迟、都延迟或者都不延迟。

极性控制:

通过配置DBCTL.POLSEL位来决定是否要将上升沿延迟信号/下降沿延迟信号取反。

注:由图可知,通过DBCTL.OUT_MODE来决定要不要使用死区单元。

死区运行模式

注:可见对于一个死区输出信号来说,不能同时输出上升沿延迟和下降沿延迟。

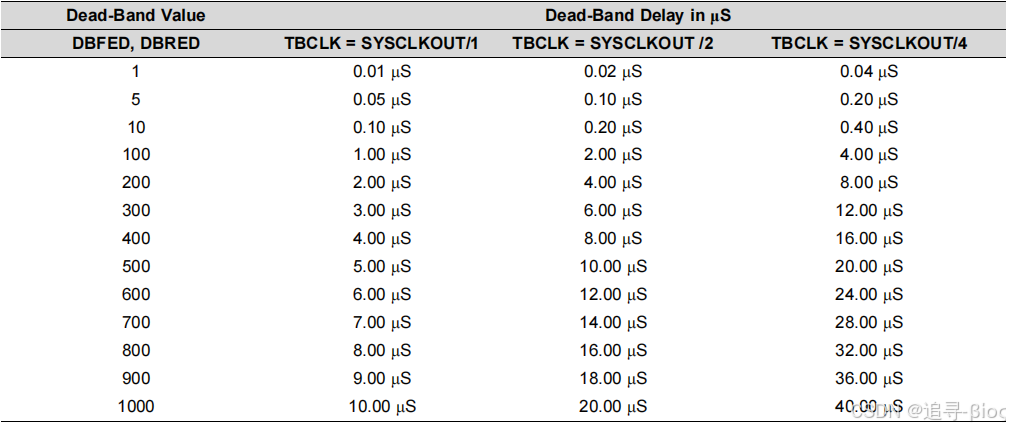

注:死区延迟时间基于TBCLK计数,即FED = DBFED×TBCLK,RED=DBRED×TBCLK。

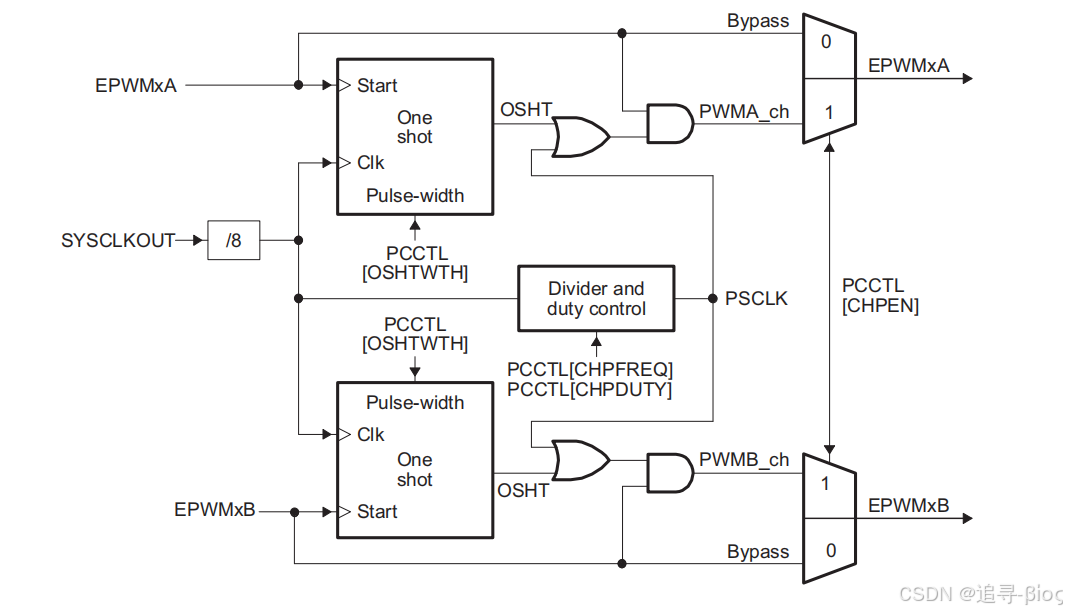

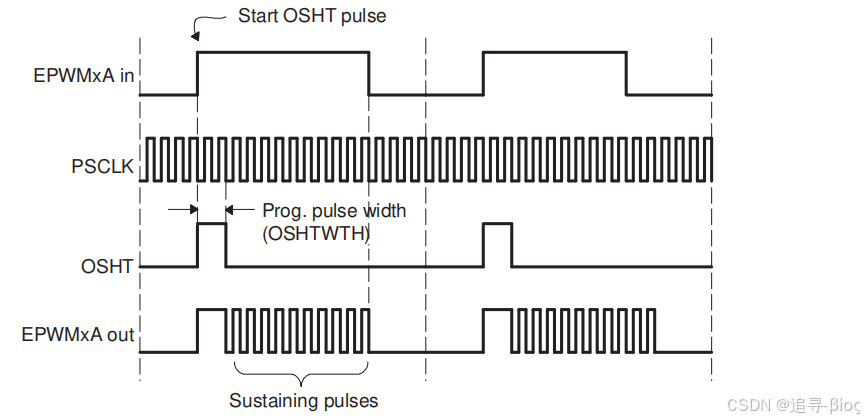

5、PWM斩波单元

PWM 斩波单元通过一个高频载波来修整PWM波形,对于控制电力电子开关十分重要。

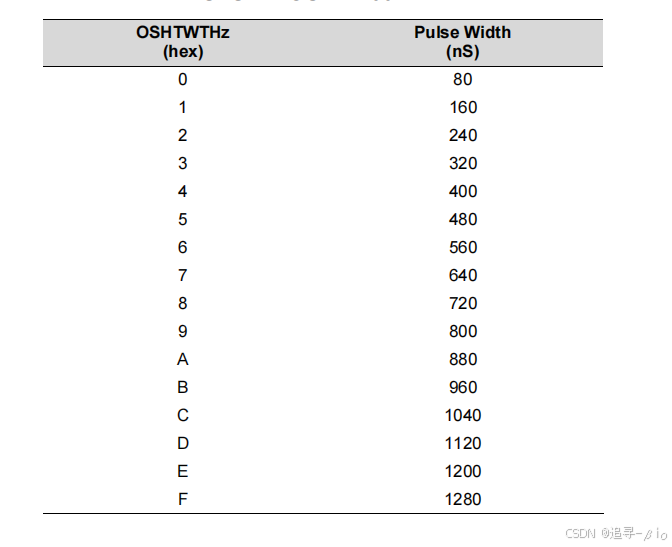

载波时钟来自于系统时钟SYSCLKOUT,通过PCCTL寄存器的CHPFREQ和CHPDUTY来控制频率和占空比。one-shot块可以提供第一个高能脉冲来确保开关开启,One-shot 脉冲宽度由OSHTWTH位来控制。

PWM斩波单元结构图

5.1 One-Shot 脉冲

第一个脉冲宽度可以配置成16种,T(first pluse)= SYSCLKOUT×8×OSHTWTH(4 bit)。

以SYSCLKOUT=100MHZ为例

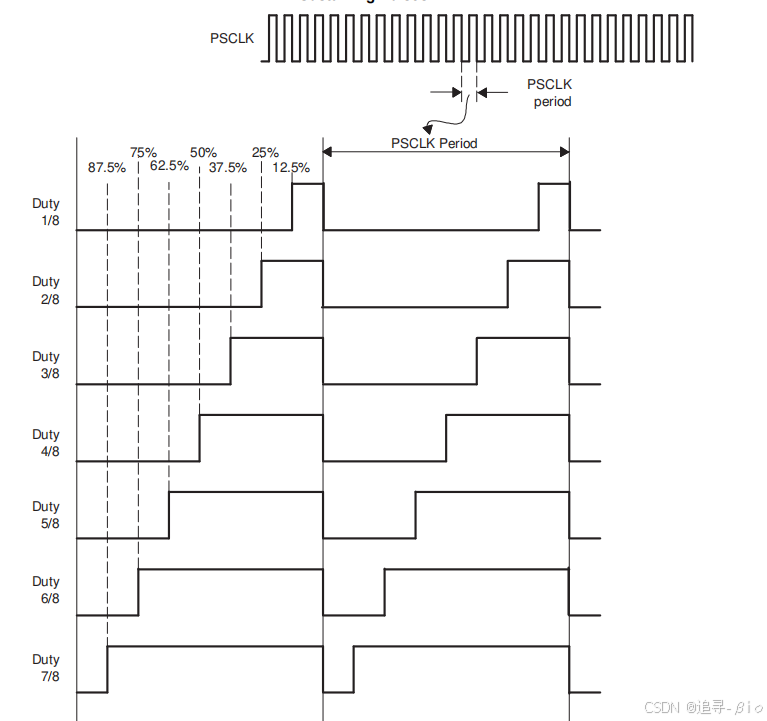

5.2 占空比控制

在第一个脉冲后,第二个脉冲以及随后的脉冲的占空比也是可变的,通过CHPDUTY位来实现。

注:PSCLK由系统时钟8倍分频得到,即为PC单元产生的高频载波,在此基础上调节展开比。

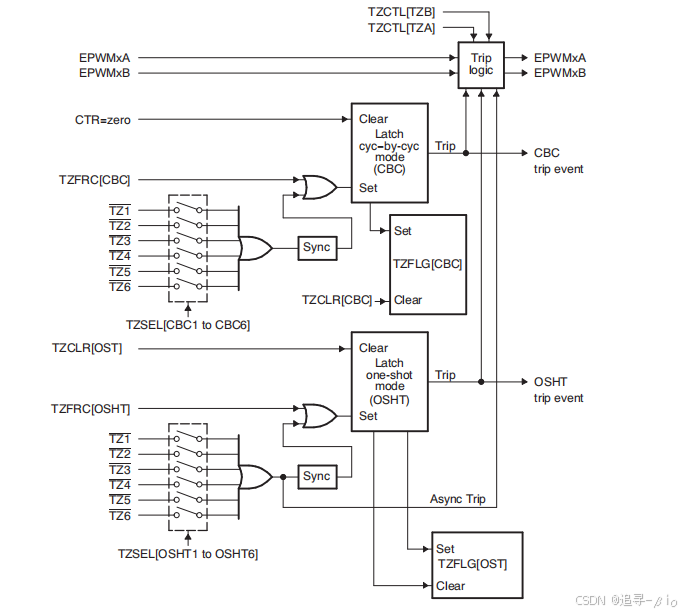

6、Trip-Zone(TZ)单元

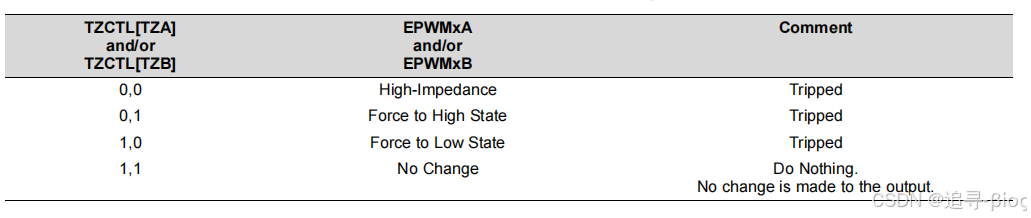

每个EPWM模块连接6个TZn信号(TZ1~TZ6,源于GPIO)。这些信号用于指示外部故障或者触发条件。当发送故障时,EPWM可以配置相应的输出,如拉低,拉高,高组态,不动作。

注:只有6个TZ输出映射到各个EPWM。

TZn信号有效电平为低电平。当其中一个引脚被拉低时,表明TZ事件产生。每个EPWM都可以配置使用或者忽略该信号,通过TZSEL寄存器来配置。TZn引脚输入至少保持1个SYSCLKOUT的低脉冲,足以满足触发条件。TZ引脚可以同步或者不同步系统时钟,但是异步可以确保在系统时钟丢失仍能够将信号输送到EPWM。

注:系统时钟丢失GPIO仍能检测引脚状态。

对于一个EPWM来说,每个TZn输入可以独立配置为周期性(cycle-by-cycle)触发或者一次性(one-shot)触发,通过TZSEL.CBC和TZSEL.OSHTn控制。

Cycle-by-Cycle(CBC):

当一个周期性触发事件产生时,TZCTL寄存器立即对EPWMxA/EPWMxB执行指定动作。另外,CBC触发标志位置起,如果使能TZEINT,则产生EPWM_TZINT中断。

如果触发事件不存在时,在时基计数器达到0时,会自动清除相应位。所以,在此模式下,触发事件会在每个PWM周期清除/复位。但是TZFLG.CBC标志位会保证置位,需手动清除。如果CBC触发事件仍存在,在清除标志位后又立即置起。

One-Shot(OSHT):

当发生一次性触发事件,TZCTL寄存器立即对EPWMxA/EPWMxB执行指定动作。另外,ONE-SHOT 触发标志位置起,如果使能TZEINT,则产生EPWM_TZINT中断。one-shot条件必须手动清除。

Trip事件输出动作

Trip-Zone单元逻辑图

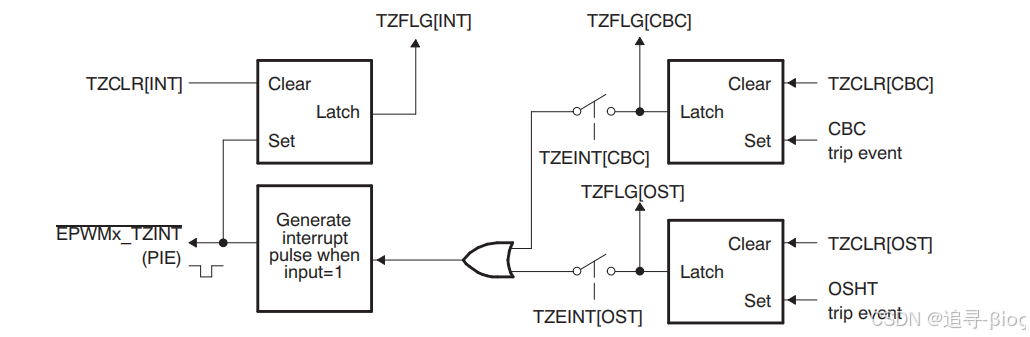

Trip-Zone单元中断逻辑

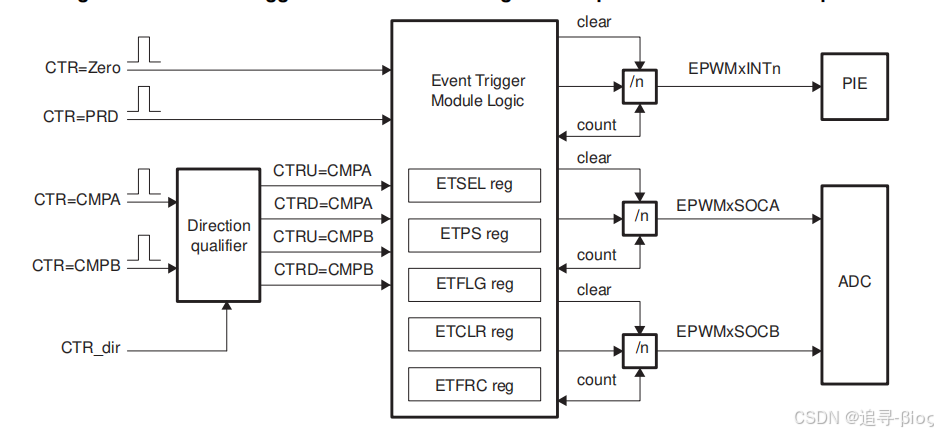

7、事件触发单元(Event-Trigger,ET)

事件触发单元用于管理时基单元和比较单元产生的事件,对应产生中断或者ADC启动转换脉冲。

每个EPWM模块有一条中断请求线连接到PIE和2个启动转换信号连接到ADC模块如例图。

注:如果两个启动转换请求同时产生,则只能一个被送入ADC。

事件触发单元结构图

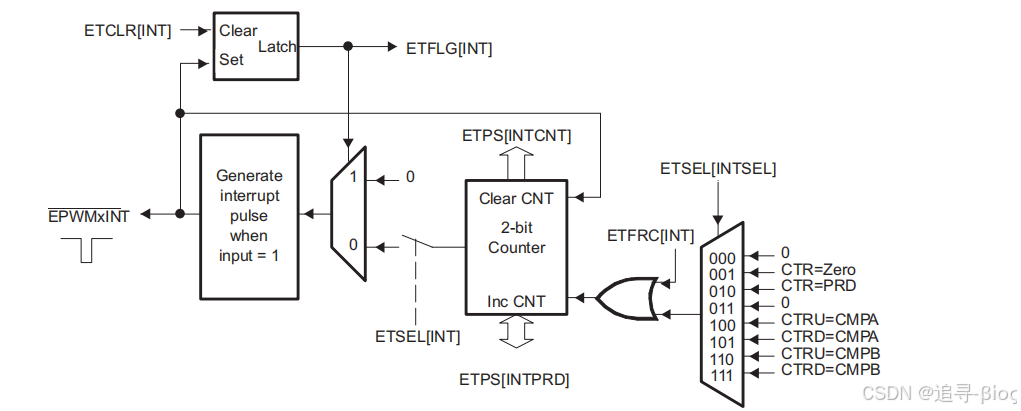

注:ETPS.INTPRD位可以指定产生一次中断的事件次数,如不产生中断、第一次事件、第二次事件、第三次事件。通过读取ETPS.INTCNT来获知事件产生的次数。当中断送入PIE时计数才清零。

如果中断使能,标志位清零,当中断产生时标志位置起,事件计数清零后重新计数。

如果中断禁能,标志位置起,当INTCNT=INTPRD时,事件计数器停止。

当中断使能,标志位已经置起,事件计数器保持高电平输出知道ENFLG.INT标志位清零。

对INTPRD位写入可以清零INTCNT,同时计数器输出复位,因此没有中断产生。向ETFRC.INT位写入1会使事件计数器值增1。当INTPRD=0时,计数器失效,不会检测到任何事件,ETFRC.INT失效。

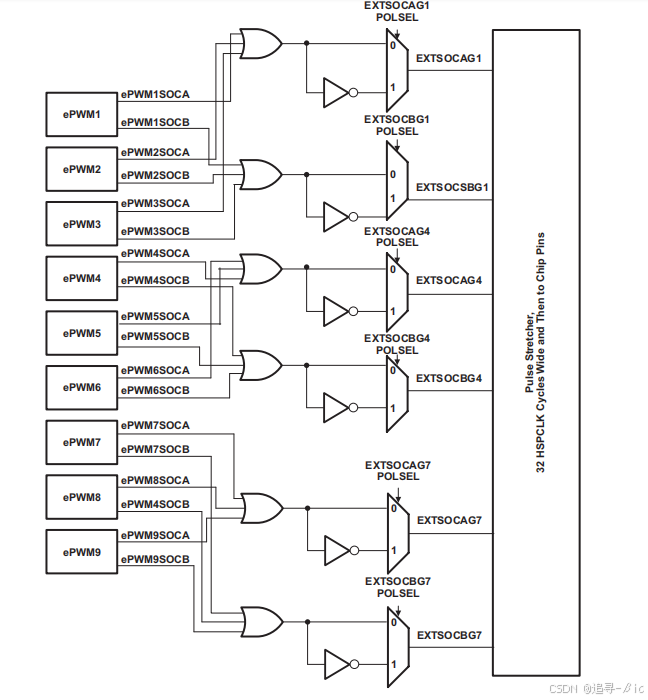

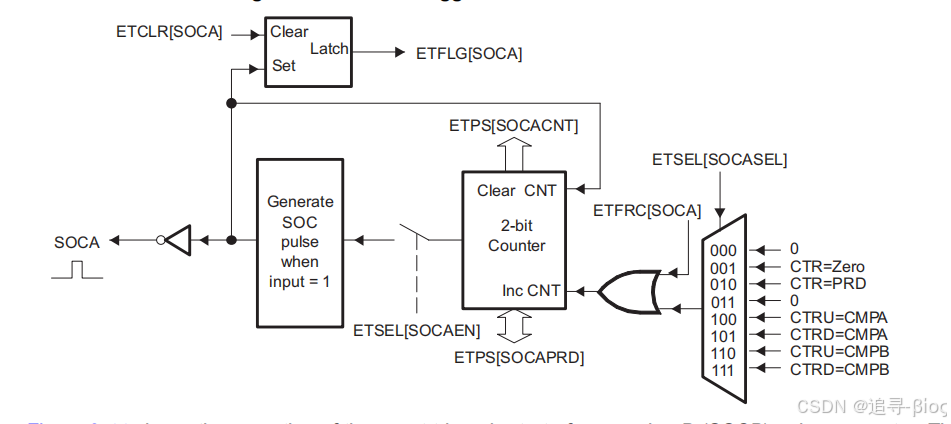

事件触发中断产生

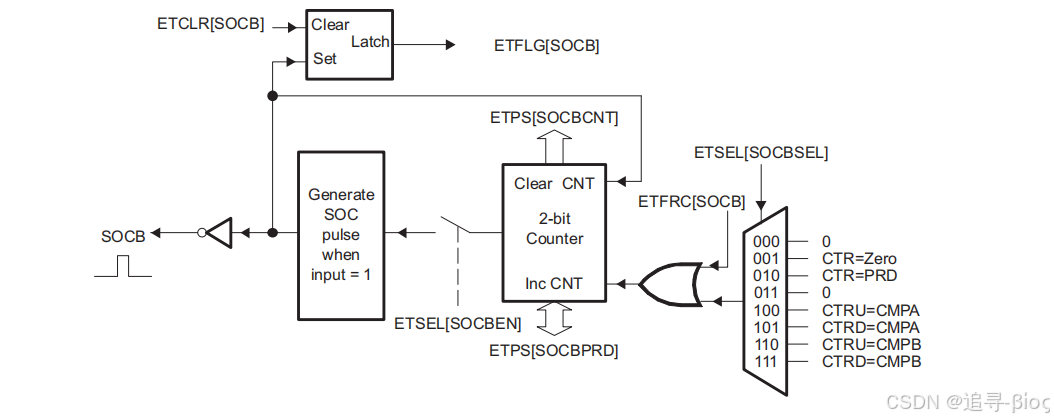

ETPS[SOCACNT]计数器和ETPS[SOCAPRD]周期值的行为与中断发生器相似,只是脉冲是连续产生的。也就是说,当脉冲产生时,脉冲标志ETFLG[SOCA]被锁存,但它不会停止进一步的脉冲产生。启用/禁用ETSEL[SOCAEN]位停止脉冲产生,但是输入事件仍然可以被计数,直到达到周期值。触发SOCA和SOCB脉冲的事件可以在ETSEL[SOCASEL]和ETSEL[SOCBSEL]位中分别配置。

事件触发SOCA脉冲产生

事件触发SOCB脉冲产生

2747

2747

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?