文章目录

一、ARM微处理器概述

1、ARM简介

ARM(Advanced RISC Machines),既可以认为是一个公司的名字,也可以认为是对一类微处理器的通称,还可以认为是一种技术的名字。

ARM处理器支持Thumb(16位)和ARM(32位)双指令集,大多数数据操作都在寄存器中完成,并且指令长度固定、寻址方式灵活简单,指令执行速度更快、效率更高。

2、ARM处理器系列

(1)基于指令集体系结构版本分类:v1,v2,v5,v6,v7,v8,v9等。

(2)基于ARM体系结构设计的处理器系列分类:ARM7,ARM9,ARM10,ARM11,StrongARM,XScale等。

(3)ARM处理器命名规则

| 标志 | 含义 | 说明 |

|---|---|---|

| T | 支持Thumb指令集 | 不同的版本支持的Thumb指令集版本可能不同 |

| D | 支持片上调试 | 一个边界扫描链 JTAG,可使 CPU 进入调试模式 |

| M | 支持快速乘法器 | 32位乘32位得到64位,32位的乘加得到64位 |

| I | 支持Embedded ICE | 嵌入式跟踪宏单元,用于实现断点观测及变量观测 |

| E | 支持增强型DSP指令 | 增加了DSP算法处理器指令,包括16位乘加指令,饱和的带符号数的加减法,双字数据操作,cache预取指令 |

| J | 支持Jazelle | 即Java加速器,提高java代码的运行速度 |

| S | 可综合版本 | 提供VHDL或Verilog语言设计文件 |

3、CISC与RISC

(1)CISC: 即复杂指令集计算机(Complex Instruction Set Computer),随着计算机技术的发展,不断引入新的复杂的指令到指令集中,为支持这些新增的指令,计算机的体系结构会越来越复杂。然而,在CISC指令集的各种指令中,约20%的指令会被反复使用,占整个程序代码的80%,而余下的80%的指令却不经常使用,在整个程序代码中只占20%。

(2)RISC: 即精简指令集计算机(Reduced Instruction Set Computer),为了解决CISC的不合理性,RISC被提出,它只要求硬件执行很有限且最常用的那部分指令,大部分复杂的操作则使用成熟的编译技术,由简单指令合成。从而使计算机的结构更加简单,提高了运算速度。其特点如下:

- 指令规整、对称、简单

- 指令字长度一致,单拍完成,便于流水操作

- 拥有大量的寄存器

(3)两者区别:

| 类别 | CISC | RISC |

|---|---|---|

| 指令系统 | 指令数量很多 | 通常不超过100条 |

| 执行时间 | 执行时间有些很短、有些很长 | 没有执行时间较长的指令 |

| 编码长度 | 长度可变,1~15字节 | 编码长度固定,通常位4字节 |

| 寻址方式 | 根据指令决定,多种多样 | 所有指令共用一套简单寻址规则 |

| 操作 | 可以对存储器和寄存器进行算术和逻辑操作 | 只能对寄存器对行算术和逻辑操作,Load/Store体系结构 |

| 编译 | 难以用优化编译器生成高效的目标代码程序 | 采用优化编译技术,生成高效的目标代码程序 |

4、指令集

(1)ARM指令集概述: ARM指令集是32位指令集,可分为5大类指令,所有指令都可以条件执行,其中一些指令还可以根据执行结果更新CPSR寄存器的相关标志位。分类如下:

- 数据处理指令:MOV、AND、SUB、ADD等;

- 加载和存储指令: LDR、STR、LDM、STM等;

- 分支指令: B、BX等;

- 协处理器指令: LDC、STC等;

- 杂项指令: SWI、 MRS、MSR等;

(2)Thumb指令集概述: Thumb指令集是16位指令集,是ARM指令集的子集,按16位指令重新编码,可分为4大类,如下:

- 分支指令;

- 数据处理指令;

- 寄存器加载和存储指令;

- 异常产生指令;

二、ARM微处理器体系结构

1、数据类型

体系结构直接支持的数据类型有三种,分别为:

- 字节(Byte):在ARM体系结构和8位/16位处理器体系结构中,字节的长度均为8位。

- 字(Word):在ARM体系结构中,字的长度为32位,必须分配为占用4个字节。而在8位/16位处理器体系结构中,字的长度一般为16位。

- 半字(Half-Word):在ARM体系结构中,半字的长度为16位,必须分配为占用两个字节。与8位/16位处理器体系结构中字的长度一致。

2、ARM微处理器的工作状态

ARM微处理器的工作状态一般有两种:

- ARM状态:处理器执行32位的字对齐的ARM指令,伪指令CODE32声明;

- Thumb状态:处理器执行16位的、半字对齐的Thumb指令,伪指令CODE16声明;

3、ARM体系结构的存储器格式

ARM体系结构可以用两种方法存储字数据,分别为大端格式和小端格式,ARM默认小端格式,但用户可自行设置大、小端格式。区别如下:

- 大端格式:字数据的高字节存储在低地址中,而字数据的低字节则存放在高地址中;

- 小端格式:字数据的高字节存储在高地址中,而字数据的低字节则存放在低地址中;

4、ARM微处理器的模式

(1)简介: ARM体系结构支持7种处理器模式,如下表所示:

| 处理器模式 | 说明 | **备注 ** |

|---|---|---|

| 用户(usr) | 正常程序工作模式 | 不能直接切换到其它模式 |

| 系统(sys) | 用于支持操作系统的特权任务等 | 与用户模式类似,但具有可以直接切换到其它模式等特权 |

| 快中断(fiq) | 支持高速数据传输及通道处理 | FIQ异常响应时进入此模式 |

| 中断(irq) | 用于通用中断处理 | IRQ异常响应时进入此模式 |

| 管理(svc) | 操作系统保护代码 | 系统复位和软件中断响应时进入此模式 |

| 中止(abt) | 用于支持虚拟内存和/或存储器保护 | 预取中止和数据中止 |

| 未定义(und) | 支持硬件协处理器的软件仿真 | 未定义指令异常响应时进入此模式 |

(2)特权模式: 特权模式并不是一个具体的模式,它表示除用户模式外的其它模式,它比用户模式拥有更高的权限,可以访问ARM内部寄存器(通常情况下用户模式不能),也可以自由的切换处理器模式,而用户模式不能主动切换成其它模式。

(3)异常模式: 异常模式同样并不是一个具体的模式,它表示除用户和系统模式以外的其它模式,它除了可以由其它模式切换进入,也可以由特定的异常进入,并且在该模式下,不同的异常模式的部分寄存器会区别于其它模式,以避免异常退出时用户模式的状态不可靠。

5、ARM微处理器的寄存器组织

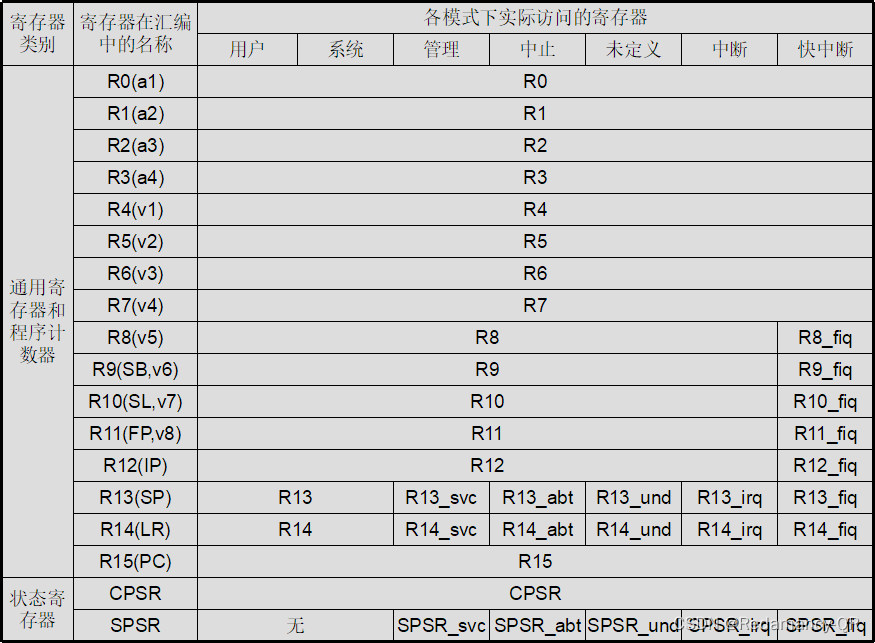

(1)简介: ARM处理器有37(31+6)个物理寄存器, 31个通用寄存器和6个状态寄存器,如下图所示:

由上图可以看出寄存器被安排成部分重叠的组,在不同的工作模式和处理器状态下,程序员可以访问的寄存器不尽相同。分组的寄存器在处理“处理器异常”和“特权操作”时可以快速地上下文切换。

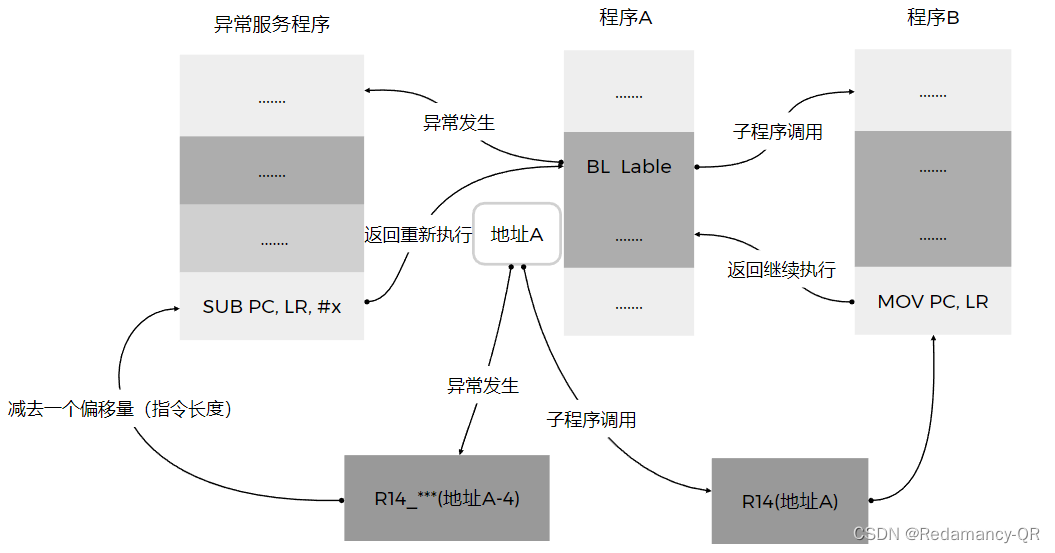

(2)R14: 该寄存器为链接寄存器(LR),在结构上有两个特殊功能:

1)在每种模式下,模式自身的R14版本用于保存子程序返回地址;

2)当发生异常时,该模式下的R14被设置成该异常模式将要返回的地址。

上图为当子程序调用或异常发生时的流程图,可以概括为三步:

1)硬件将当前指令的下一条指令地址A存入LR寄存器,区别在于一个存入R14一个存入R14_***,这样可以保整用户模式的可靠。

2)跳转执行子程序或IRQ服务程序。

3)返回原处继续执行,区别在于子程序直接执行下一条指令,异常发生时要重新执行当前指令(通过减去偏移量实现,x具体的值由异常类型决定)。

(3)状态寄存器:

寄存器CPSR为“程序状态寄存器”,在异常模式中,寄存器SPSR称为“程序状态保存寄存器”。每种异常都有自己的SPSR,在异常事件而进入时,它保存CPSR的当前值,异常退出时通过它恢复CPSR寄存器的值。CPSR寄存器各位含义如下:

| 地址 | 标志 | 含义 | 说明 |

|---|---|---|---|

| 0~4 | M0-4 | 模式位 | 指示处理器的模式,同时可以通过设置该位域来修改处理器的模式 |

| 5 | T | 状态位 | 指示处理器使用什么指令集,该位为1时表示使用Thumb,为0时表示使用ARM |

| 6 | F | FIQ控制位 | 是否屏蔽FIQ,该位为1时表示屏蔽FIQ,为0时表示打开FIQ |

| 7 | I | IRQ控制位 | 是否屏蔽IRQ,该位为1时表示屏蔽IRQ,为0时表示打开IRQ |

| 8~27 | — | — | 取决于处理器版本,为保留位或其它含义 |

| 28 | V | 溢出标志 | 当进行加法运算,并且发生有符号溢出时V=1,否则V=0 |

| 29 | C | 进位或借位扩展 | 当进行加法运算,并且最高位产生进位时C=1,否则C=0。当进行减法运算,并且最高位产生借位时C=1,否则C=0。对于移位操作指令,C为从最高位最后移出的值,其它指令C通常不变; |

| 30 | Z | 零标志位 | 指令结果为0时Z=1(表示比较结果“相等”),否则Z=0; |

| 31 | N | 负或小于标志位 | 运算结果的最高位反映在该标志位。对于有符号二进制补码,结果为负数时N=1,结果为正数或零时N=0; |

M0-4位的值与处理器模式对应关系如下:

| M0-4 | 模式 | M0-4 | 模式 |

|---|---|---|---|

| 10000 | 用户 | 10111 | 中止 |

| 10001 | 快中断 | 11011 | 未定义 |

| 10010 | 中断 | 11111 | 系统 |

| 10011 | 管理 |

状态寄存器有专门的访问指令,分别为:

- MRS: 状态寄存器到通用寄存器的传送指令(读状态寄存器)

- MSR: 通用寄存器到状态寄存器的传送指令(写状态寄存器)

MRS和MSR指令可以实现对状态寄存器的读、修改、写操作,即修改状态寄存器的值。使用方法如下:

- MRS R1, CPSR ->读取CPSR保存到通用寄存器R1

- MSR CPSR, R1 ->传送R1到CPSR

6、ARM微处理器的异常

(1)简介: 只要正常的程序流被暂时中止,处理器就进入异常模式。如果同时发生两个或更多异常,那么将按照固定的顺序来处理异常。异常类型如下:

| 异常类型 | 模式 | 向量地址 |

|---|---|---|

| 复位 | 管理 | 0x00000000 |

| 未定义指令 | 未定义 | 0x00000004 |

| 软件中断(SWI) | 管理 | 0x00000008 |

| 预取中止(取指令存储器中止) | 中止 | 0x0000000C |

| 数据中止(数据访问存储器中止) | 中止 | 0x00000010 |

| IRQ(中断) | IRQ | 0x00000018 |

| FIQ(快速中断) | FIQ | 0x0000001C |

异常优先级关系如下:

| 异常类型 | 优先级 |

|---|---|

| 复位 | 1(最高优先级) |

| 数据中止 | 2 |

| FIQ | 3 |

| IRQ | 4 |

| 预取中止 | 5 |

| 未定义指令 | 6 |

| SWI | 6(最低优先级) |

(2)异常处理流程:

1)进入异常: 在异常发生后,ARM内核会做以下工作:

a.在适当的LR中保存PC-4的地址;

b.将CPSR复制到适当的SPSR中;

c.(可选)置位中断禁止标志(CPSR 第1位置1),这样可以防止不受控制的异常嵌套;

d.如果当前为Thumb模式,则清零T位,强制进入ARM模式;

e.将CPSR模式位强制设置为与异常类型相对应的值;

f.强制PC从相关的异常向量处取指;

2)退出异常:

a.将对应的SPSR的值复制回CPSR;

b.将CPSR模式位设置为原模式相对应的值;

c.如果当前为Thumb模式,则将T位置1,重新进入Thumb模式;

d.若在进入异常处理时设置了中断禁止标志(I/F位)则清零该标志。

e.将对应的LR中的值减去偏移量后存入PC,偏移量根据异常的类型而有所不同;

(3)异常类型及相关返回指令:

本文详细介绍了ARM微处理器的概述,包括其发展历程、指令集特性、CISC与RISC的区别,以及ARM体系结构的详细内容,如数据类型、工作状态、寄存器组织和异常处理流程。

本文详细介绍了ARM微处理器的概述,包括其发展历程、指令集特性、CISC与RISC的区别,以及ARM体系结构的详细内容,如数据类型、工作状态、寄存器组织和异常处理流程。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?