一、简介

利用直观换效率,利于逻辑优化电路

语言分为:VHDL和Verilog HDL。Verilog语言比较简单。(类比c和py?)

二、综合和仿真

语言描述硬件,软件为综合器。描述完用综合器对代码解释并转化为电路,即综合。

仿真器来仿真测试文件,用仿真器进行输入,看功能出来的信号是否为目标信号,即仿真。

程序映射成电路结构可实现,称之为可综合语法。反之,不可综合语法。

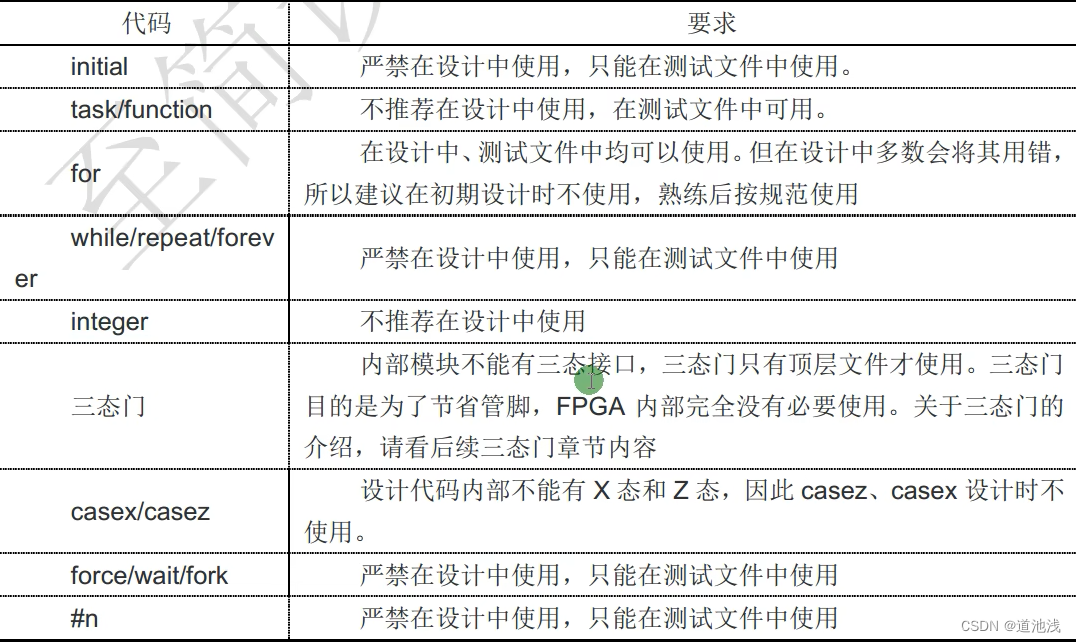

不可综合或不推荐使用的代码

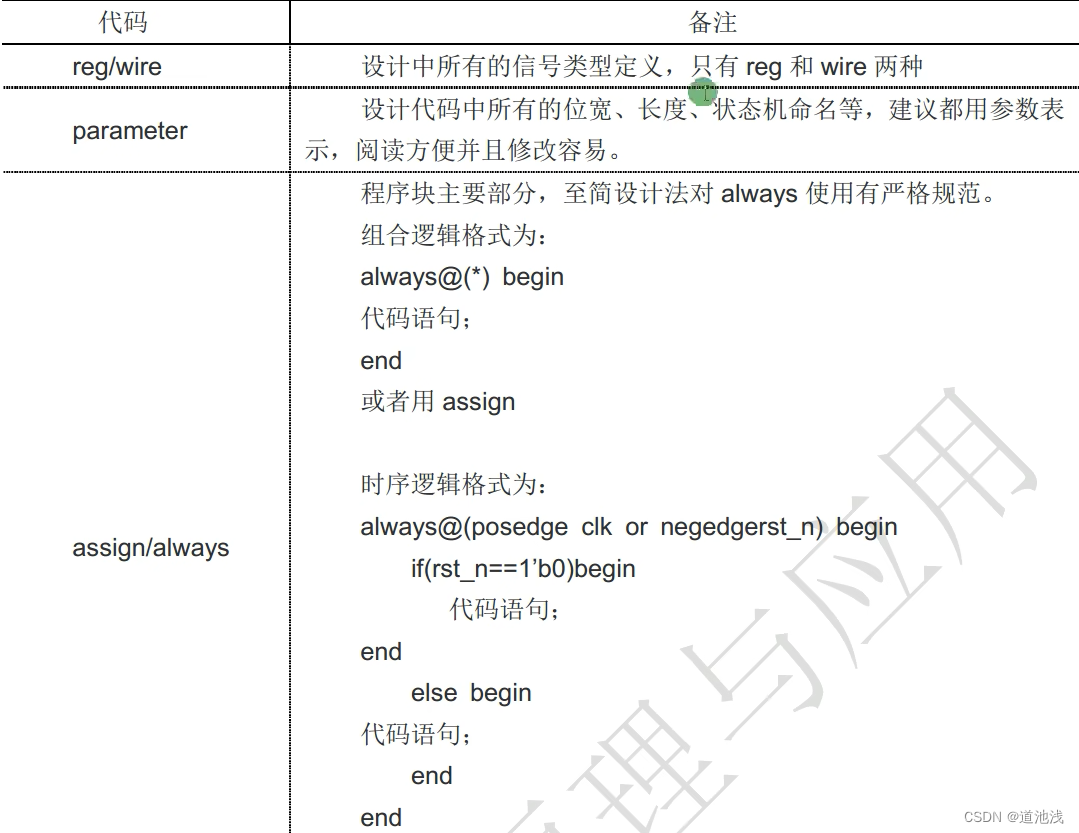

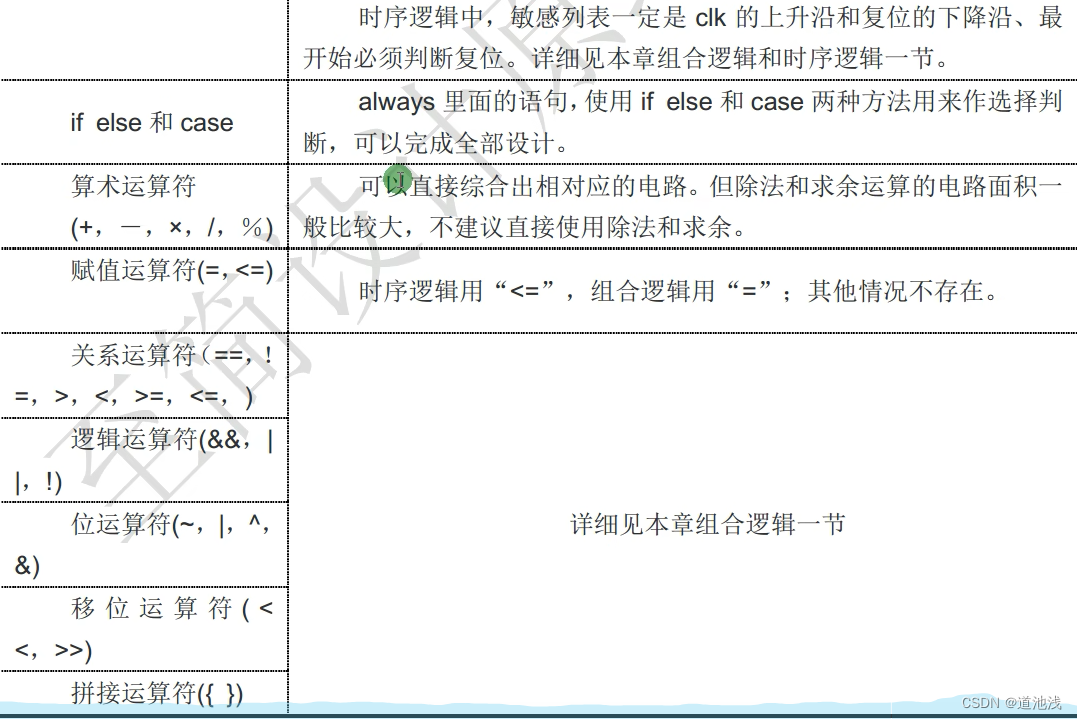

推荐使用代码及说明

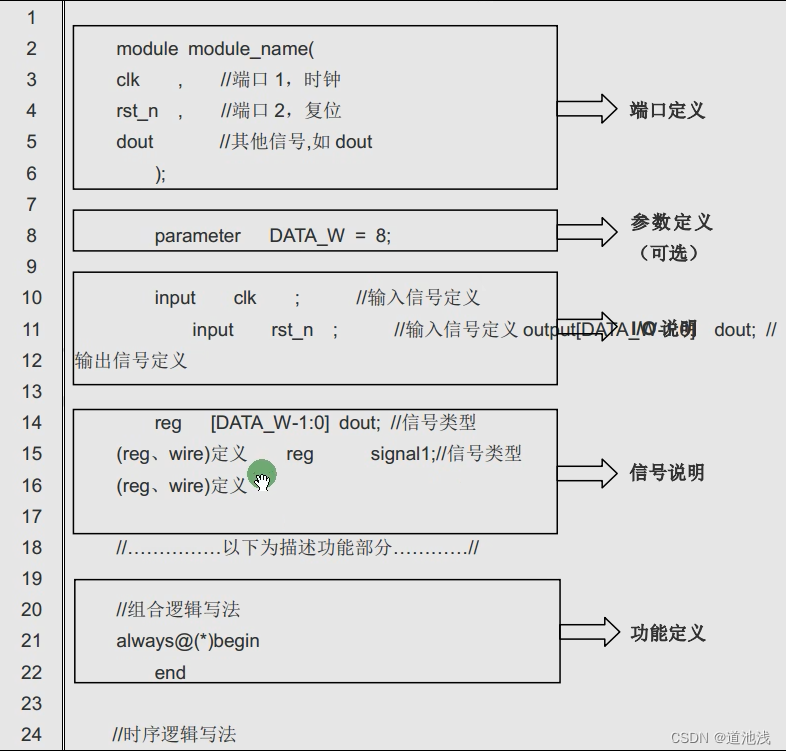

三、模块结构

模块化设计,小模块实现功能,顶层模块调用子模块。

端口定义(类比结构体):

关键词 module 表示模块名,内部定义端口,类比结构体的结构

函数定义(类比宏定义):

关键词 parameter,类比 #define

思维差异:计算机思维是0开始,人的思维是1开始。如果是位宽为8,那么我们可以parameter cnt=8;在使用到它时换成[cnt-1 : 0](即0-7)

接口定义(类比函数类型定义):

输入端口:input[信号位宽-1 : 0] 端口名 1:

input[信号位宽-1 : 0] 端口名 2:

......

输出端口:output[信号位宽-1 : 0] 端口名 1:

output[信号位宽-1 : 0] 端口名 2:

......

输入端口:output[信号位宽-1 : 0] 端口名 1:

output[信号位宽-1 : 0] 端口名 2:

......

信号类型(类比函数声明):

reg[width-1 : 0] R变量1,R变量2......; 寄存器类型 仅在always设计的信号定义为reg

wire[width-1 : 0] W常量1,W常量2......; 线网类型 其他定义为wire

默认值:wire类型,位宽为1

类比函数声明,使用函数前要用函数头申明,默认为void-void。

信号位宽:默认信号位宽1位(即1bit),位宽取决于信号表达的最大值,能表达2^n -1,n为位宽。例如:max为1000,n就得>=10。

可以在电脑的计算器的程序员模式下的十进制输入信号值(如1000)可查看

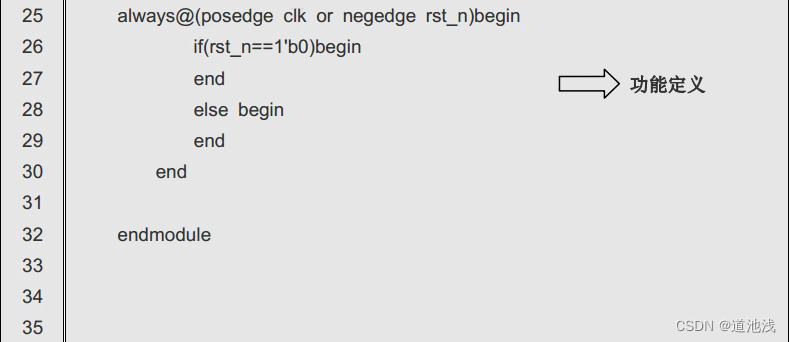

功能定义(语法):

通常用always和assign构成

模块例化:

【名字关联】

例:mdy u_mdy (

.clk (Clk),

.rst (Rst),

.preset( ),管脚悬空

.......

);

左侧有"."符号的接口名为源文件的接口,右侧括号里为外部连接的信号

总结

提示:这里对文章进行总结:

例如:以上就是今天要讲的内容,本文仅仅简单介绍了pandas的使用,而pandas提供了大量能使我们快速便捷地处理数据的函数和方法。

6447

6447

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?