(1)掌握1位全加器的实现逻辑,掌握多位可控减法器电路的实现逻辑;

(2)掌握先行进位的原理,能够利用相关知识设计4位先行进位电路,并利用设计的4位先行进位电路构造4位快速加法器;

(3)理解成组进位生成函数、成组进位传递函数的概念,能利用4位先行进位电路和4位快速加法器电路构建16位、32位快速加法器;

(4)理解算术逻辑运算单元(ALU)的基本组成,能利用已完成的32位加法器、Logisim中的运算组件构造指定规格的ALU;

(5)掌握阵列乘法器的实现原理,能够分析阵列乘法器的性能,并能设计实现阵列乘法器电路;

(6)掌握原码一位乘法运算的基本原理,设计实现一个8位×8位的无符号数一位乘法器电路;

(7)掌握补码一位乘法运算的基本原理,并能设计实现一个8位×8位的补码一位乘法器电路;

(8)掌握运算流水基本概念,理解将复杂运算步骤细分成子过程的思想,能够实现简单的乘法运算流水线。

二、实验内容

(1)可控加减法电路设计实验:在对应子电路中,利用已经封装好的全加器设计8位串行可控加减法电路

(2)4位快速加法器设计实验

①4位先行进位电路:在对应子电路中利用基本逻辑门实现可级联的4位先行进位电路

②4位快速加法器:在4位快速加法器子电路中利用已经设计好的4位先行进位电路以及基本逻辑门实现4位快速加法器

(3)多位快速加法器设计实验

①16位快速加法器设计

②32位快速加法器设计

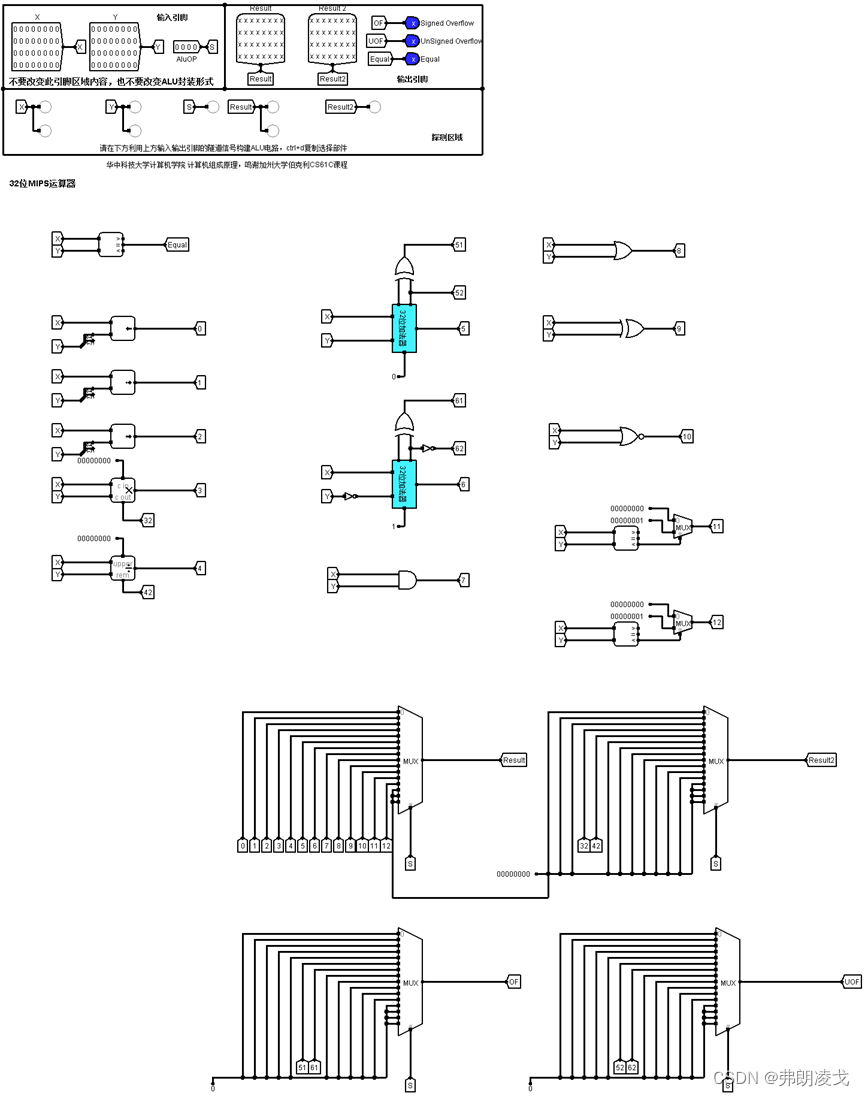

(4)32位ALU设计实验

(5)阵列乘法器设计实验

①5位无符号阵列乘法器设计:在对应的子电路中实现5位无符号阵列乘法器

②6位补码陈列乘法器设计:在对应的子电路中利用已经设计好的5位阵列乘法器实现6位补码阵列乘法器

(6)原码一位乘法器设计实验:在对应子电路中利用寄存器、加法器等基本电路设计无符号一位乘法器

(7)补码一位乘法器设计实验:在对应子电路中利用寄存器、加法器等基本电路设计8位补码一位乘法器

(8)乘法流水线设计实验

三、实验工具

Logisim仿真实验软件

四、方案设计与实验步骤及结果

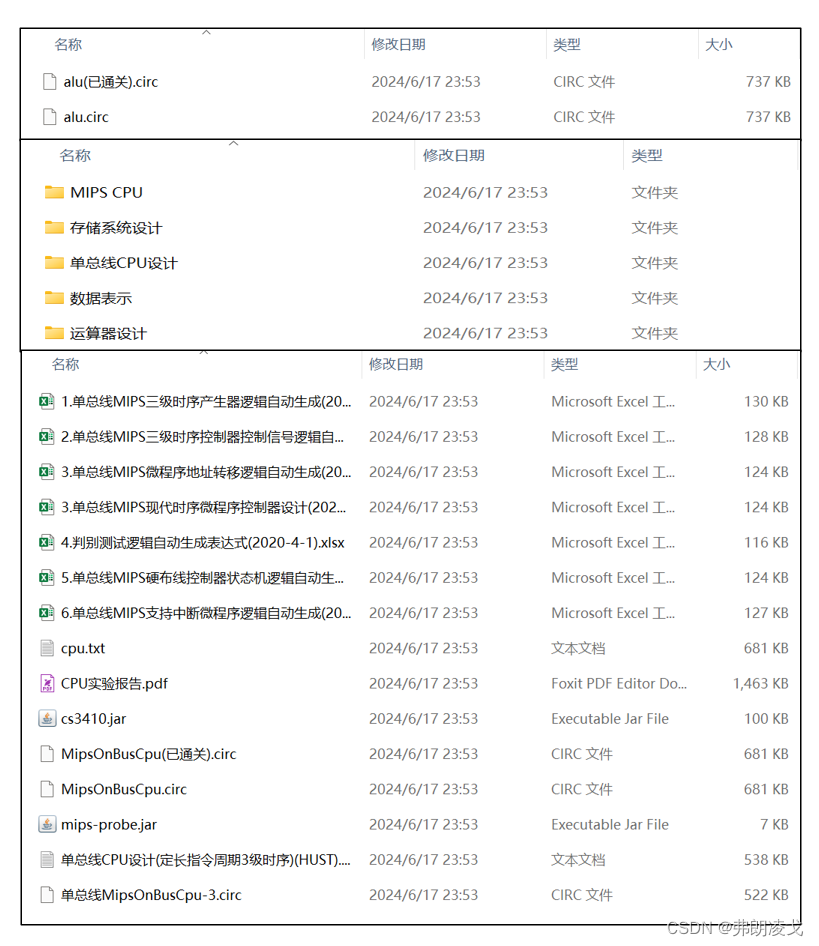

|

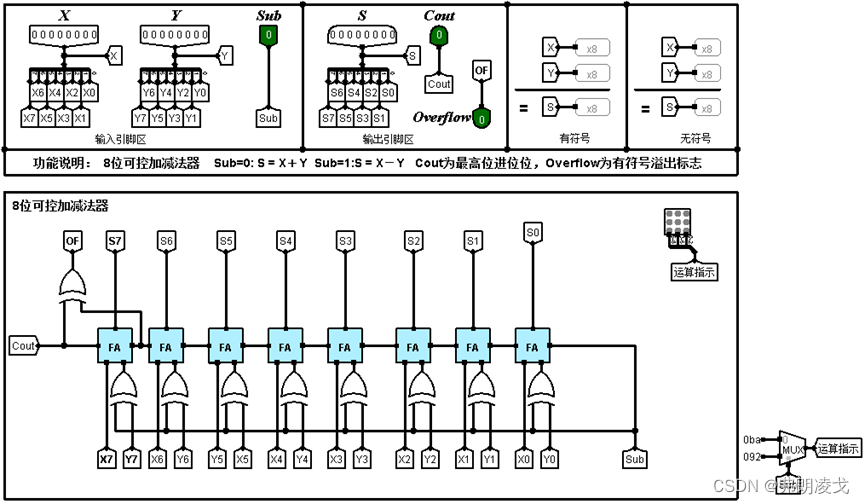

图表 1 |

(1)可控加减法电路设计实验

补码的符号位参与运算。对于无符号数的加法运算,溢出符号就是Cn;对于有符号数的溢出检测信号overflow,可以直接用最高位数值进位和符号位进位异或得到。将8个全加器的进位链串联即可得到8位串行加法器。可控电路实现如图表1所示。

(2)4位快速加法器设计实验

①4位先行进位电路

n位串行加法电路中和数与进位输出的逻辑表达式如下:

Si=Xi⊕Yi⊕Ci Ci+1=XiYi+(Xi⊕Yi)Ci

假设Gi=XiYi, Pi= Xi⊕Yi。当Gi=1时,Ci+1一定为1,所以将Gi称为进位生成函数;当Pi=1时,进位信号Ci才能传递到进位输出Ci+1处,所以称Pi为进位传递函数。有了进位生成函数和进位传递函数,则有以下公式:

Si=Pi⊕Ci Ci+1=Gi+PiCi

电路实现结果如图表2所示。

|

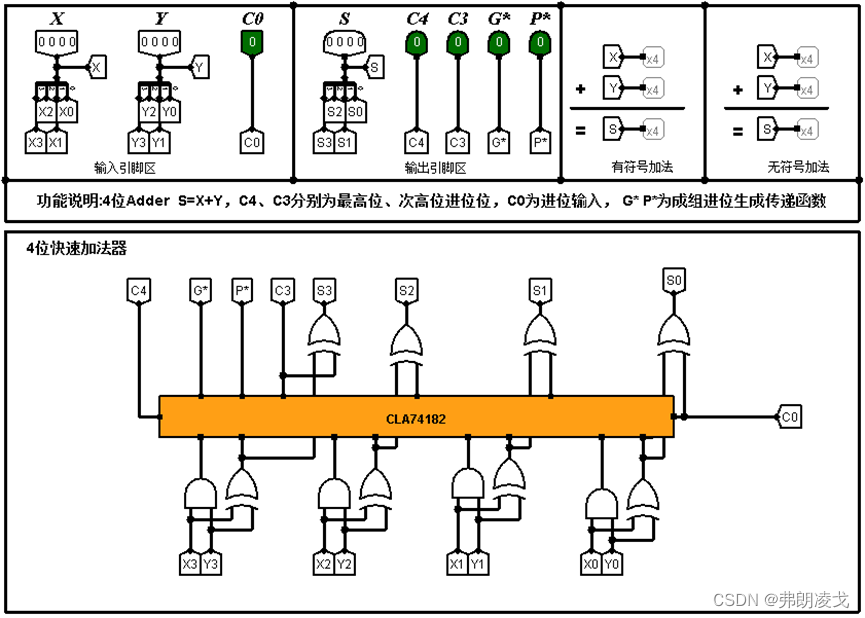

图表 2 |

②4位快速加法器

4位先行电路,加上生成Gi,Pi的与门异或门电路,再加上4个异或门就可以构成4位快速加法器,也称为并行加法器。电路实现结果如图表3所示。

图表 3

图表 3

(3)多位快速加法器设计实验

①16位快速加法器设计

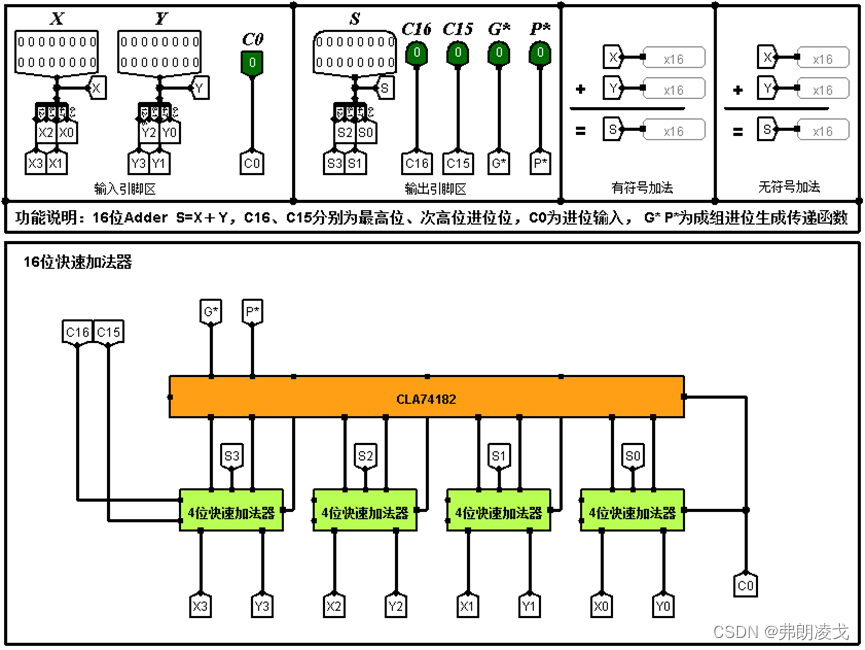

利用先行进位电路提前产生C4、C8、C12、C16信号,将4个4位快速加法器输出的成组进位生成、传递函数G*和P*及C0连接到先行进位电路的输入端,再将对应信号连接到相应的快速加法器的进位输入端即可构成16位组内并行进位、组间并行进位的快速加法器,实现结果如图表4所示。

图表 4

图表 4

②32位快速加法器设计

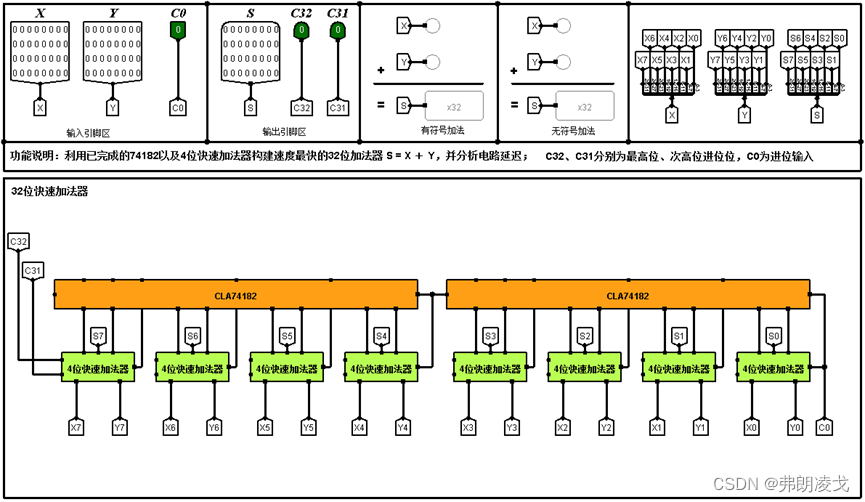

在实现16位快速加法器的基础上,将16位快速加法器进行组间串联连接即可实现32位快速加法器,实现结果如图表5所示。

|

图表 5 |

电路实现结果如图标6所示。

图表 6

图表 6

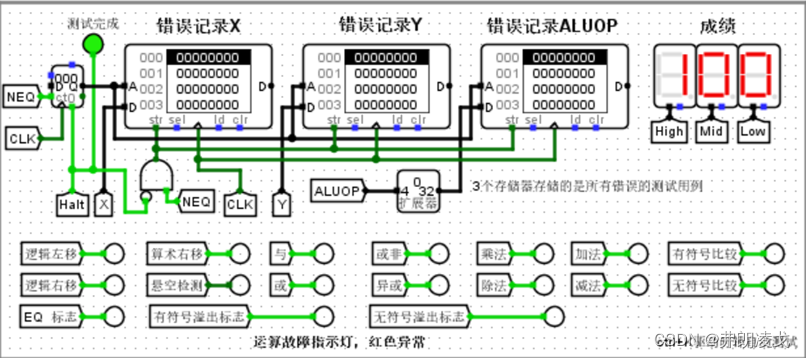

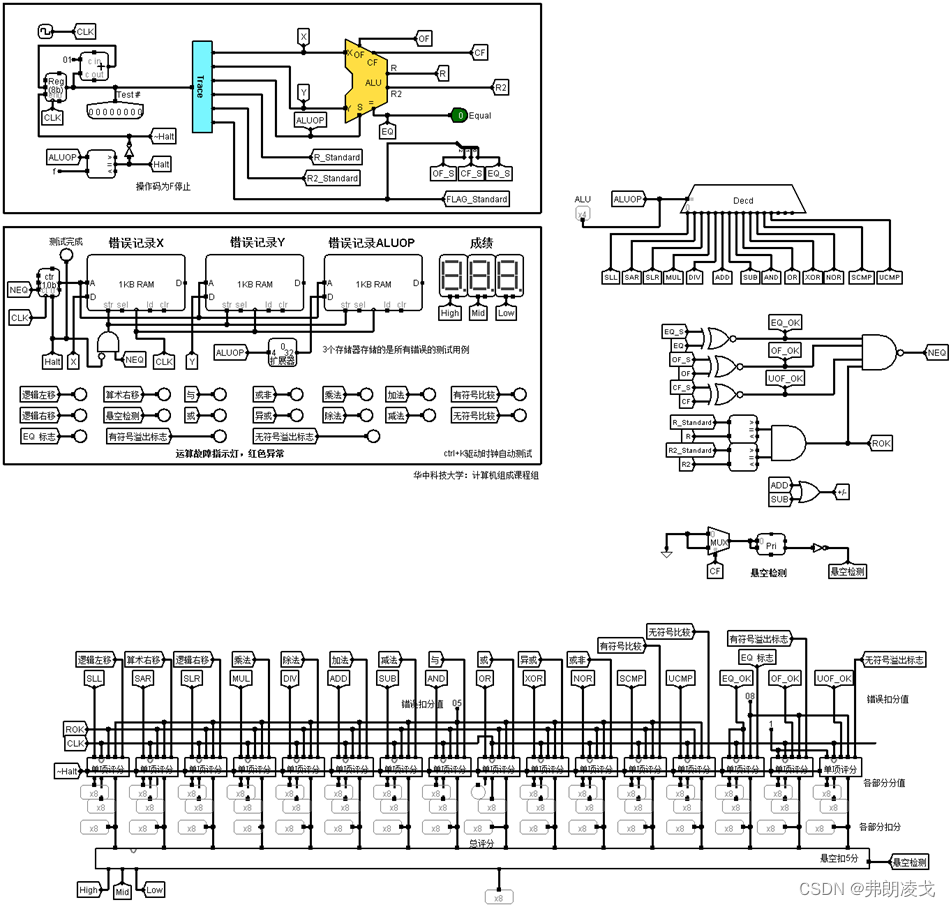

通过给出的ALU自动测试电路进行测试,不断修改错误,直到出现正确的实验结果。实验结果如图表7、8所示。

|

图表 7 |

|

图表 8 |

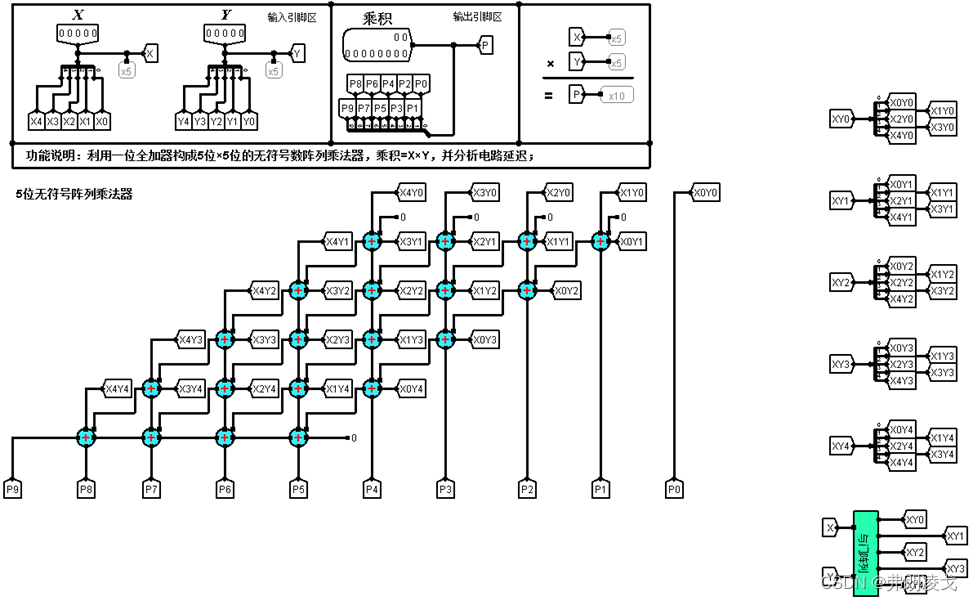

(5)阵列乘法器设计实验

①5位无符号阵列乘法器设计

用与门阵列同时产生手动乘法中的各乘积项,同时用一位全加器按照手动乘法运算的需要构成全加器阵列,实现结果如图表9所示。

|

图表 9 |

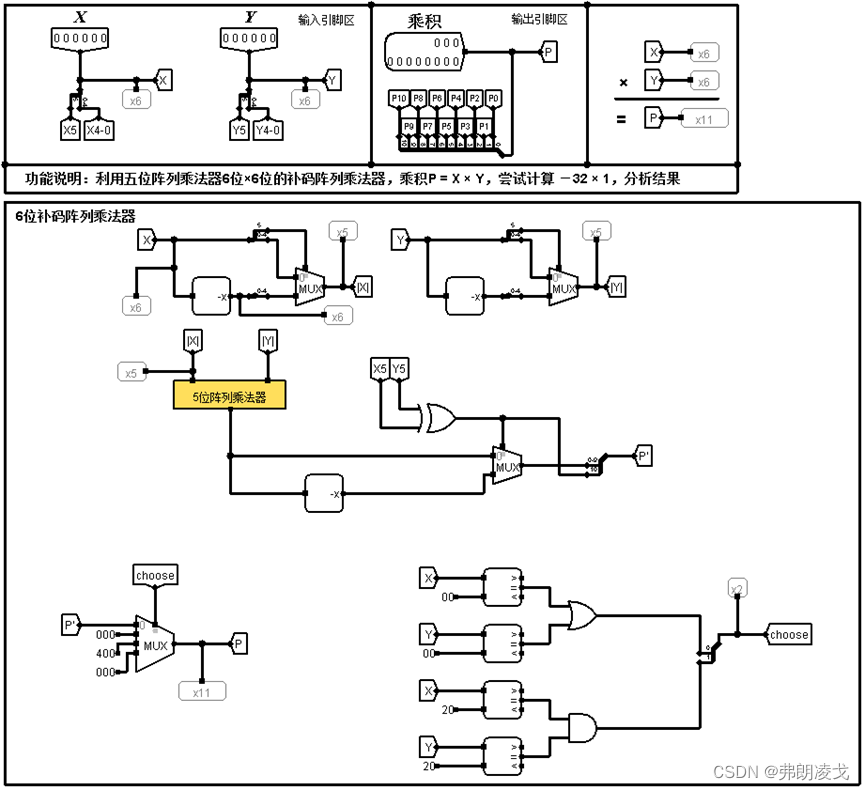

②6位补码陈列乘法器设计

由于补码乘法中的乘数、被乘数和乘积的结果都以补码的形式给出,为了能利用无符号阵列乘法器,需要在运算前将乘数和被乘数先转换成无符号数,因此在相加数电路前增加了两个n位运算前求补电路,并且分别用各自的符号位作为求补控制信号。又因为无符号阵列乘法器的输出结果是无符号数,为将结果转换为补码,需要在最后增加一个2n位运算后求补电路,同时结果的符号位由异或门产生,并作为运算后求补电路的求补控制信号。6位补码阵列乘法器的实现结果如图表10所示。

图表 10

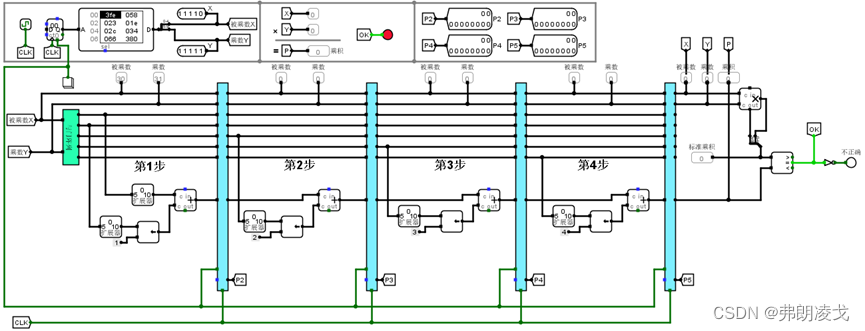

(6)乘法流水线设计实验

5位无符号乘法用横向进位阵列乘法器实现。该乘法器可看成4个5位串行加法器的级联。根据运算流水线的基本原理,可以在4个5位串行加法器之间增加流水寄存器缓存中间运算结果P1-P4。实现结果如图表11所示。

图表 11

图表 11

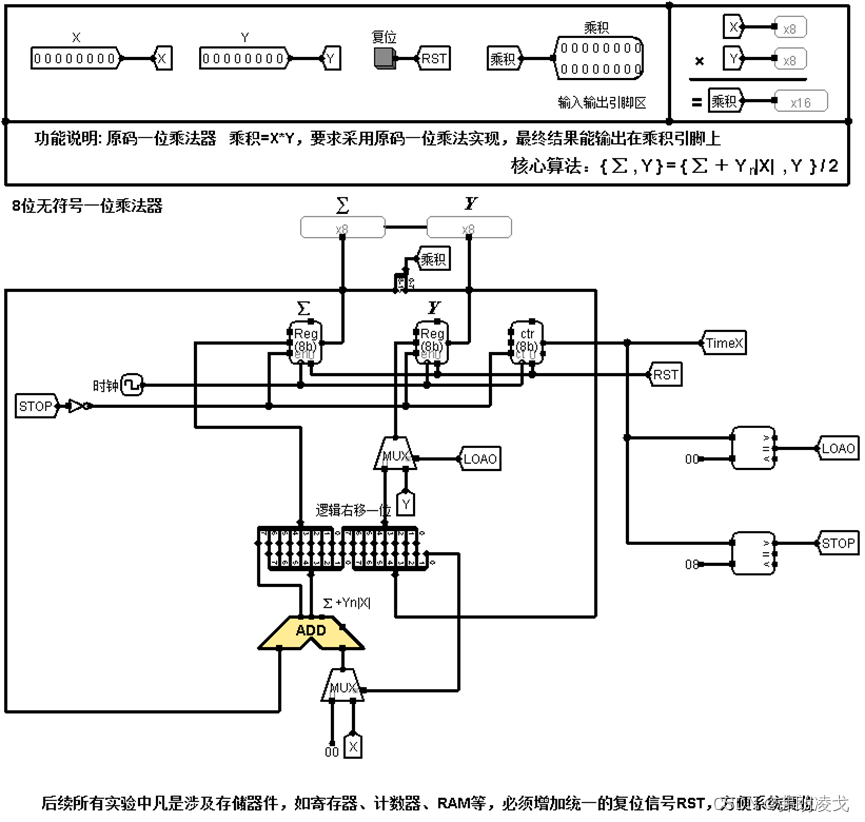

(7)原码一位乘法器设计实验

无符号原码一位乘法的计算: 维护一个部分积,初始为0,每次取乘数b的最低位,如果最低位为1,部分积=部分积+乘数a,如果最低位为0,部分积=部分积+0;然后将部分积右移一位,同时将乘数b右移一位。第i次(i<=8)对部分积的右移操作移出来的数为最终乘积的第i低位,8次结束后的部分积为最终乘积的高8位。该计算方法本质是计算乘数a与乘数b的各位相乘得到的部分积,然后将所有的部分积相加。实现结果如图表12所示。

图表 12

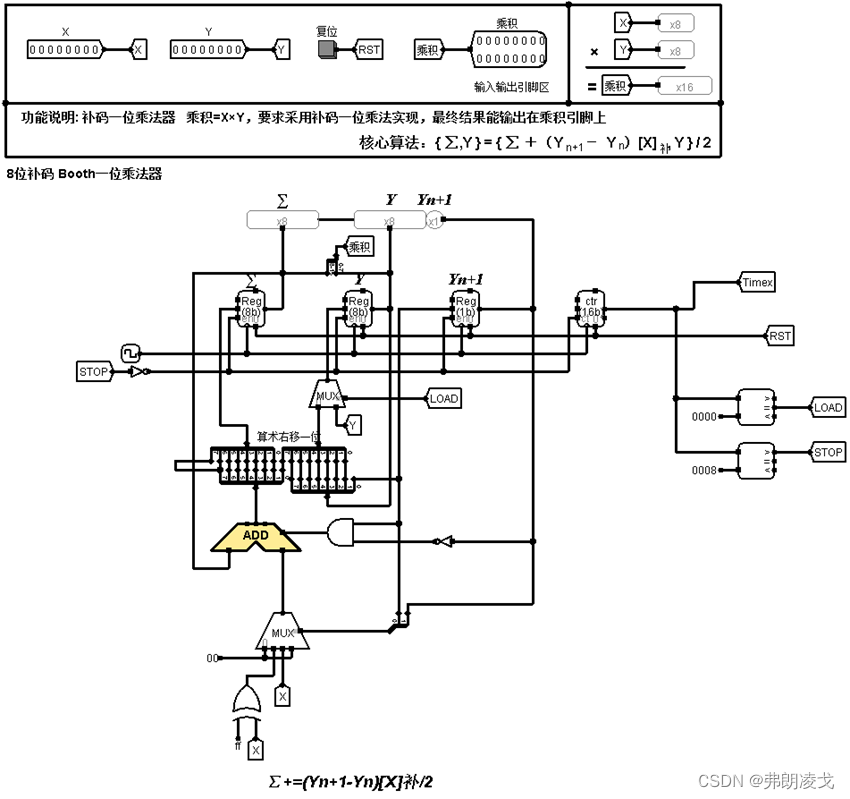

(8)补码一位乘法器设计实验

补码一位乘法器和原码一位乘法器的逻辑十分类似,计算核心逻辑为{P,y}={(P+(yn+1-yn)[x]补),y}/2。不同点如下:

①符号位参与运算

②每次对乘数寄存器中的yn、yn+1两位进行判断,并根据yn+1-yn的值决定累加值。

③控制逻辑需要控制电路进行n+1次累加与位移操作,最终结果存放在R0与R1当中,比实际多移动了一位,最终结果的最高n位存放在R0低位中,低n+1位存放在R1高位中。

补码一位乘法器的实现结果如图表13所示。

图表 13

五、遇到的问题及解决方法

1.对各实验原理不太了解。结合教材上提示的电路原理图以及网上的相关资料,最后在理解试验背后理论知识原理的基础上,完成了电路的设计工作。

2. Logisim仿真软件存在BUG。试验过程中会出现明明电路正确,出现整块报错的问题。重启软件后才恢复正常。

3.对某些元器件的功能使用不太了解。最初,我将计数器误认为是寄存器,导致原码一位乘法器始终无法正常使用,百思不得其解,在和同学讨论后,才发现元器件的错误使用,改正后电路才能够正常使用。

六、心得体会

总体来说,本次试验比上次好。但还是不知道从何处入手去解决问题,在翻阅课本和查阅大量资料后,才知道怎么去做。在后面的实验中,要提前将实验原理理解,这样做实验的时候会轻松很多。当然在试验过程中也遇到了很多的问题,或是通过查阅相关资料,或是和同学探讨,或是向老师咨询,最后都顺利解决了问题。

本文详述了多个数字电路实验,包括全加器、先行进位电路、快速加法器(4位、16位、32位)、ALU设计、阵列乘法器和乘法流水线的实现,使用Logisim软件进行仿真。实验涉及补码运算、进位逻辑及运算单元构造,通过解决软件错误和元件理解问题,加深了对数字逻辑和运算原理的理解。

本文详述了多个数字电路实验,包括全加器、先行进位电路、快速加法器(4位、16位、32位)、ALU设计、阵列乘法器和乘法流水线的实现,使用Logisim软件进行仿真。实验涉及补码运算、进位逻辑及运算单元构造,通过解决软件错误和元件理解问题,加深了对数字逻辑和运算原理的理解。

9428

9428

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?