所有资源都已打包

计算机组成原理.zip官方版下载丨最新版下载丨绿色版下载丨APP下载-123云盘

一、实验目的

(1)理解存储系统位扩展、字扩展的基本原理,能利用相关原理解决实验中汉字字库的存储扩展问题;

(2)理解主存地址进行编址基本概念和存储位扩展基本思想,并能利用相关原理构建同时支持字节、半字、字访问的存储子系统;

(3)了解MIPS寄存文件基本概念,进一步熟悉多路选择器、译码器、解复用器等Logisim组件的使用,并利用相关组件设计实现MIPS寄存器文件;

(4)掌握cache实现的3个关键技术:数据查找、地址映射、代替算法,熟练掌握译码器、多路选择器、寄存器的使用,能根据不同映射策略用数字逻辑电路实现对应的cache模块。

二、实验内容

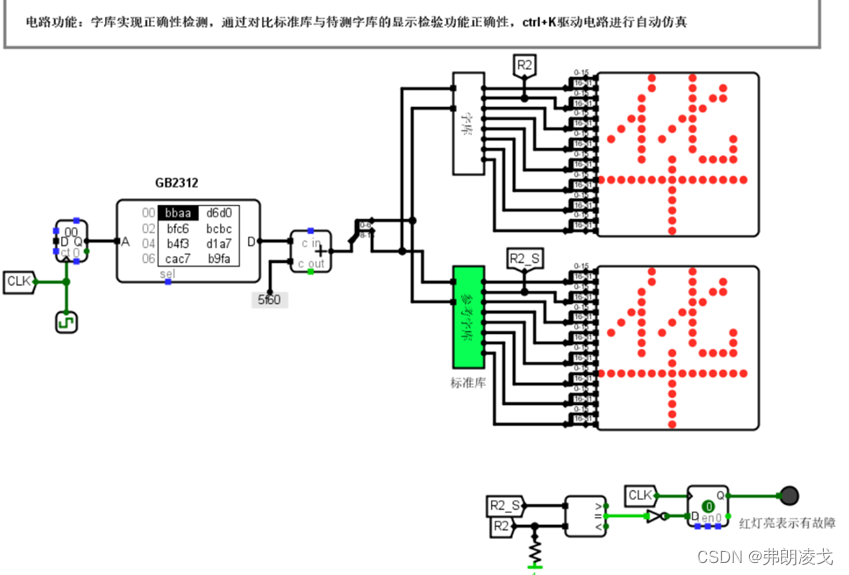

(1)字库电路实验

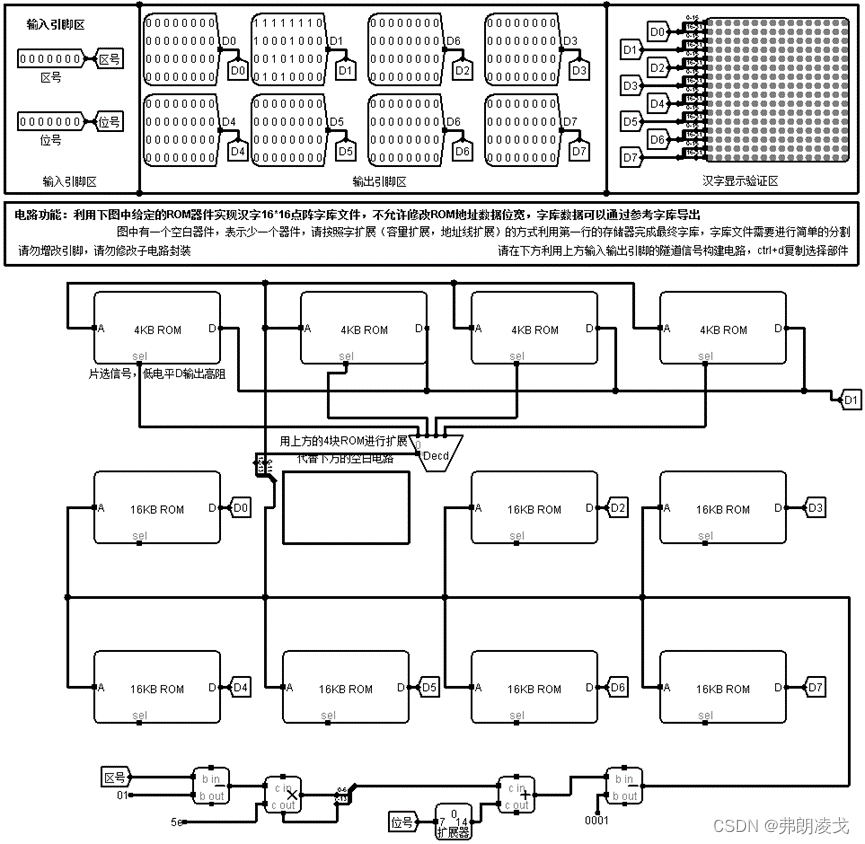

现有ROM组件,4片4K32位ROM,7片16K32位ROM,用4片4K*32位的ROM 替换其中一片16K*32位器件,即进行字扩展,需要构建GB2312汉字编码的16K*16点阵汉字字库。

实验结果如下:

实验电路如下:

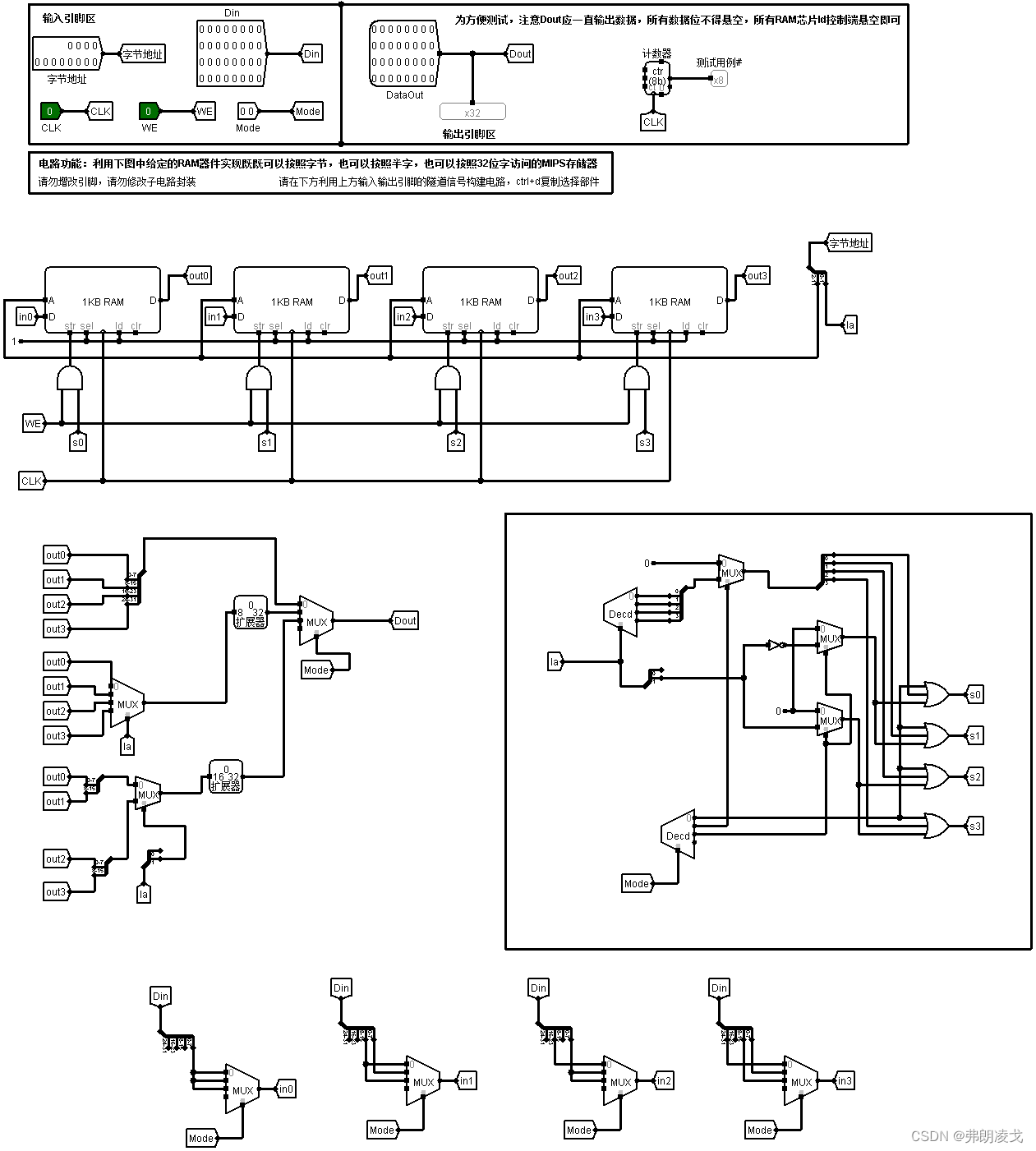

(2)MIPS RAM设计实验

主存通常按字节进行编制,主存既可以按字节访问,也可以按16位半字访问,还可以按32位的字进行访问。根据访问存储单元的大小,主存地址可以分为字节地址、半字地址和字地址。

00表示字访问,01表示1字节访问(即单字节访问),10表示2字节访问(即半字访问)。在实验中字32bit,单字节8bit,半字为16bit。地址在字访问时忽略最低两位;半字访问时忽略最低位,倒数第二位为片选;字节访问时,第二位进行片选。为了避免存储单元中的数据被覆盖,需要根据Mode和低二位决定4个存储器哪一个需要去存储。

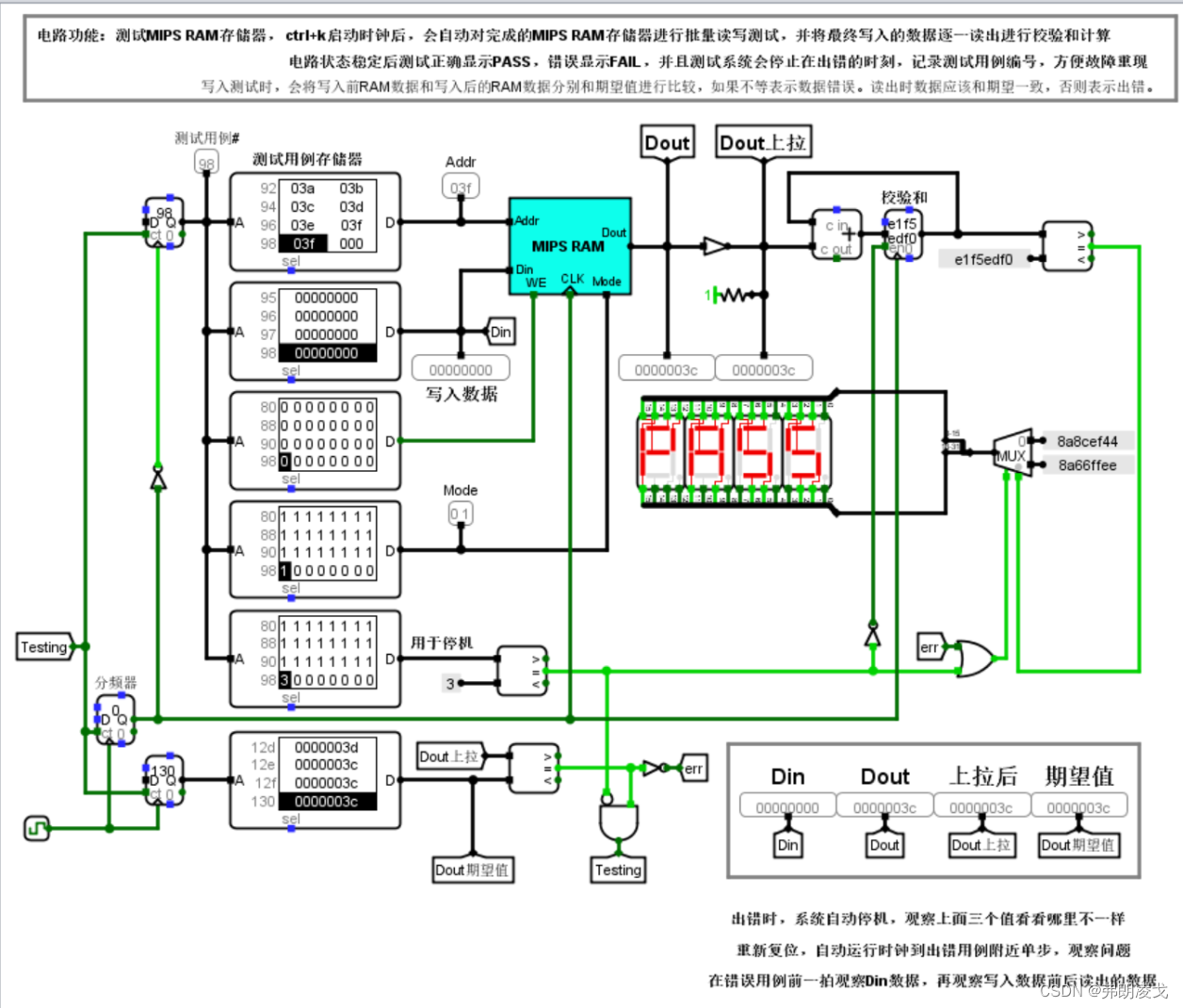

实验电路图如下:

测试效果图如下:

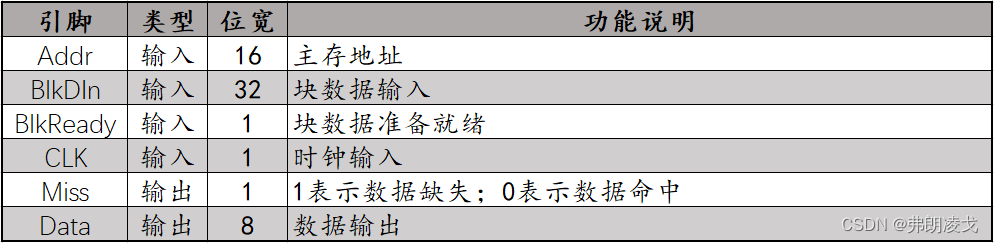

引脚的功能如下:

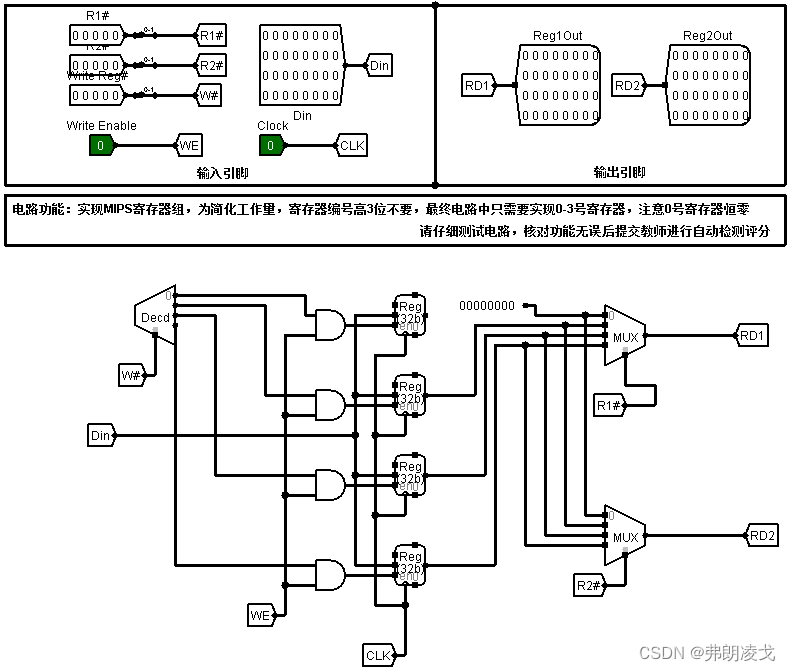

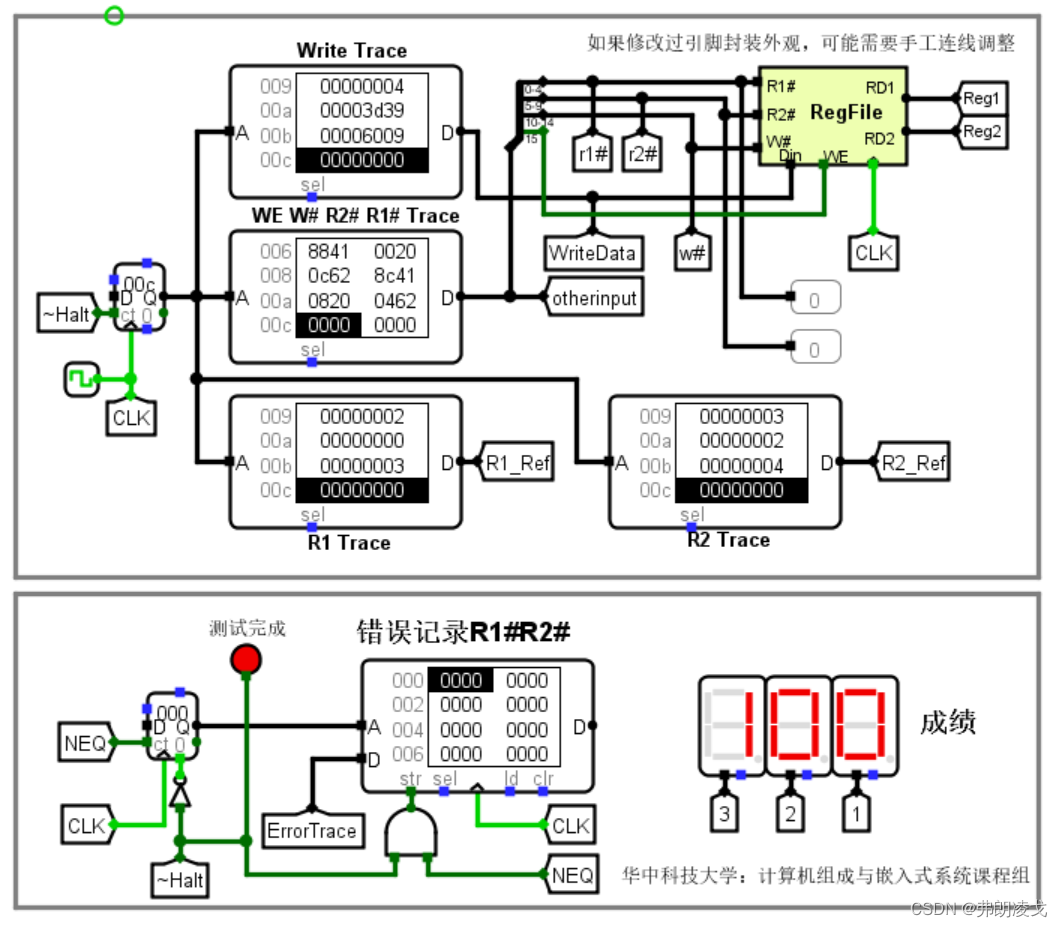

(3)MIPS寄存器文件实验

寄存器文件(寄存器堆)是CPU中通用寄存器的集合。以MIPS寄存器文件为例,MIPS指令支持32个通用寄存器,32个通用寄存器均包含在寄存器文件中,其中每个寄存器的内容可以通过对应寄存器编号进行访问,类似于一个具有多地址端口和多个数据端口的高速存储器。利用多路选择器、译码器等组件设计实现一个MIPS寄存器文件,内容包含32个32位寄存器。

实现电路如下:

电路测试结果如下:

|

具体引脚与功能如下:

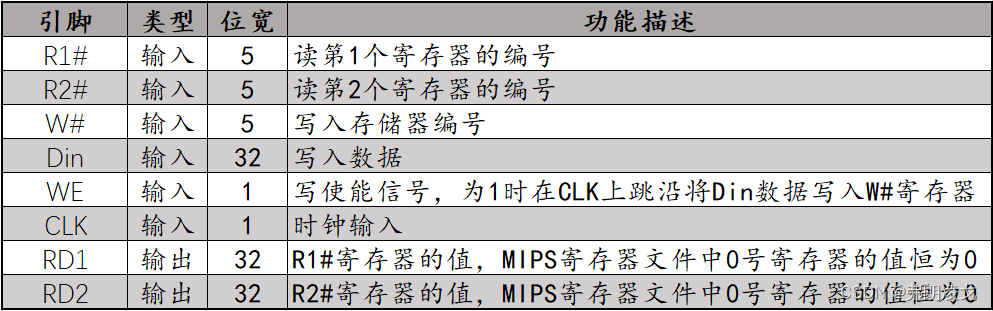

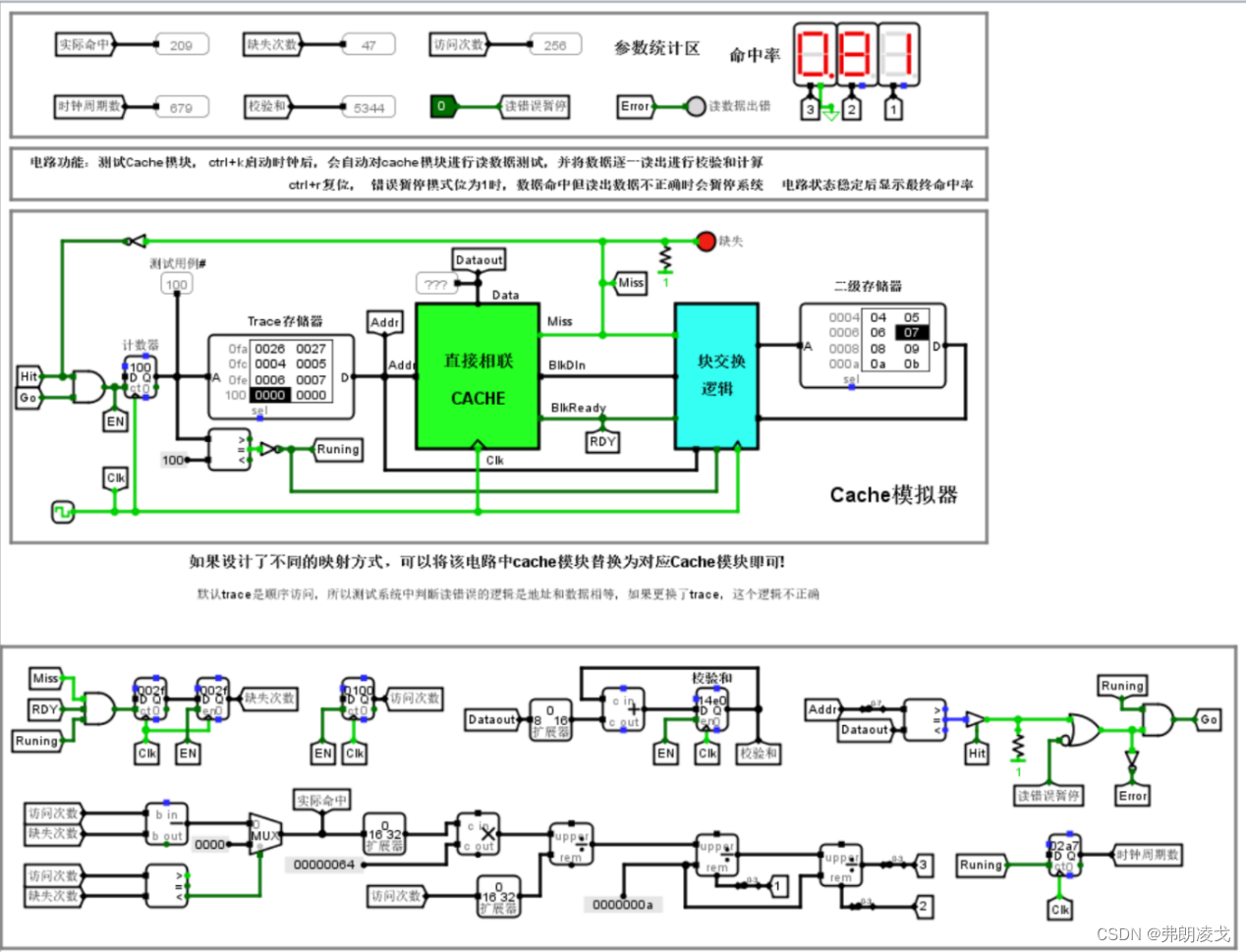

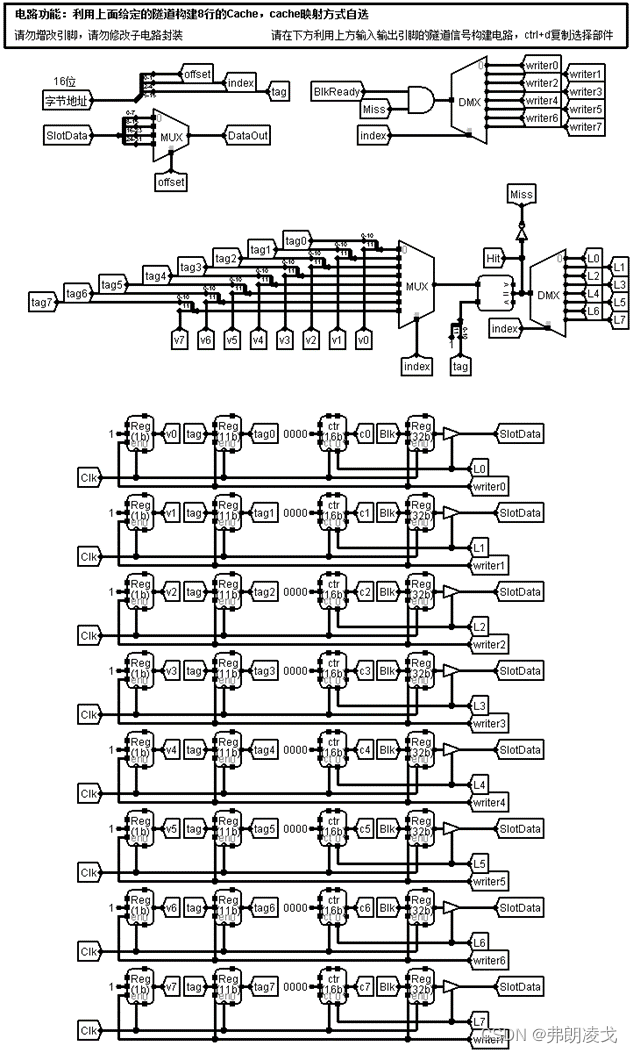

(4)Cache硬件设计实验

本试验采用直接相联映射。

假设cache块大小为4W,共8行,字节地址为16位,分为tag、index、offset三个部分,因为块大小为4W,故offset为2位;cache共8行,故index为3为;tag则为11位。行索引index字段部分经过行索引译码器生成若干行索引译码信号,由行索引译码信号选择对应的cache行,控制对应行的有效位valid、标记位tag、数据块输出,所有行数据输出均采用三态门控制输出至系统数据总线。行译码信号L0-L7连接至对应的三态门控制端,只有行译码信号有效的行才会进行输出,同一时刻只有一行输出。当选中行有效位为1且标记位与字节地址中的tag相同时,数据命中。命中信号hit控制最终的字选择多路选择器的使能端,决定具体输出选中行中哪一个字,从而实现数据的查找和访问。

数据未命中时,Miss信号为1,当Miss信号和BlkReady信号同时为1时,结合行索引译码信号,对cache中相应行的valid信号、tag、data进行修改,然后取出正确数据。

实验效果如下:

|

引脚功能如下:

实现电路如下:

实现电路如下:

三、实验工具

Logisim仿真实验软件

四、遇到的问题及解决方法

1.在连接完字库电路后,字库测试时发现结果有一定偏差,经过与同学讨论得知,是未将参考字库存储器中的数据转移至设计电路寄存器中的原因,在将参考字库存储器中的数据复制至设计电路存储器中的过程也遇到了难题,不知道如何正确对应数据,在进一步查询资料学习后,问题才得以解决。

2.对各实验原理欠缺全面了解。在实验设计之前,我重新学习了相关实验的理论知识,搞清楚各实验背后的原理,然后才尝试进行试验的设计。结合教材上提示的电路原理图以及网上的相关资料,最后在理解实验背后理论知识原理的基础上,完成了电路的设计工作。

3.对于一些元器件的作用不太清楚。由于暂时还没有学习数电,对一些元器件的功能没有清楚的认识,很多时候无法正确地选择元器件。在查阅大量资料后才解决此问题。

五、心得体会

总体来说,本次试验比上次好。但还是不知道从何处入手去解决问题,在翻阅课本和查阅大量资料后,才知道怎么去做。在后面的实验中,要提前将实验原理理解,这样做实验的时候会轻松很多。当然在试验过程中也遇到了很多的问题,或是通过查阅相关资料,或是和同学探讨,或是向老师咨询,最后都顺利解决了问题。

该实验涉及存储系统的基本原理,包括位扩展和字扩展,通过Logisim设计了汉字字库、MIPSRAM、寄存器文件和Cache。在实践中,遇到数据转移、元器件理解等问题,通过学习和讨论得以解决。实验强调了理论知识的重要性,并提升了问题解决能力。

该实验涉及存储系统的基本原理,包括位扩展和字扩展,通过Logisim设计了汉字字库、MIPSRAM、寄存器文件和Cache。在实践中,遇到数据转移、元器件理解等问题,通过学习和讨论得以解决。实验强调了理论知识的重要性,并提升了问题解决能力。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?