一、实验平台

芯片介绍:

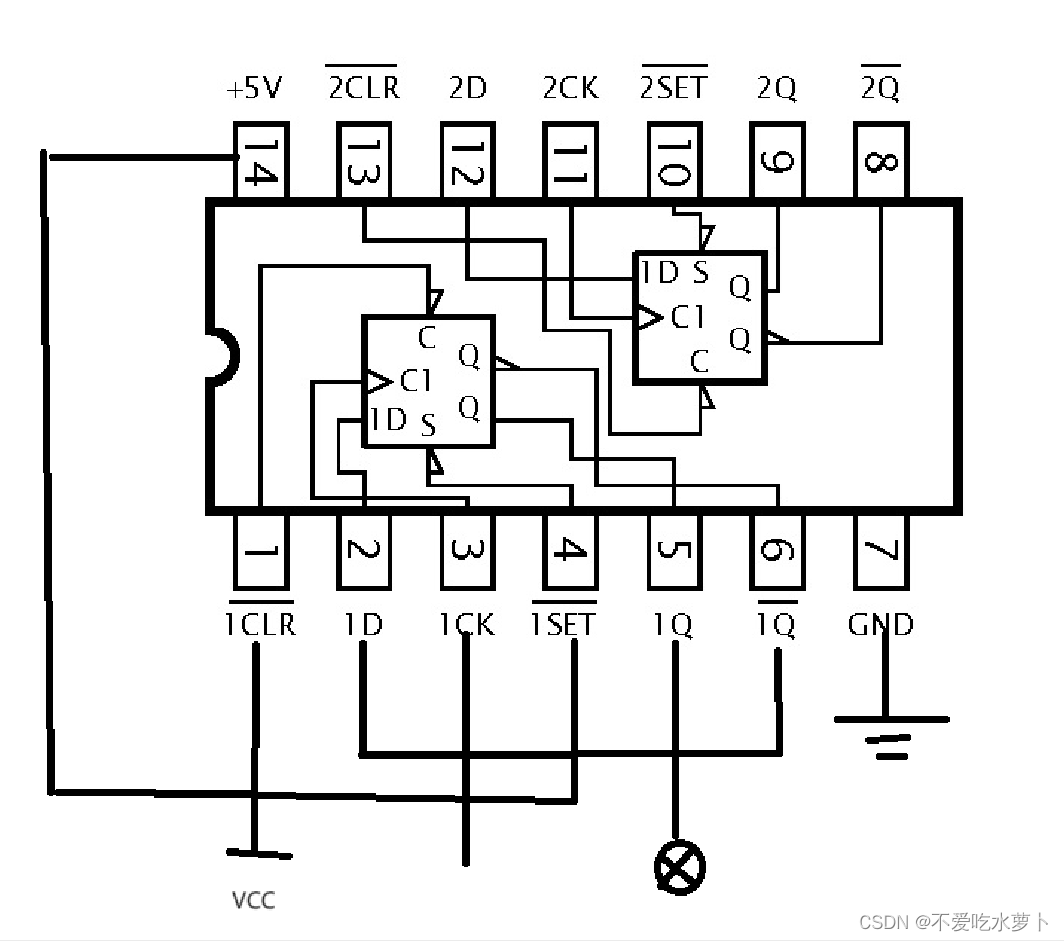

7474芯片内部包含有两个独立的D型触发器,每个触发器都有独立的数据(D)、时钟(CLK)、复位(CLR或.RST)和置位(PRE或.SET)输入端口,以及对应的输出(Q和Q')端口。在时钟信号的上升沿(或某些版本在下降沿)时,触发器会根据数据输入D的值更新输出状态,而复位和置位端口则分别用于强制触发器输出清零或置1。

二、实验原理

简单画了个电路连接图,我们先实现1CK输入1HZ的时钟,1Q的指示灯LED1HZ翻转一次,即为一个周期为2S,0.5HZ,实现二分频:

- 芯片供电(VCC,GND)

- 1D接1Q反,原因:在时钟的上升沿,1D的值会赋给1Q,而1D和1Q反相接,可以实现状态翻转

- 置位端和清零端不使用,接高电平禁用

我们通过上述要点即可实现利用7474芯片制作一个二分频计数器。

本文介绍了如何使用7474芯片构建二分频计数器,以及如何通过接线和逻辑设计实现四进制、三进制加法和减法计数器,以及扩展到八进制计数器的应用。此外,还提及了数电实验中的其他应用,如四舍五入和三人表决电路。

本文介绍了如何使用7474芯片构建二分频计数器,以及如何通过接线和逻辑设计实现四进制、三进制加法和减法计数器,以及扩展到八进制计数器的应用。此外,还提及了数电实验中的其他应用,如四舍五入和三人表决电路。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?