13.采用8体并行低位交叉存储器,设每个体的存储容量为32K*16位,按16位字编址存储周期为400ns,下述说法正确的是()

A.在400ns内,存储器可向CPU提供128位二进制信息

B.在100ns内,每个体可向CPU提供128位二进制信息

C.在400ns内,存储器可向CPU提供256位二进制信息

D.在100ns内,每个体可向CPU提供256位二进制信息

A

400ns=0.4微秒

16位*8=128位=2^7位

有个问题,并行,多体,低位都是啥🤔

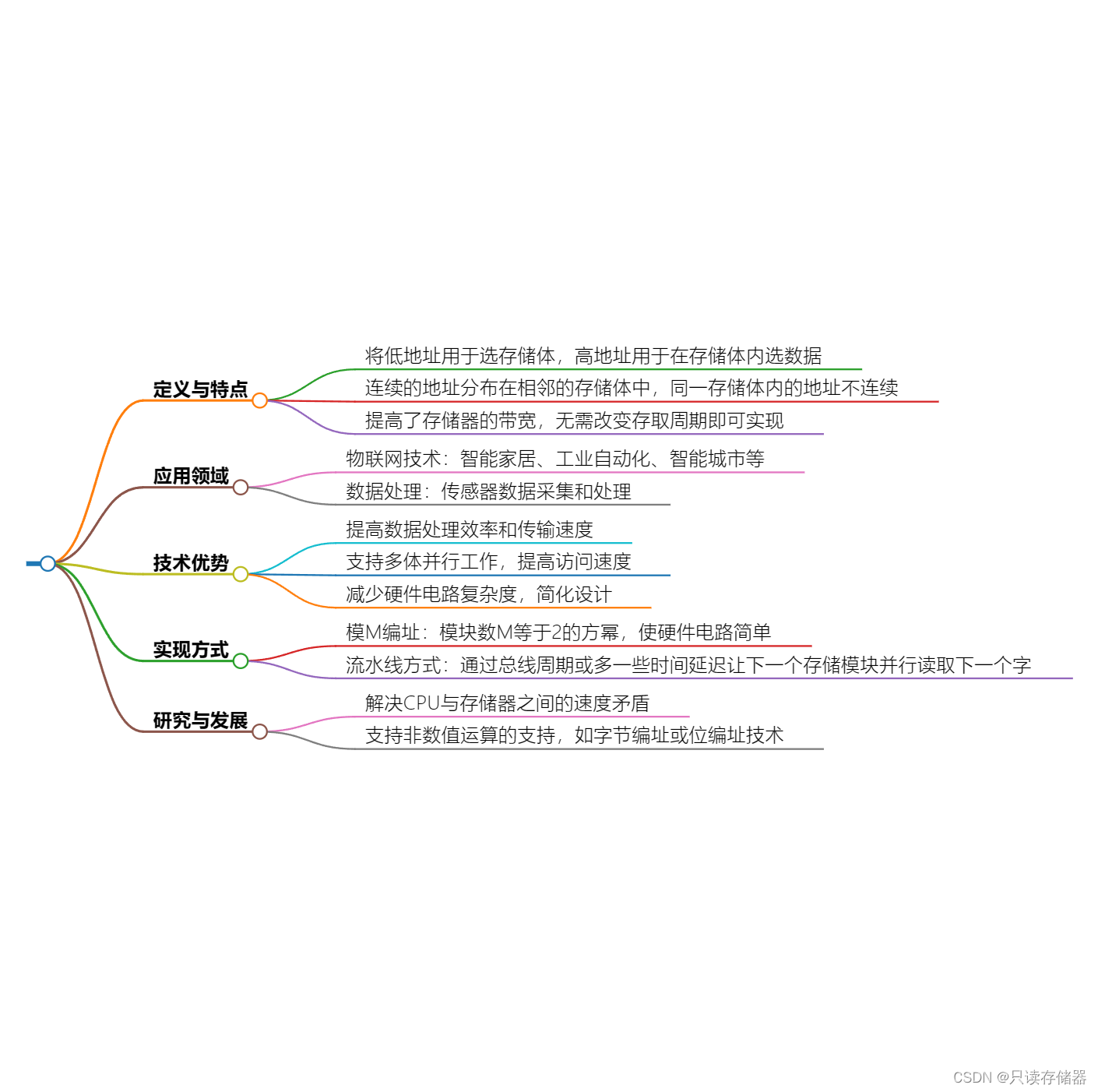

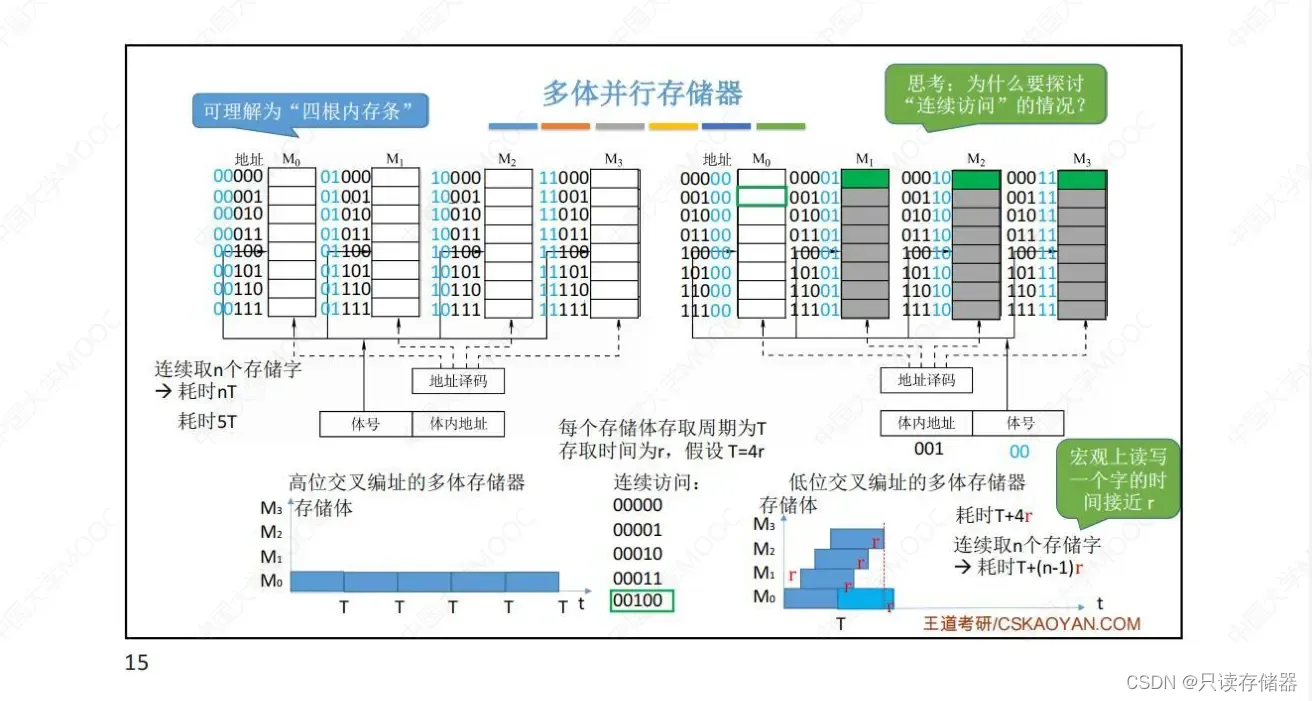

多体并行存储器由多体模块组成。每个模块都有相同的容量和存取速度,各模块都有独立的读写控制电路,地址寄存器和数据寄存器。它们既能并行工作,又能交叉工作。

其目的是为了解决一个存取周期中恢复时间较长问题,多体并行存储器分为高位交叉编址和低位交叉编址两种。

低位交叉编址

下面来张图,来自秘塔AI👍

来自王道

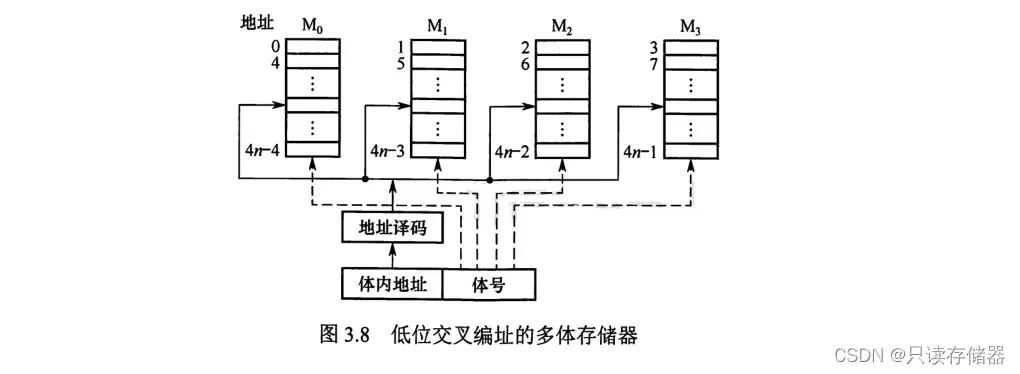

低位交叉编址的低位地址表示体号,高位表示体内地址,每个模块按‘模M’交叉编址,模块号=单元地址%M

- 低位地址表示体号,高位地址表示体内地址(这种编址方法又称模 M 编址,M 等于模块数)

- 相邻地址位于不同存储体中,每个存储体都需要寄存器

- 多模块并行,可以实现对存储器的流水线式访问,性能提升

14.某总线共有88根信号线,其中数据总线为32根,地址总线为20根,控制总线为36根,总线工作频率为66Hz,则总线宽度和传输速率分别为

A.32位 264MB/s

B.20位 254MB/s

C.20位 264MB/s

D.32位 254MB/s

A

好,来再看一遍知识点😁

数据总线:传送数据信息,CPU一次传输的数据与数据总线带宽相等。

控制总线:传送控制信号和时序信号,如读/写,片选,中断响应信号等。

地址总线:传送地址,它决定了系统的寻址空间。

总线的位宽(宽度):即总线能同时传输的数据位数,有32位,64位等。所以由数据总线可以知道

总线带宽可理解为总线的最大数据传输率,即单位时间内总线上最多可传输数据的位数,通常用每秒传送信息的字节数来衡量,单位可用字节/秒(B/s)来表示。

总线带宽 = 总线工作频率 * (总线宽度/8)

地址总线的宽度越小,则地址数量越少,允许直接访问主存储器的空间越小。

15.某计算机使用4体低位交叉编址存储器,假定在存储器产品线上出现的主存地址(十进制)序列为8005,8006,8007,8008,8001,8002,8004,8000,则可能发生访存冲突的地址对是()

A.8004和8008

B.8002和8007

C.8001和8008

D.8000和8004

D

8005 % 4 = 2001...1所以8005的模块序号为1

模块序号 = 访存地址 % 存储器交叉模块数

16.关于Cache的3种基本映射方式,下面叙述中错误的是()

A.Cache的地址映射有全相联,直接和多路相联3种基本映射方式

B.全相联映射方式,即主存单元与Cache单元随意对应,线路过于复杂,成本太高

C.多路组相联映射是全相联映射和直接映射的一种折中方案,有利于提高命中率

D. 直接映射是全相联映射和组相联映射的一种折中方案,有利于提高命中率

D

cache行中的信息是主存中某个块的副本,地址映射是指把主存地址空间映射到cache地址空间,即把存放在主存中的信息按照某种规则装入cache。

由于cache行数比主存块数少得多,因此主存中只有一部分块的信息可存放在cache中,因此在cache中要为每块加一个标记,指明它是主存中哪一块的副本,该标记的内容相当于主存中块的编号。为了说明cache行中的信息是否有效,每个cache行需要一个有效位。

D错在折中,组相联才是,书P119

17.主存按字节编址,地址为0A4000H到0CBFFFH,共()字节,若用存储容量为32K*8位的存储芯片构成该主存,至少需要()片

A.80K,2

B.96K,2

C.160K,5

D.192K,5

C

按字节计算:存储容量=存储单元个数 * 存储字长/8

存储单元个数 = 末地址-首地址 + 1,题目求得后16进制转换为10进制可得163839

所需芯片数 = 存储空间 / 存储容量(160K*8)/(32K*8)

18.存储器采用部分译码法片选时,()

A.不需要地址译码器

B.不能充分利用存储空间

C.会产生地址重叠

D.CPU的地址线全参与译码

C

采用部分译码法时,由于未参加译码的高位地址与存储器地址无关,因此存在地址重叠问题

地址重叠:一个存储单元有多个地址与其对应的现象

CPU对存储器进行读写时,首先要对存储芯片进行选择(称为片选),然后从被选中的存储芯片中选中所要读写的存储单元。

片选是通过地址译码来实现的。排除A👊

19.某容量为256MB的存储器由若干4M*8位的DRAM芯片构成,该DRAM芯片的地址引脚和数据引脚总数是()

A.19

B.22

C.30

D.36

A

地址引脚 = 地址线的个数,地址线的个数看MAR的位数,MAR的位数反映了存储单元的个数

数据引脚 = 数据线的个数,数据线的个数看MDR的位数,MDR的位数反映了存储单元的字长

https://blog.csdn.net/weixin_44001521/article/details/103548736

20.某存储器容量为64KB,按字节编址,地址4000H~5FFFH为ROM区,其余为RAM区。若采用8K*4位的SRAM芯片进行设计,则需要该芯片数量是()

A.7

B.8

C.14

D.16

C

所需芯片数 = 存储空间 / 存储容量

ROM的末地址-首地址可以得到ROM的地址为2000H经转换得到2^13B = 8KB

因为1K = 2^10B

RAM = 64KB - 8KB = 56KB

https://blog.csdn.net/qq_34438969/article/details/120789680

21.某计算机主存按字节编址,由4个64M*8位的DRAM芯片采用交叉编址方式构成,并与宽度为32位的存储器总线相连,主存每次最多读写32位数据。若double型变量x的主存地址为804001H,则读取x需要的存储周期数是()

A.1

B.2

C.3

D.4

C

https://blog.csdn.net/Sherrian_/article/details/126988158

感觉这个也能理解一点,先把x的主存地址转换为二进制,然后四个芯片,最低两位拿出来做体号

22.有一个容量为128KB的SRAM存储器芯片上,按字长32位编址,其地址范围可从0000H到()

A.3FFFH

D.7FFFH

C.7FFFFH

D.3FFFFH

B

https://blog.csdn.net/Mancuojie/article/details/120683597

字节进制的单位换算

23.地址线A15~A0(低),若选取用16K*1位存储芯片构成64KB存储器,则应由地址码()译码产生片选信号

A. A15,A14

B. A0,A1

C. A14,A13

D. A1,A2

A

没搞明白😐

24.一个存储器系统中,常常同时包含ROM和RAM两种类型的存储器,如果用lK×8位的ROM芯片和lK×4位的RAM芯片,组成4K×8位的ROM和1K×8位的RAM存储系统,按先ROM后RAM进行编址。采用3-8译码器选片,译码信号输出信号为Y0~Y7,其中Y4选择的是( )。

A.第1片ROM

B.第5片ROM

C.第1片RAM

D.第1片RAM和第2片RAM

D

25.若数据在存储器中采用低字节地址为字地址的存放方式(小端存储),则16进制数12345678H按自己地址由小到大依次存为()

A.12345678

B.87654321

C.78563412

D.34127856

C

2个16进制数位对应8个二进制数位,即1个字节

字:一组或者一串bit

字长:字的位数叫做字长

字节:8个二进制位为一个字节

26.容量为64块的cache采用组相联映射方式,子块大小为128个字,每4块为1组。如果主存为4K块,且按字编址,那么主存地址和主存标记的位数分别为()位

A.16,6

B.17,6

C.18,8

D.19,8

D

27. Cache用组相联映射,一块大小为128B,Cache共64块,4块分一组,主存有4096块,主存地址共需()位。

A.19

B.18

C.17

D.16

A

28.假定主存地址为32位,按字节编址,主存和cache之间采用直接映射方式,主存块大小为4个字,每字32位,采用写回(Write Back)方式,则能存放4K字数据的cache的总容量的位数至少是( )。

A.146K

B.147K

C.148K

D.158K

C

29.在全相联映射,直接映射和组相联映射中,块冲突概念最小的是()

A.全相联映射

B.直接映射

C.组相联映射

D. 不一定

A

30.关于LRU算法,以下说法正确的是()

A.LRU算法替换掉那些在Cache中驻留时间最长且未被引用的块

B.LRU算法替换掉那些在Cache中驻留时间最短且未被引用的块

C.LRU算法替换掉那些在Cache中驻留时间最长且仍在引用的块

D.LRU算法替换掉那些在Cache中驻留时间最短且仍在引用的块

A

LRU(Least Recently Used)最近最少使用页面置换算法

31.下列关于虚拟存储器的说法,错误的是()

A.虚拟存储器利用了局部性原理

B.页式虚拟存储器的页面如果太小,主存中存放的页面数产多,导致缺页频率较低,换页次数减少,可以提升操作速度

C.页式虚拟存储器的页面如果较大,主存中存放的页面数产少,导致页面调度频率较高,换页次数增加,降低操作速度

D.段式虚拟存储器中,段具有逻辑独立性,易于实现程序的编译,管理和保护,也便于多道程序共享

B

以页为基本单位的虚拟存储器称为页式虚拟存储器

虚拟空间与主存空间都被划分成同样大小的页,主存的页称为实页,虚存的页称为虚页

32.访问相联存储器时,()

A.根据内容,不需要地址

B.不根据内容,只需要地址

C.既要内容,又要地址

D.不要内容也不要地址

C

33.对36位虚拟地址的页式虚拟存储系统,每页8KB,每个页表项为32位,页表的总容量为()

A.1MB

B.4MB

C.8MB

D.32MB

D

https://blog.csdn.net/qq_45735810/article/details/107135355

✌终于over,有错请指出,谢谢你的观看👋

1386

1386

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?