PHY芯片详解(型号:88E1145)

一 概述

1.1 PHY基本作用

(1) 接收MAC过来的数据进行处理,并行数据转串行,按照物理层编码方式进行编码,再变为模拟信号发送出去。

(2) 实现CSMA/CD(多点接入载波监听/冲突检测),检测网络上是否有数据在传输,如果有则等待,一旦检测到网络空闲,则发送下一个数据。冲突检测可以检测到数据冲突,然后各自等待一个随机的时间重新发送数据。

1.2 特性

① 四端口设备,定义为port0-port3,每个port对应一个net设备,且每个port支持10/100/1000传输速率。

② 对于port0的信号描述,例如pin 1,采用格式P0_CONFIG1。

③ PHY芯片型号是88E1145(引脚数:364-pin)。

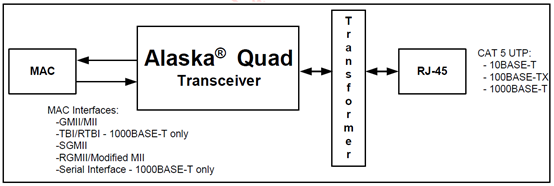

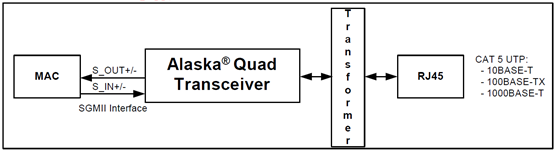

1.3 功能模块框图

二 设备接口描述

2.1媒体相关接口

2.2.1 铜接口:包含引脚P[3:0]_MDI[3:0]+、P[3:0]_MDI[3:0]-连接到外部RJ45,通过RJ45连接网线。

2.2.2光纤接口:光纤连接到光纤收发器,光纤收发器通过串行接口连接到PHY芯片,PHY芯片再通过GMII或者RGMII连接到MAC。包含引脚有S_IN+,S_IN-,S_OUT+,S_OUT-, SD+, SD-。

2.2 MAC接口

MAC接口支持GMII/MII,RGMII,SGMII和串行连接。这些接口连接到10/100/1000 Mbps MAC。

重点讲解RGMII和SGMII。

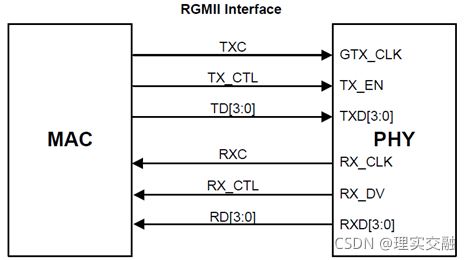

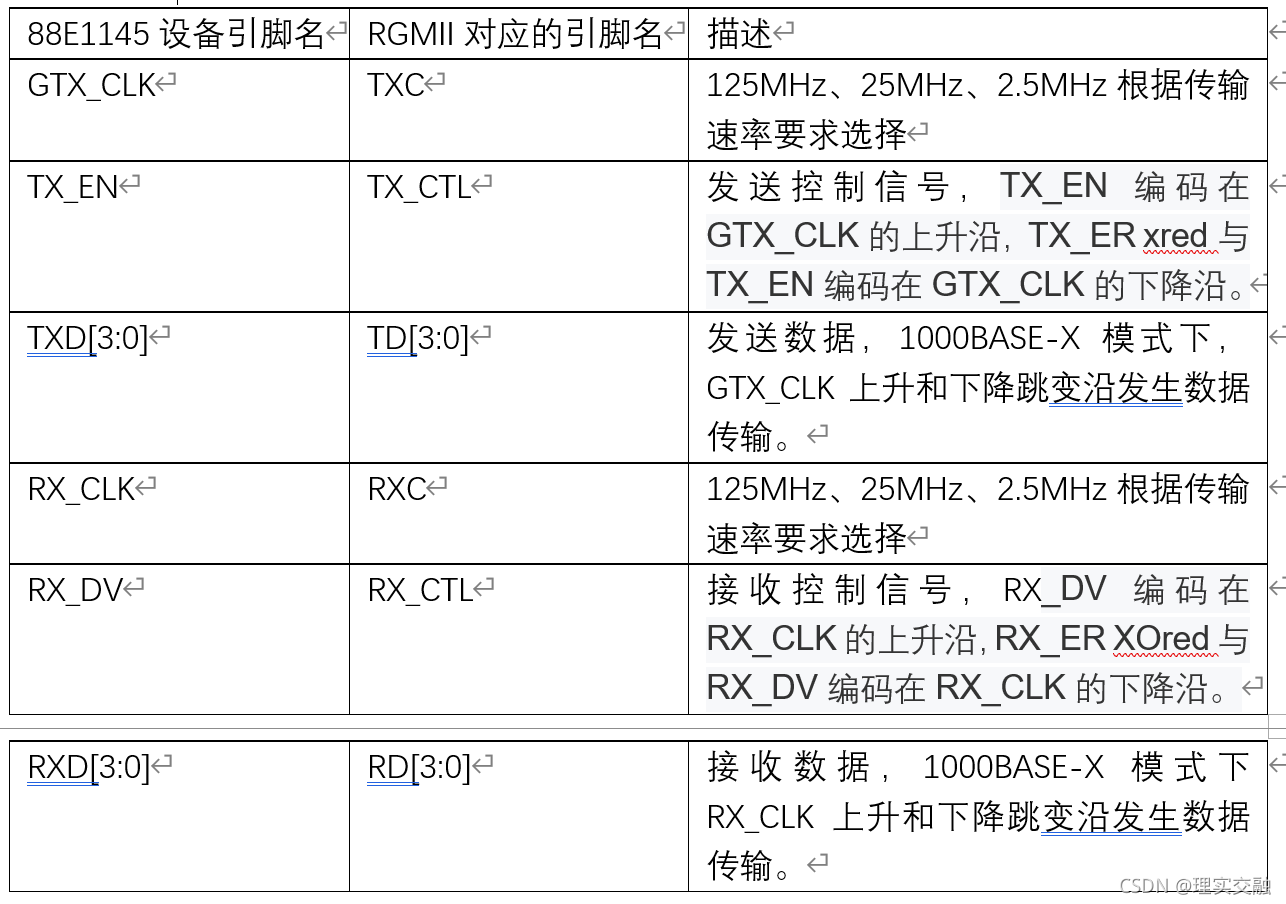

2.2.1 RGMII

通过12根线实现,将MAC层和PHY芯片连接,用于传输数据;对于GMII接口,数据和控制信号相对减少,并且一些控制信号被复用。

硬件连接方式:

引脚描述:

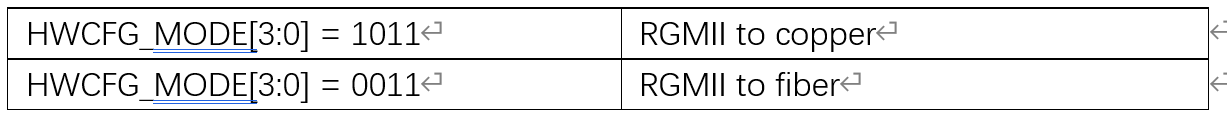

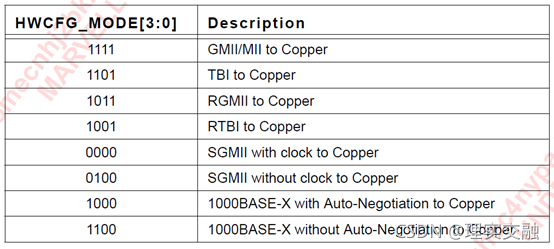

RGMII通过两种形式与外部进行数据传输,一种是转铜线,接RJ45,一种是转光纤,接光纤转接器。这里通过设置HWCFG_MODE[3:0]实现,

在包接收过程中,在高电平和低电平期间RX_CLK可以被拉伸,以适应自由时钟到数据同步时钟的过度,在PHY数据传输速度发生改变时,也可以在时钟正脉冲和负脉冲期间进行同样的拉伸,但是在整个速度转换过程中,时钟不能有任何的差错。

MAC必须确保TX_EN(TX_CTL)低,直到TX_EN(TX_CTL)确保MAC和PHY工作速度一样。

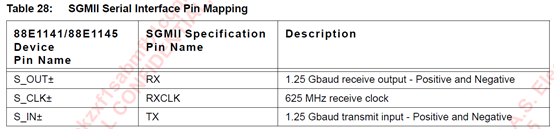

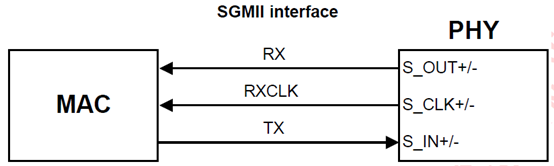

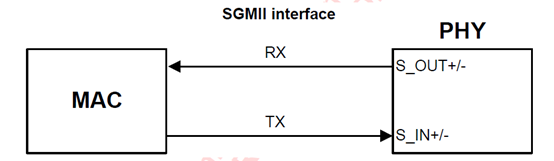

2.2.2 SGMII

在发送端,不需要TXCLK时钟输入,直接从输入数据中恢复时钟,有效减少引脚数。

在接收端,有两种操作模式,一种是提供接收时钟给MAC,一种不需要,实质就是看MAC在接收端有没有时钟恢复能力。串行接口(无时钟恢复能力)时钟选择通过设置HWCFG_MODE[3:0]=0000实现;串行接口不选择时钟(有时钟恢复能力)设置HWCFG_MODE[3:0]=0100实现。

接收端设置为无时钟模式连线方式:

接收端设置为有时钟模式连线方式:

当有时钟恢复能力的时候,可以禁用引脚S_CLK,为MAC省电。

三 功能描述

3.1 数据速率配置

通过配置HWCFG_MODE[3:0]的值实现

3.2 MAC接口转铜线配置

工作在SGMII模式下,连接、双工和速度是通过自协商的形式表明。

MAC与铜线的连接示意图:

工作在SGMII接口下与MAC的连接示意图:

3.3 RGMII 转 SGMII配置

在自协商开启的时候,速率、双工和连接都会自动协商,通过PHY决定在以上参数下工作;在自协商关闭的状态下,速率和双工通过寄存器20.5:4决定速率和寄存器0_1_8决定双工模式,当接收到有效空闲时决定连接状态。

发送和接收FIFOs在RGMII模式下被使能,S_CLK默认被使能。

3.4 模式切换

操作模式可以在上电后通过写寄存器27.3:0改变,所有模式的改变必须在软件复位后进行,软件复位完成后在新模式下操作,对于某些模式更改不能自动完成,还有一些额外的寄存器要更改。

3.5 硬件配置

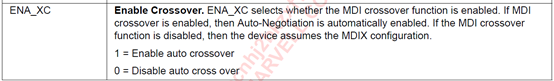

配置选项如PHY地址、工作模式、自动协商、MDI交叉和物理连接类型,通过使用配置引脚实现。

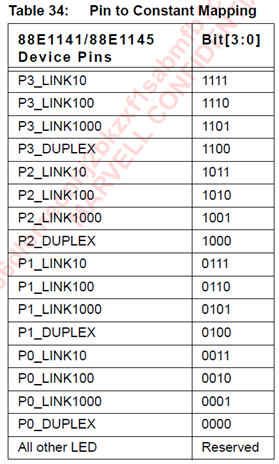

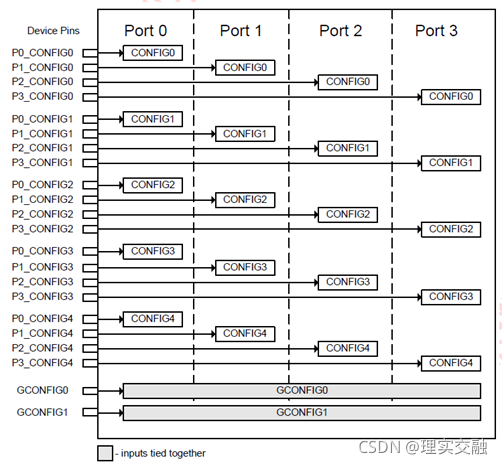

CONFIG[4:0]pin被连接到一些引脚,配置各种选项期望的选择,具体参考以下引脚连接映射值的表格。

CONFIG[4:0]配置port对应的示意图:

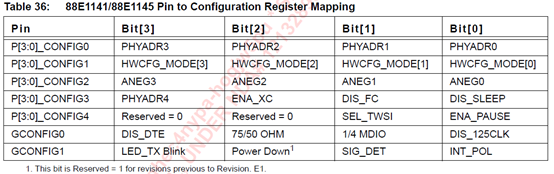

所有配置的对应关系:

这里重点讲解PHY地址和HWCFG_MODE。

由上图可知,PHY地址是5bit,低4Bit由CONFIG0决定,查看硬件原理图连接到哪个pin,对照《pin to constant mapping》表查看对应的bit[3:0]的值即为PHY地址的低4位。Bit5位由CONFIG3的最高位决定,获取方法同上。

例如:P0_CONFIG0引脚连接至P0_DUPLEX引脚,那么按照《pin to constant mapping》对照表可知,PHY_ADDR[3:0] = 0000,再查看P0_CONFIG3引脚连接至P3_LINK10,查表知此时P0_CONFIG3的bit3为1,表示PHY_ADDR的第五位PHY_ADDR[5],连接PHY_ADDR[3:0]和PHY_ADDR[5]得到PHY_ADDR = 10000(二进制) = 16(十进制)。

CONFIG2配置HWCFG_MODE[3:0]直接影响PHY芯片很多方面的工作模式。具体表现为:

其他需要重点关注的寄存器配置如下:

关于table36中所有配置寄存器的定义不再一一描述,详见数据手册Page(89)开始均有介绍。

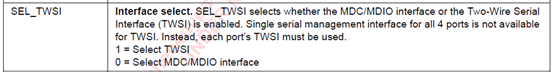

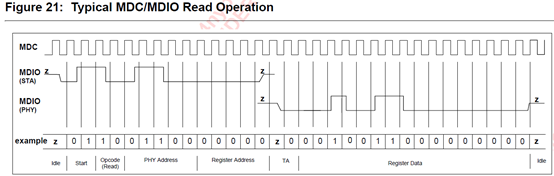

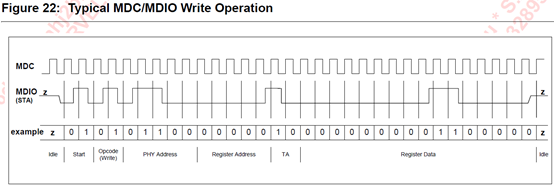

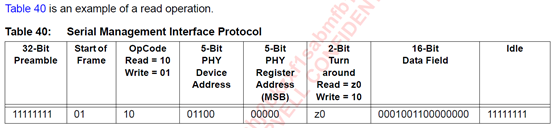

3.6 管理接口MDC/MDIO

MDC/MDIO接口类似于IIC接口,MDC为时钟线,时钟最大不超过8.3MHz,MDIO是数据线,进行地址和数据的传输。

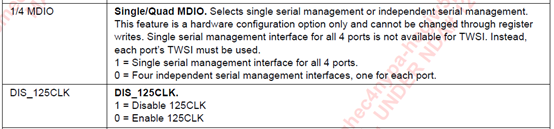

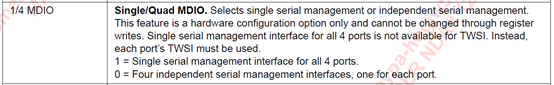

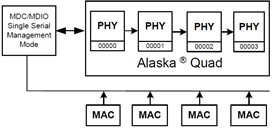

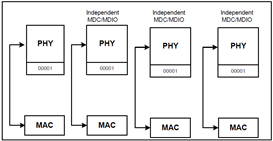

在4个port口使用MDC/MDIO管理接口时候,可以采用两种方案设计,第一种是一个单一的串行管理接口支持四个port。另一种是4个独立的串行接口分别管理每个port。连接示意图如下所示:

当选择4个独立的串行接口分别管理每个port的时候,必须配置1/4 MDIO寄存器,关于这个寄存器的配置在3.5节硬件配置里面有讲解。

关于MDC/MDIO的读写时序如下所示:

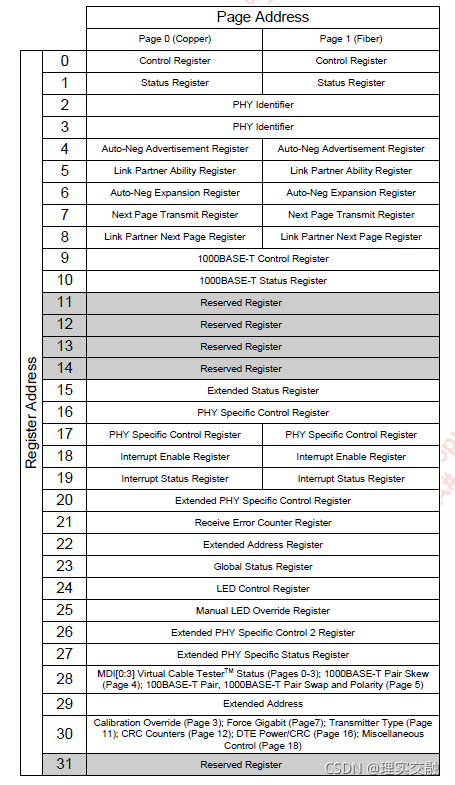

MDC/MDIO协议仅支持32个寄存器,然而88E1145有32个以上的寄存器,因此采用分页机制管理进行寻址。具体参考后续寄存器描述。

MDC/MDIO也有中断功能,这里不做详细介绍。

3.7 自协商

支持5种类型的自动协商。

自动协商在以下任意一种情况下发起:

① 上电复位

② 硬件复位

③ 软件复位(寄存器 0.15)

④ 重启自动协商(寄存器 0.9)

⑤ 从掉电到上电的切换

⑥ 链路断开

当选择前两种自动协商类型的时候,通过硬件配置在复位的情况下,基于所使用的数字接口类型进行配置,具体的配置方法在前面3.5节硬件配置里面有详细的描述。

这里重点讲解第一种自动协商类型,10/100/1000BASE-T Copper Auto-Negotiation类型,也就是通过铜线接到RJ45进行外部数据传输方式。

使用协商机制协商传输线缆上的速率、双工和流量控制,一旦自协商功能发起,PHY决定远程设备是否发起自协商,如果是,PHY和远程设备协商速率、双工。如果远程设备不具备自协商能力,那么PHY将使用并行侦测远程设备的速率,通过侦察功能建立连接,这时候只需要在半双工模式下建立连接。

硬件复位后,自协商可以通过寄存器0.12启用和禁用,自动化MDI/MDIX和自协商可以单独被启用和禁用。当自协商被禁用时,可以通过寄存器0.13、0.6和0.8分别设置,启用自协商后,可以通过寄存器4和9更改新的功能。

自协商功可以通过寄存器配置,也能通过引脚CONFIG[2]配置,关于引脚CONFIG[2]的配置详见3.5节硬件配置详解。

总结:关于自协商功能可以启用和关闭,启用的时候可以通过硬件连接配置,也可以通过软件设置寄存器的值进行配置,一般根据工程应用决定。关闭的时候,可以通过软件配置寄存器的方式要求传输速率、双工和流量控制。

一旦自协商完成,寄存器1、5、6和10的状态值将被改变;速率、双工、页接收和自协商状态也可以被寄存器17和19使用。

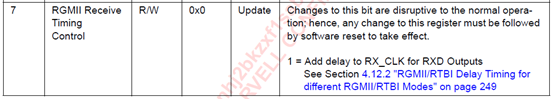

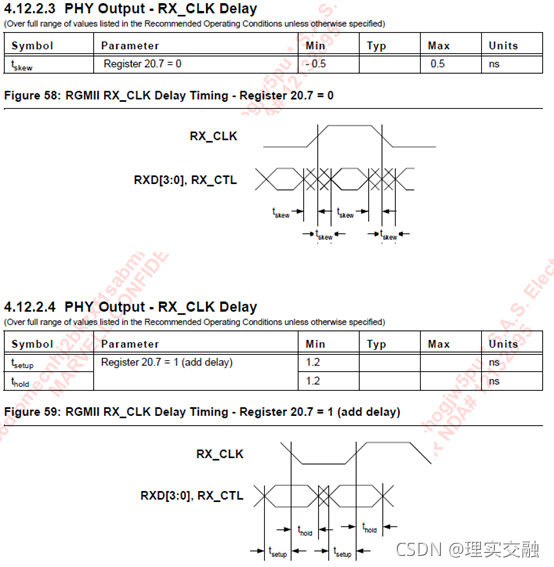

3.8 收发延时使能

收发延时是指在接收或发送数据的时候,将时钟和数据同步的时间差关系,换句话说,就是数据在时钟的setup时刻进行跳变还是在时钟的hold时刻进行跳变。

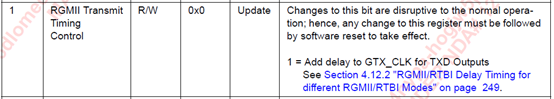

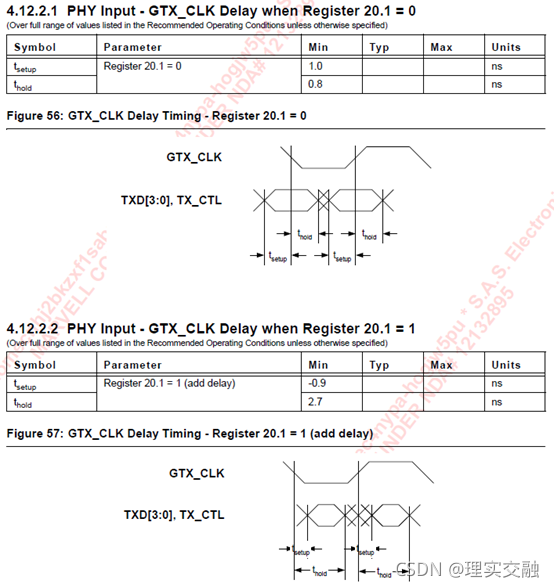

PHY芯片专门设置一个寄存器来管理延时使能问题,寄存器20的bit7和bit1。查看这个寄存器的定义如下:

默认值为0,当设置为1即增加延时时间,即数据时钟呈现中间对齐。

是否需要设置收发延时需要根据对端具体情况,当对端发出的数据为沿对齐时候,需要phy设置数据接收延时;当对端接收数据没有说设置接收延时,需要phy设置发送延时。

具体到硬件层面,setup和hold时间是多少?如何进行的延时?这些问题将通过下面这组图展示出来。

四 寄存器描述

4.1 寄存器表示方法

IEEE只为PHY芯片提供32个地址空间,为了扩展寄存器地址空间,采用分页机制表示。定义寄存器地址0至21,23至28寄存器,通过寄存器22的7bit-0bit来表示页数;30寄存器至31寄存器通过29寄存器的5bit-0bit确定分页。22寄存器和29寄存器不分页。

在数据手册里采用简短的方式表示一个寄存器。表示方法为 register_page.bit:bit。

例如:

寄存器0页数1的bit5-bit0表示为:0_1.5:0

寄存器2的bit3至bit0表示为:2.3:0

寄存器2的bit3表示为:2.3

Note:为了使分页机制正常工作,寄存器27.9必须设置为1,禁用自动介质寄存器选择。

4.2 寄存器地址映射

这里的分页机制是page0为铜线外部接口,page1为光纤外部接口。

前面章节也提到过,关于对PHY芯片的配置,可以依靠纯软件的形式进行,也可以通过硬件配置的方式完成绝大部分的配置工作,使其能正常工作,进行网络传输。

值得注意的是,前面提到的所有的硬件配置,除了PHY地址以外,均可以通过软件配置寄存器的当时进行配置和后期更改、刷新。

至于具体的配置工作需要根据工程实际需求进行。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?