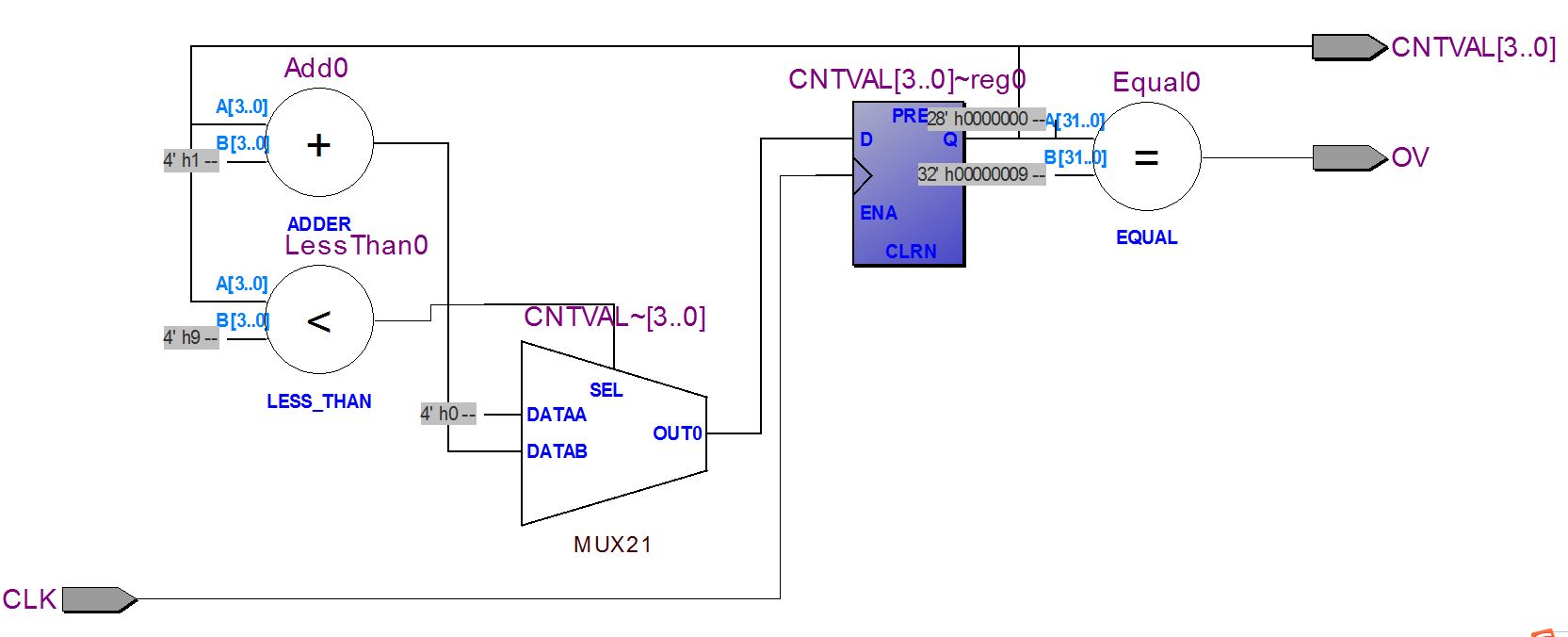

简单的0-9计数器

- RTL:

- 代码片:

module cnt_0to9(

CLK , // clock

CNTVAL, // counter value

OV ); // overflow

parameter CNTVAL_MAX = 9 ;//计数器最大值

parameter CNTVAL_WL = 4 ;//位宽

input CLK;

output [CNTVAL_WL-1:0] CNTVAL;

output OV;

reg [CNTVAL_WL-1:0] CNTVAL;

reg OV;

always @ (posedge CLK) begin

if(CNTVAL < CNTVAL_MAX)

CNTVAL <= CNTVAL + 1'b1;

else

CNTVAL <= 0;

end

always @ (CNTVAL) begin

if(CNTVAL == CNTVAL_MAX)

OV = 1'b1;

else

OV = 1'b0;

end

endmodule // module cnt_0to9时间基准电路 和 带使能的多周期计数器

- 时间基准电路

本文详细介绍了如何使用Verilog设计计数器模块,包括简单的0-9计数器,时间基准电路,带使能的多周期计数器,以及具备清零和暂停功能的0-9.9秒计时秒表。通过代码片段和原理图展示了具体实现方法。

本文详细介绍了如何使用Verilog设计计数器模块,包括简单的0-9计数器,时间基准电路,带使能的多周期计数器,以及具备清零和暂停功能的0-9.9秒计时秒表。通过代码片段和原理图展示了具体实现方法。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?