浮点数的转化

浮点数:小数点位置可以浮动的数据。

常用下式表示: (类似于科学计数法)

N为浮点数,M为尾数,E为阶码(即指数),R为阶的基数(一般R为2或8或16)

浮点数在计算机里面的表示:阶符+阶码+数符+尾数<二进制>

eg:分别求X= , Y=

的浮点数,注:阶符1位,阶码2位,数符1位,尾数3位

转化为二进制,

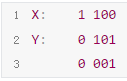

X,Y写为7位浮点数为:X=0 01 1 001

Y=0 10 0 101

浮点数的加减法

步骤:

1.对阶——2.尾数运算——3.规格化处理——4.舍入处理——5.溢出判断

对阶:目的—使两个操作数的小数点对齐,即让阶码相同

操作—先求阶差(△E),即阶码小的尾数右移1位,阶码+1,直到相同为止 (只是尾数右移,不包含数符)

注:求阶差(△E)—前半部分做差(阶符+阶码)

//对上题X与Y求阶差 [△E]补=001-010=111 真值为-001 即△E=-1 ∴对阶后X=0 10 1 100

尾数运算:将尾数相加减 (连同数符位) 注:相减是加其补码

// 对上题X+Y有

规格化处理:

规格化处理主要是针对浮点数的尾数部分,规格化的尾数格式要求如下:

单符号位:

0.1XX……X (尾数采用原码、补码、反码表示,正数的规格化格式)

1.0XX……X (尾数采用补码、反码表示,负数的规格化格式)

1.1XX……X (尾数采用原码表示,负数的规格化格式)

双符号位:

尾数采用补码表示形式时,正数的规格化格式为00.1XXX,负数的规格化格式为:11.0XXX

注:单符号位(0正1负) 双符号位(00正11负)

引入双符号位是为了检测是否有溢出,符号位为"01"的时候称为"上溢",为"10"时,称为"下溢"。

小结:补码单符号位是否规格化标准:符号位与尾数最高位不同才算是规格化,相同为非规格化。

对于非规格化的数:左归和右归

左规:尾数需要向左移位,每移1位阶码值减1,直到为规格化数为止。

右规:尾数需要向右移位,每移1位阶码值加1,直到为规格化数为止。

必须右归:运算结果产生溢出(双符号位01,10,最高符号位有进位或借位)

在最高有效位前补相应数量的0,10.XXX格式右规后的格式为11.0XXX,01.XXX格式右规后的格式为00.1XXX

必须左归:符号位与尾数最高有效位相同时(出现0.1XX or 1.0XX)

左规时最低有效位后补相应位数的0,eg:1.1101111——将11011111左移两位——1.01111100

舍入处理

对阶,左归,右归时,尾数要向左or右移位,移位后尾数就会有误差,因此须舍入处理,减小误差。

两种减小误差的方法:

“0舍1入法”:类似四舍五入,即左规或右规时丢弃的是0,则舍去不计,若丢弃的是1,要将尾数的末尾加1。

eg同上:1.11011111,需要左规,得到1.01111100

可见左移时去掉的是前面的两位1,此情况就需要在尾数的最后一位加1,这样进行舍入处理的结果就是:1.01111101

‘‘恒置1法’’:

只要有数位被左规或者右规丢弃,就要在尾数的末尾恒置1。精确度不高,∵丢弃0和1的概率各占一半。

溢出处理

双符号位补码形式:出现了"01"或者是"10"的形式就直接判断溢出

单符号位:需要根据对尾数进行规格化处理后的阶码是否超出了当前阶码所能表示的取值范围来判定。

右规时:尾数每向右移一位阶码就加1,最终可能导致阶码超出了当前阶码所能表示的数值范围,这称为"上溢"。

即:当阶码有4位(1个符号位)时,最大表示111(+7),如果再右移一位,阶码加1,发生上溢

左规时:同理。因为左规后可能超出了用于存储阶码的存储位所能表示的最小值,称为"下溢"。

若是上溢,计算机立即停止运算,做中断处理。

若是下溢,计算机将整个尾数按0处理。

两个例子

第一题:

第二题:

8518

8518

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?