目录

二.线下实验

管脚绑定模版

#----------------------------------------------------------------------------------

#-- Engineer: switch_swq

#-- Create Date: 2024/04/18 13:02:24

#----------------------------------------------------------------------------------

#CLK_100M

set_property PACKAGE_PIN E10 [get_ports clk]

set_property IOSTANDARD LVCMOS18 [get_ports clk]

#SW0~15

set_property IOSTANDARD LVCMOS18 [get_ports {a_in[0]}]

set_property IOSTANDARD LVCMOS18 [get_ports {a_in[1]}]

set_property IOSTANDARD LVCMOS18 [get_ports {a_in[2]}]

set_property IOSTANDARD LVCMOS18 [get_ports {a_in[3]}]

set_property IOSTANDARD LVCMOS18 [get_ports {a_in[4]}]

set_property IOSTANDARD LVCMOS18 [get_ports {a_in[5]}]

set_property IOSTANDARD LVCMOS18 [get_ports {a_in[6]}]

set_property IOSTANDARD LVCMOS18 [get_ports {a_in[7]}]

set_property PACKAGE_PIN C9 [get_ports {a_in[0]}]

set_property PACKAGE_PIN B9 [get_ports {a_in[1]}]

set_property PACKAGE_PIN G11 [get_ports {a_in[2]}]

set_property PACKAGE_PIN F10 [get_ports {a_in[3]}]

set_property PACKAGE_PIN D10 [get_ports {a_in[4]}]

set_property PACKAGE_PIN E11 [get_ports {a_in[5]}]

set_property PACKAGE_PIN D11 [get_ports {a_in[6]}]

set_property PACKAGE_PIN A14 [get_ports {a_in[7]}]

set_property IOSTANDARD LVCMOS18 [get_ports {b_in[0]}]

set_property IOSTANDARD LVCMOS18 [get_ports {b_in[1]}]

set_property IOSTANDARD LVCMOS18 [get_ports {b_in[2]}]

set_property IOSTANDARD LVCMOS18 [get_ports {b_in[3]}]

set_property IOSTANDARD LVCMOS18 [get_ports {b_in[4]}]

set_property IOSTANDARD LVCMOS18 [get_ports {b_in[5]}]

set_property IOSTANDARD LVCMOS18 [get_ports {b_in[6]}]

set_property IOSTANDARD LVCMOS18 [get_ports {b_in[7]}]

set_property PACKAGE_PIN B10 [get_ports {b_in[0]}]

set_property PACKAGE_PIN A10 [get_ports {b_in[1]}]

set_property PACKAGE_PIN B15 [get_ports {b_in[2]}]

set_property PACKAGE_PIN A15 [get_ports {b_in[3]}]

set_property PACKAGE_PIN A13 [get_ports {b_in[4]}]

set_property PACKAGE_PIN A12 [get_ports {b_in[5]}]

set_property PACKAGE_PIN D8 [get_ports {b_in[6]}]

set_property PACKAGE_PIN D9 [get_ports {b_in[7]}]

#SW16~23

set_property IOSTANDARD LVCMOS18 [get_ports {c_in[0]}]

set_property IOSTANDARD LVCMOS18 [get_ports {c_in[1]}]

set_property IOSTANDARD LVCMOS18 [get_ports {c_in[2]}]

set_property IOSTANDARD LVCMOS18 [get_ports {c_in[3]}]

set_property IOSTANDARD LVCMOS18 [get_ports {c_in[4]}]

set_property IOSTANDARD LVCMOS18 [get_ports {c_in[5]}]

set_property IOSTANDARD LVCMOS18 [get_ports {c_in[6]}]

set_property IOSTANDARD LVCMOS18 [get_ports {c_in[7]}]

set_property PACKAGE_PIN F8 [get_ports {c_in[0]}]

set_property PACKAGE_PIN F9 [get_ports {c_in[1]}]

set_property PACKAGE_PIN H11 [get_ports {c_in[2]}]

set_property PACKAGE_PIN H12 [get_ports {c_in[3]}]

set_property PACKAGE_PIN G14 [get_ports {c_in[4]}]

set_property PACKAGE_PIN J10 [get_ports {c_in[5]}]

set_property PACKAGE_PIN H14 [get_ports {c_in[6]}]

set_property PACKAGE_PIN J11 [get_ports {c_in[7]}]

#sw31~24

set_property PACKAGE_PIN J8 [get_ports rst]

set_property IOSTANDARD LVCMOS18 [get_ports rst]

set_property PACKAGE_PIN J14 [get_ports key_in]

set_property IOSTANDARD LVCMOS18 [get_ports key_in]

set_property PACKAGE_PIN H9 [get_ports wr]

set_property IOSTANDARD LVCMOS18 [get_ports wr]

set_property PACKAGE_PIN H8 [get_ports rd]

set_property IOSTANDARD LVCMOS18 [get_ports rd]

set_property PACKAGE_PIN G10 [get_ports a]

set_property IOSTANDARD LVCMOS18 [get_ports a]

set_property PACKAGE_PIN G9 [get_ports b]

set_property IOSTANDARD LVCMOS18 [get_ports b]

set_property PACKAGE_PIN J13 [get_ports c]

set_property IOSTANDARD LVCMOS18 [get_ports c]

set_property PACKAGE_PIN H13 [get_ports d]

set_property IOSTANDARD LVCMOS18 [get_ports d]

#SEG_DIG1~16

set_property IOSTANDARD LVCMOS33 [get_ports {seg_dig[15]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg_dig[14]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg_dig[13]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg_dig[12]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg_dig[11]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg_dig[10]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg_dig[9]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg_dig[8]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg_dig[7]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg_dig[6]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg_dig[5]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg_dig[4]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg_dig[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg_dig[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg_dig[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg_dig[0]}]

set_property PACKAGE_PIN A23 [get_ports {seg_dig[15]}]

set_property PACKAGE_PIN A24 [get_ports {seg_dig[14]}]

set_property PACKAGE_PIN D26 [get_ports {seg_dig[13]}]

set_property PACKAGE_PIN C26 [get_ports {seg_dig[12]}]

set_property PACKAGE_PIN A20 [get_ports {seg_dig[11]}]

set_property PACKAGE_PIN J25 [get_ports {seg_dig[10]}]

set_property PACKAGE_PIN J24 [get_ports {seg_dig[9]}]

set_property PACKAGE_PIN H22 [get_ports {seg_dig[8]}]

set_property PACKAGE_PIN K21 [get_ports {seg_dig[7]}]

set_property PACKAGE_PIN L23 [get_ports {seg_dig[6]}]

set_property PACKAGE_PIN B25 [get_ports {seg_dig[5]}]

set_property PACKAGE_PIN B26 [get_ports {seg_dig[4]}]

set_property PACKAGE_PIN C24 [get_ports {seg_dig[3]}]

set_property PACKAGE_PIN D21 [get_ports {seg_dig[2]}]

set_property PACKAGE_PIN C22 [get_ports {seg_dig[1]}]

set_property PACKAGE_PIN B20 [get_ports {seg_dig[0]}]

#seg_data

set_property PACKAGE_PIN E26 [get_ports {seg_data[7]}]

set_property PACKAGE_PIN J26 [get_ports {seg_data[6]}]

set_property PACKAGE_PIN H26 [get_ports {seg_data[5]}]

set_property PACKAGE_PIN H21 [get_ports {seg_data[4]}]

set_property PACKAGE_PIN G21 [get_ports {seg_data[3]}]

set_property PACKAGE_PIN H23 [get_ports {seg_data[2]}]

set_property PACKAGE_PIN H24 [get_ports {seg_data[1]}]

set_property PACKAGE_PIN J21 [get_ports {seg_data[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg_data[7]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg_data[6]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg_data[5]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg_data[4]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg_data[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg_data[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg_data[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg_data[0]}]

#LED

set_property IOSTANDARD LVCMOS33 [get_ports {data_out[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {data_out[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {data_out[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {data_out[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {data_out[4]}]

set_property IOSTANDARD LVCMOS33 [get_ports {data_out[5]}]

set_property IOSTANDARD LVCMOS33 [get_ports {data_out[6]}]

set_property IOSTANDARD LVCMOS33 [get_ports {data_out[7]}]

set_property PACKAGE_PIN G16 [get_ports {data_out[0]}]

set_property PACKAGE_PIN H16 [get_ports {data_out[1]}]

set_property PACKAGE_PIN D16 [get_ports {data_out[2]}]

set_property PACKAGE_PIN D15 [get_ports {data_out[3]}]

set_property PACKAGE_PIN C18 [get_ports {data_out[4]}]

set_property PACKAGE_PIN C17 [get_ports {data_out[5]}]

set_property PACKAGE_PIN B19 [get_ports {data_out[6]}]

set_property PACKAGE_PIN C19 [get_ports {data_out[7]}]

#led15

set_property PACKAGE_PIN L20 [get_ports empty]

set_property IOSTANDARD LVCMOS33 [get_ports empty]

#led11

set_property PACKAGE_PIN J20 [get_ports full]

set_property IOSTANDARD LVCMOS33 [get_ports full]通用模块模版

时钟分频:

----------------------------------------------------------------------------------

-- Engineer: switch_swq

-- Create Date: 2024/04/18 13:02:24

----------------------------------------------------------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity clk_div is

generic(

DIV_NUM:integer:=10000

);

Port (

rst:in std_logic;

clk_in:in std_logic;

clk_out:out std_logic

);

end clk_div;

architecture Behavioral of clk_div is

begin

process(rst,clk_in)

variable count:integer:=0;

begin

if(rst='1')then count:=0;

elsif(clk_in='1'and clk_in'event)then

count:=count+1;

if(count<=DIV_NUM/2)then

clk_out<='1';

elsif(count>DIV_NUM/2 and count<DIV_NUM)then

clk_out<='0';

elsif(count>=DIV_NUM)then

count:=0;

end if;

end if;

end process;

end Behavioral;

按键消抖:

----------------------------------------------------------------------------------

-- Engineer: switch_swq

-- Create Date: 2024/04/18 13:02:24

----------------------------------------------------------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity key_stroke is

generic(CLK_FRE:integer:=100000000);

Port (

clk:in std_logic;

reset:in std_logic;

key_in:in std_logic;

output:out std_logic

);

end key_stroke;

architecture Behavioral of key_stroke is

type states is(s0,s1,s2,s3);

signal state:states;

begin

process(reset,clk,key_in)

variable count_num:integer:=3*CLK_FRE/1000;--delay 3ms

variable count:integer:=0;

begin

if reset='0'then

state<=s0;

count:=0;

output<='0';

elsif(clk='1'and clk'event)then

case state is

when s0=>if(key_in='1')then count:=0;output<='0';state<=s1;end if;

when s1=>

count:=count+1;

if (count>=count_num) then state<=s2; end if;

when s2=>

if(key_in='1')then output<='1';state<=s3;

--if(key_in='1')then output<='1';state<=s0;--one clk cycle

elsif(key_in='0')then state<=s0;

end if;

when s3=>if(key_in='0')then state<=s0;end if;

end case;

end if;

end process;

end Behavioral;

数码管显示:

----------------------------------------------------------------------------------

-- Engineer: switch_swq

-- Create Date: 2024/04/18 13:02:24

----------------------------------------------------------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity seg_dis is

port(

rst,clk:in std_logic;

data_in_A,data_in_B,data_in_C,data_in_D:in std_logic_vector(15 downto 0);

seg_dig:out std_logic_vector(15 downto 0);

seg_data:out std_logic_vector(7 downto 0)--管脚连接顺序:dp,g,f,e,d,c,b,a

);

end seg_dis;

architecture Behavioral of seg_dis is

signal data_in_line: std_logic_vector(3 downto 0);

type states is(s0,s1,s2,s3,s4,s5,s6,s7,s8,s9,s10,s11,s12,s13,s14,s15);

signal state,next_state:states;

begin

process(rst,clk)

begin

if(rst='1')then state<=s0;

elsif(clk='1'and clk'event)then

state<=next_state;

end if;

end process;

process(state)

begin

case state is

when s0 => seg_dig<=not"0000000000000001"; data_in_line<=data_in_A(3 downto 0); next_state<=s1;

when s1 => seg_dig<=not"0000000000000010"; data_in_line<=data_in_A(7 downto 4); next_state<=s2;

when s2 => seg_dig<=not"0000000000000100"; data_in_line<=data_in_A(11 downto 8); next_state<=s3;

when s3 => seg_dig<=not"0000000000001000"; data_in_line<=data_in_A(15 downto 12); next_state<=s4;

when s4 => seg_dig<=not"0000000000010000"; data_in_line<=data_in_B(3 downto 0); next_state<=s5;

when s5 => seg_dig<=not"0000000000100000"; data_in_line<=data_in_B(7 downto 4); next_state<=s6;

when s6 => seg_dig<=not"0000000001000000"; data_in_line<=data_in_B(11 downto 8); next_state<=s7;

when s7 => seg_dig<=not"0000000010000000"; data_in_line<=data_in_B(15 downto 12); next_state<=s8;

when s8 => seg_dig<=not"0000000100000000"; data_in_line<=data_in_C(3 downto 0); next_state<=s9;

when s9 => seg_dig<=not"0000001000000000"; data_in_line<=data_in_C(7 downto 4); next_state<=s10;

when s10=> seg_dig<=not"0000010000000000"; data_in_line<=data_in_C(11 downto 8); next_state<=s11;

when s11=> seg_dig<=not"0000100000000000"; data_in_line<=data_in_C(15 downto 12); next_state<=s12;

when s12=> seg_dig<=not"0001000000000000"; data_in_line<=data_in_D(3 downto 0); next_state<=s13;

when s13=> seg_dig<=not"0010000000000000"; data_in_line<=data_in_D(7 downto 4); next_state<=s14;

when s14=> seg_dig<=not"0100000000000000"; data_in_line<=data_in_D(11 downto 8); next_state<=s15;

when s15=> seg_dig<=not"1000000000000000"; data_in_line<=data_in_D(15 downto 12); next_state<=s0;

when others=>next_state<=s0;

end case;

end process;

process(data_in_line)

begin

case data_in_line is

when "0000"=>seg_data<=not"00111111";

when "0001"=>seg_data<=not"00000110";

when "0010"=>seg_data<=not"01011011";

when "0011"=>seg_data<=not"01001111";

when "0100"=>seg_data<=not"01100110";

when "0101"=>seg_data<=not"01101101";

when "0110"=>seg_data<=not"01111101";

when "0111"=>seg_data<=not"00000111";

when "1000"=>seg_data<=not"01111111";

when "1001"=>seg_data<=not"01101111";

when "1010"=>seg_data<=not"01110111";

when "1011"=>seg_data<=not"01111100";

when "1100"=>seg_data<=not"00111001";

when "1101"=>seg_data<=not"01011110";

when "1110"=>seg_data<=not"01111001";

when "1111"=>seg_data<=not"01110001";

when others=>seg_data<=not"11111111";

end case;

end process;

end Behavioral;注意事项

1.器件型号:xc7k160tfbg676-2

2.输入一般cmos18 输出cmos33

3.输入数码管的时钟需分频

4.按键加消抖

5.程序的运行结合.xdc文件进行理解

1.跑马灯控制设计

功能叙述:初始情况下 Y0=‘1’,其它为‘0’。然后,在 en 为高电平的情况下,在时钟信 号 clk 的下降沿进行移位。当 dir=‘1’时,每来一个时钟信号,循环左移一位,当 dir=‘0’时, 每来一个时钟,循环右移一位。 另外,移位控制时钟可以选择为按键,即每按键一次相当于一个时钟信号,系统可以在 按键和系统分频时钟之间进行选择。

资源使用:

1)用 LED0~LED7 作为跑马灯输出显示,LED7 为高位,LED0 为低位;

2)SW0 为循环方向控制;

3)SW1 为工作允许 EN 控制端;

4)计数时钟频率为 1Hz,通过对 50Mhz 系统时钟分频得到;

5)扩展:可以由按键来控制循环(按键为 BTN_SOUTH),即每按一次 BTN_SOUTH, 则完成一次移位。通过 SW2 选择移位控制时钟沿。

源文件:

----------------------------------------------------------------------------------

-- Engineer: switch_swq

-- Create Date: 2024/04/18 13:02:24

----------------------------------------------------------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity run_led is

Port(

en,dir,sel,clk,con:in std_logic;

y:out std_logic_vector(7 downto 0)

);

end run_led;

architecture Behavioral of run_led is

signal input:std_logic;

signal clk_div:std_logic;

begin

process(clk)

variable clk_cnt:integer:=0;

variable clk_cnt_2:integer:=0;

begin

if(clk='1'and clk'event)then

clk_cnt_2:=clk_cnt_2+1;

if(clk_cnt_2>=10000)then

clk_cnt:=clk_cnt+1;

clk_cnt_2:=0;

end if;

if(clk_cnt<5000)then clk_div<='1';

elsif(clk_cnt>=5000)then clk_div<='0';

end if;

if(clk_cnt>=10000)then clk_cnt:=0;

end if;

end if;

end process;

process(clk,en,clk_div,con,sel)

begin

if(en='1')then

if(sel='0')then input<=clk_div;

elsif(sel='1')then input<=con;

end if;

elsif(en='0')then input<='0';

end if;

end process;

process(input,dir)

variable count:integer:=0;

begin

if(input='1'and input'event)then

if(dir='1')then

count:=count+1;

if(count>7)then count:=0;end if;

elsif(dir='0')then

count:=count-1;

if(count<0)then count:=7;end if;

end if;

if(count=0)then y<="00000001";

elsif(count=1)then y<="00000010";

elsif(count=2)then y<="00000100";

elsif(count=3)then y<="00001000";

elsif(count=4)then y<="00010000";

elsif(count=5)then y<="00100000";

elsif(count=6)then y<="01000000";

elsif(count=7)then y<="10000000";

else y<="11111111";

end if;

end if;

end process;

end Behavioral;

testbench:

----------------------------------------------------------------------------------

-- Engineer: switch_swq

-- Create Date: 2024/04/18 13:02:24

----------------------------------------------------------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity run_led_tb is

end run_led_tb;

architecture Behavioral of run_led_tb is

component run_led

Port(

en,dir,sel,clk,con:in std_logic;

y:out std_logic_vector(7 downto 0)

);

end component;

SIGNAL en,dir,sel,clk,con: std_logic;

SIGNAL y: std_logic_vector(7 downto 0);

begin

run_led_inst:run_led port map(en=>en,dir=>dir,sel=>sel,clk=>clk,con=>con,y=>y);

clock:process

begin

clk<='1';

wait for 5ns;

clk<='0';

wait for 5ns;

end process;

key:process

begin

con<='1';

wait for 25ns;

con<='0';

wait for 25ns;

end process;

test:process

begin

en<='0';

sel<='1';

dir<='1';

wait for 25ns;

en<='1';

wait;

end process;

end Behavioral;

xdc:

#----------------------------------------------------------------------------------

#-- Engineer: switch_swq

#-- Create Date: 2024/04/18 13:02:24

#----------------------------------------------------------------------------------

set_property PACKAGE_PIN C9 [get_ports dir]

set_property PACKAGE_PIN AF12 [get_ports con]

set_property PACKAGE_PIN B9 [get_ports en]

set_property PACKAGE_PIN E10 [get_ports clk]

set_property PACKAGE_PIN G11 [get_ports sel]

set_property PACKAGE_PIN G16 [get_ports {y[0]}]

set_property PACKAGE_PIN H16 [get_ports {y[1]}]

set_property PACKAGE_PIN D16 [get_ports {y[2]}]

set_property PACKAGE_PIN D15 [get_ports {y[3]}]

set_property PACKAGE_PIN C18 [get_ports {y[4]}]

set_property PACKAGE_PIN C17 [get_ports {y[5]}]

set_property PACKAGE_PIN B19 [get_ports {y[6]}]

set_property PACKAGE_PIN C19 [get_ports {y[7]}]

set_property IOSTANDARD LVCMOS33 [get_ports {y[4]}]

set_property IOSTANDARD LVCMOS33 [get_ports {y[5]}]

set_property IOSTANDARD LVCMOS33 [get_ports {y[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {y[6]}]

set_property IOSTANDARD LVCMOS33 [get_ports {y[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {y[7]}]

set_property IOSTANDARD LVCMOS33 [get_ports {y[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {y[3]}]

set_property DRIVE 12 [get_ports {y[4]}]

set_property DRIVE 12 [get_ports {y[5]}]

set_property DRIVE 12 [get_ports {y[0]}]

set_property DRIVE 12 [get_ports {y[6]}]

set_property DRIVE 12 [get_ports {y[1]}]

set_property DRIVE 12 [get_ports {y[7]}]

set_property DRIVE 12 [get_ports {y[2]}]

set_property DRIVE 12 [get_ports {y[3]}]

set_property IOSTANDARD LVCMOS18 [get_ports dir]

set_property IOSTANDARD LVCMOS18 [get_ports con]

set_property IOSTANDARD LVCMOS18 [get_ports en]

set_property IOSTANDARD LVCMOS18 [get_ports clk]

set_property IOSTANDARD LVCMOS18 [get_ports sel]

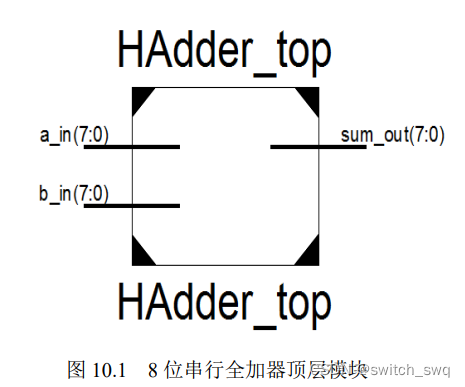

2.8 位并行全加器设计+数码管显示程序设计

注:数码管部分未使用优化代码

其中 a_in,b_in:数据输入,使用板上开关(SW0~SW15); sum_out:运算结果输出,使用 LED 显示运算结果。

(1)用硬件描述语言实现 16 个七段数码管扫描显示模块

七段数码管扫描显示模块电路如图所示,主要包括顶层的数码管扫描显示模块,以及输入数据向七段数码管进行译码的模块。

该模块实现数码管扫描显示功能,扩展板上的 16 个数码管四个一组,分为 A,B,C,D 四组。模块管脚说明如下:clk 为系统的时钟输入,rst 信号为复位信号,data_in_A(15:0)为 A 组四个数码管的输入显示值,其中,data_in_A(3:0)对应于第一个数码管的输入显示值; data_in_A(7:4)对应第二个数码管的输入显示值;data_in_A(11:8)对应第三个数码管的输入显 示值;data_in_A(15:12)对应第四个数码管的输入显示值,其它各组与 A 组分配一致; data_in_B(15:0)为 B 组四个数码管的输入显示值;data_in_C(15:0)为 C 组四个数码管的输入显 示值;data_in_D(15:0)为 D 组四个数码管的输入显示值;seg_sel(3:0)为数码管选择编码输出 信号,seg_data(7:0)为数码管显示数据输出。

该模块实现将输入的 4 为二进制数转换为数码管显示的数据;其中,data_in(3:0)为输入 值,seg_data(7:0)为数码管编码的输出值。

源码:

顶层:

----------------------------------------------------------------------------------

-- Engineer: switch_swq

-- Create Date: 2024/04/18 13:02:24

----------------------------------------------------------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity adder is

Port (

clk,rst:in std_logic;

a,b:in std_logic_vector(7 downto 0);

c:in std_logic;

c_out:out std_logic;

sel_out:out std_logic_vector(15 downto 0);

seg_data:out std_logic_vector(7 downto 0)

);

end adder;

architecture Behavioral of adder is

component clk_div

generic(

DIV_NUM:integer:=10000

);

Port (

clk_in:in std_logic;

clk_out:out std_logic

);

end component;

component seg_dis

port(

rst,clk:in std_logic;

data_in_A,data_in_B,data_in_C,data_in_D:in std_logic_vector(15 downto 0);

seg_sel:out std_logic_vector(3 downto 0);

seg_data:out std_logic_vector(7 downto 0)

);

end component;

component decoder4_16

Port (

sel_in:in std_logic_vector(3 downto 0);

sel_out:out std_logic_vector(15 downto 0)

);

end component;

signal clk_out_line:std_logic;

signal sum_line:std_logic_vector(16 downto 0);

signal data_line:std_logic_vector(15 downto 0);

signal c_line:std_logic;

signal sel_out_line:std_logic_vector(3 downto 0);

begin

clk_div_inst:clk_div generic map(10000)port map(clk,clk_out_line);

seg_dis_inst:seg_dis port map(rst,clk_out_line,data_line,"0000000000000000","0000000000000000","0000000000000000",sel_out_line,seg_data);

decoder4_16_inst:decoder4_16 port map(sel_out_line,sel_out);

process(a,b,c)

begin

sum_line<=("00000000"&a)+("00000000"&b)+("0000000000000000"&c);

data_line<=sum_line(15 downto 0);

c_out<=sum_line(16);

end process;

end Behavioral;

模块:

----------------------------------------------------------------------------------

-- Engineer: switch_swq

-- Create Date: 2024/04/18 13:02:24

----------------------------------------------------------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity decoder4_16 is

Port (

sel_in:in std_logic_vector(3 downto 0);

sel_out:out std_logic_vector(15 downto 0)

);

end decoder4_16;

architecture Behavioral of decoder4_16 is

begin

process(sel_in)

begin

case sel_in is

when "0000"=>sel_out<=not"0000000000000001";

when "0001"=>sel_out<=not"0000000000000010";

when "0010"=>sel_out<=not"0000000000000100";

when "0011"=>sel_out<=not"0000000000001000";

when "0100"=>sel_out<=not"0000000000010000";

when "0101"=>sel_out<=not"0000000000100000";

when "0110"=>sel_out<=not"0000000001000000";

when "0111"=>sel_out<=not"0000000010000000";

when "1000"=>sel_out<=not"0000000100000000";

when "1001"=>sel_out<=not"0000001000000000";

when "1010"=>sel_out<=not"0000010000000000";

when "1011"=>sel_out<=not"0000100000000000";

when "1100"=>sel_out<=not"0001000000000000";

when "1101"=>sel_out<=not"0010000000000000";

when "1110"=>sel_out<=not"0100000000000000";

when "1111"=>sel_out<=not"1000000000000000";

when others=>sel_out<=not"1111111111111111";

end case;

end process;

end Behavioral;

----------------------------------------------------------------------------------

-- Engineer: switch_swq

-- Create Date: 2024/04/18 13:02:24

----------------------------------------------------------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity seg_dis is

port(

rst,clk:in std_logic;

data_in_A,data_in_B,data_in_C,data_in_D:in std_logic_vector(15 downto 0);

seg_sel:out std_logic_vector(3 downto 0);

seg_data:out std_logic_vector(7 downto 0)

);

end seg_dis;

architecture Behavioral of seg_dis is

component data2seg

port(

data_in:in std_logic_vector(3 downto 0);

seg_data:out std_logic_vector(7 downto 0)

);

end component;

signal data_in_line: std_logic_vector(3 downto 0);

type states is(s0,s1,s2,s3,s4,s5,s6,s7,s8,s9,s10,s11,s12,s13,s14,s15);

signal state,next_state:states;

begin

data2seg_inst:data2seg port map(data_in_line,seg_data);

process(rst,clk)

begin

if(rst='1')then state<=s0;

elsif(clk='1'and clk'event)then

state<=next_state;

end if;

end process;

process(state)

begin

case state is

when s0=>

seg_sel<="0000";

data_in_line<=data_in_A(3 downto 0);

next_state<=s1;

when s1=>

seg_sel<="0001";

data_in_line<=data_in_A(7 downto 4);

next_state<=s2;

when s2=>

seg_sel<="0010";

data_in_line<=data_in_A(11 downto 8);

next_state<=s3;

when s3=>

seg_sel<="0011";

data_in_line<=data_in_A(15 downto 12);

next_state<=s4;

when s4=>seg_sel<="0100";data_in_line<=data_in_B(3 downto 0);next_state<=s5;

when s5=>seg_sel<="0101";data_in_line<=data_in_B(7 downto 4);next_state<=s6;

when s6=>seg_sel<="0110";data_in_line<=data_in_B(11 downto 8);next_state<=s7;

when s7=>seg_sel<="0111";data_in_line<=data_in_B(15 downto 12);next_state<=s8;

when s8=>seg_sel<="1000";data_in_line<=data_in_C(3 downto 0);next_state<=s9;

when s9=>seg_sel<="1001";data_in_line<=data_in_C(7 downto 4);next_state<=s10;

when s10=>seg_sel<="1010";data_in_line<=data_in_C(11 downto 8);next_state<=s11;

when s11=>seg_sel<="1011";data_in_line<=data_in_C(15 downto 12);next_state<=s12;

when s12=>seg_sel<="1100";data_in_line<=data_in_D(3 downto 0);next_state<=s13;

when s13=>seg_sel<="1101";data_in_line<=data_in_D(7 downto 4);next_state<=s14;

when s14=>seg_sel<="1110";data_in_line<=data_in_D(11 downto 8);next_state<=s15;

when s15=>seg_sel<="1111";data_in_line<=data_in_D(15 downto 12);next_state<=s0;

when others=>state<=next_state;

end case;

end process;

end Behavioral;----------------------------------------------------------------------------------

-- Engineer: switch_swq

-- Create Date: 2024/04/18 13:02:24

----------------------------------------------------------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity data2seg is

port(

data_in:in std_logic_vector(3 downto 0);

seg_data:out std_logic_vector(7 downto 0)

);

end data2seg;

architecture Behavioral of data2seg is

begin

process(data_in)

begin

case data_in is

when "0000"=>seg_data<=not"00111111";

when "0001"=>seg_data<=not"00000110";

when "0010"=>seg_data<=not"01011011";

when "0011"=>seg_data<=not"01001111";

when "0100"=>seg_data<=not"01100110";

when "0101"=>seg_data<=not"00110111";

when "0110"=>seg_data<=not"01111101";

when "0111"=>seg_data<=not"00000111";

when "1000"=>seg_data<=not"01111111";

when "1001"=>seg_data<=not"01101111";

when "1010"=>seg_data<=not"01110111";

when "1011"=>seg_data<=not"01111100";

when "1100"=>seg_data<=not"00111000";

when "1101"=>seg_data<=not"01011110";

when "1110"=>seg_data<=not"01111001";

when "1111"=>seg_data<=not"01110001";

when others=>seg_data<=not"11111111";

end case;

end process;

end Behavioral;testbench:

----------------------------------------------------------------------------------

-- Engineer: switch_swq

-- Create Date: 2024/04/18 13:02:24

----------------------------------------------------------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity adder_tb is

-- Port ( );

end adder_tb;

architecture Behavioral of adder_tb is

component adder

Port (

clk,rst:in std_logic;

a,b:in std_logic_vector(7 downto 0);

c:in std_logic;

c_out:out std_logic;

sel_out:out std_logic_vector(15 downto 0);

seg_data:out std_logic_vector(7 downto 0)

);

end component;

signal clk,rst :std_logic;

signal a,b :std_logic_vector(7 downto 0);

signal c :std_logic;

signal c_out : std_logic;

signal sel_out : std_logic_vector(15 downto 0);

signal seg_data: std_logic_vector(7 downto 0);

begin

adder_inst:adder port map(clk,rst,a,b,c,c_out,sel_out,seg_data);

clock:process

begin

clk<='1';

wait for 5ns;

clk<='0';

wait for 5ns;

end process;

restart:process

begin

rst<='1';

wait for 25ns;

rst<='0';

wait;

end process;

test:process

begin

a<="00100010";

b<="01000100";

c<='1';

wait for 100ns;

a<="11111111";

b<="11111111";

c<='1';

wait;

end process;

end Behavioral;

xdc:

set_property PACKAGE_PIN E26 [get_ports {seg_data[7]}]

set_property PACKAGE_PIN J26 [get_ports {seg_data[6]}]

set_property PACKAGE_PIN H26 [get_ports {seg_data[5]}]

set_property PACKAGE_PIN H21 [get_ports {seg_data[4]}]

set_property PACKAGE_PIN G21 [get_ports {seg_data[3]}]

set_property PACKAGE_PIN H23 [get_ports {seg_data[2]}]

set_property PACKAGE_PIN H24 [get_ports {seg_data[1]}]

set_property PACKAGE_PIN J21 [get_ports {seg_data[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg_data[7]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg_data[6]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg_data[5]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg_data[4]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg_data[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg_data[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg_data[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg_data[0]}]

set_property PACKAGE_PIN E10 [get_ports clk]

set_property PACKAGE_PIN C9 [get_ports {a[0]}]

set_property PACKAGE_PIN B9 [get_ports {a[1]}]

set_property PACKAGE_PIN G11 [get_ports {a[2]}]

set_property PACKAGE_PIN F10 [get_ports {a[3]}]

set_property PACKAGE_PIN D10 [get_ports {a[4]}]

set_property PACKAGE_PIN E11 [get_ports {a[5]}]

set_property PACKAGE_PIN D11 [get_ports {a[6]}]

set_property PACKAGE_PIN A14 [get_ports {a[7]}]

set_property PACKAGE_PIN B10 [get_ports {b[0]}]

set_property PACKAGE_PIN A10 [get_ports {b[1]}]

set_property PACKAGE_PIN B15 [get_ports {b[2]}]

set_property PACKAGE_PIN A15 [get_ports {b[3]}]

set_property PACKAGE_PIN A13 [get_ports {b[4]}]

set_property PACKAGE_PIN A12 [get_ports {b[5]}]

set_property PACKAGE_PIN D8 [get_ports {b[6]}]

set_property PACKAGE_PIN D9 [get_ports {b[7]}]

set_property IOSTANDARD LVCMOS18 [get_ports {b[0]}]

set_property IOSTANDARD LVCMOS18 [get_ports {b[1]}]

set_property IOSTANDARD LVCMOS18 [get_ports {b[2]}]

set_property IOSTANDARD LVCMOS18 [get_ports {b[3]}]

set_property IOSTANDARD LVCMOS18 [get_ports {b[4]}]

set_property IOSTANDARD LVCMOS18 [get_ports {b[5]}]

set_property IOSTANDARD LVCMOS18 [get_ports {b[6]}]

set_property IOSTANDARD LVCMOS18 [get_ports {b[7]}]

set_property IOSTANDARD LVCMOS18 [get_ports {a[0]}]

set_property IOSTANDARD LVCMOS18 [get_ports {a[1]}]

set_property IOSTANDARD LVCMOS18 [get_ports {a[2]}]

set_property IOSTANDARD LVCMOS18 [get_ports {a[3]}]

set_property IOSTANDARD LVCMOS18 [get_ports {a[4]}]

set_property IOSTANDARD LVCMOS18 [get_ports {a[5]}]

set_property IOSTANDARD LVCMOS18 [get_ports {a[6]}]

set_property IOSTANDARD LVCMOS18 [get_ports {a[7]}]

set_property IOSTANDARD LVCMOS18 [get_ports clk]

set_property IOSTANDARD LVCMOS18 [get_ports rst]

set_property IOSTANDARD LVCMOS33 [get_ports c_out]

set_property IOSTANDARD LVCMOS18 [get_ports c]

set_property PACKAGE_PIN J14 [get_ports c]

set_property PACKAGE_PIN G16 [get_ports c_out]

set_property PACKAGE_PIN J8 [get_ports rst]

#set_property IOSTANDARD LVCMOS18 [get_ports {sel_in[0]}]

#set_property IOSTANDARD LVCMOS18 [get_ports {sel_in[1]}]

#set_property IOSTANDARD LVCMOS18 [get_ports {sel_in[2]}]

#set_property IOSTANDARD LVCMOS18 [get_ports {sel_in[3]}]

#set_property PACKAGE_PIN F8 [get_ports {sel_in[0]}]

#set_property PACKAGE_PIN F9 [get_ports {sel_in[1]}]

#set_property PACKAGE_PIN H11 [get_ports {sel_in[2]}]

#set_property PACKAGE_PIN H12 [get_ports {sel_in[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sel_out[7]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sel_out[10]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sel_out[4]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sel_out[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sel_out[15]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sel_out[12]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sel_out[6]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sel_out[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sel_out[13]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sel_out[5]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sel_out[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sel_out[8]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sel_out[11]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sel_out[14]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sel_out[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sel_out[9]}]

set_property PACKAGE_PIN A23 [get_ports {sel_out[15]}]

set_property PACKAGE_PIN A24 [get_ports {sel_out[14]}]

set_property PACKAGE_PIN D26 [get_ports {sel_out[13]}]

set_property PACKAGE_PIN C26 [get_ports {sel_out[12]}]

set_property PACKAGE_PIN A20 [get_ports {sel_out[11]}]

set_property PACKAGE_PIN J25 [get_ports {sel_out[10]}]

set_property PACKAGE_PIN J24 [get_ports {sel_out[9]}]

set_property PACKAGE_PIN H22 [get_ports {sel_out[8]}]

set_property PACKAGE_PIN K21 [get_ports {sel_out[7]}]

set_property PACKAGE_PIN L23 [get_ports {sel_out[6]}]

set_property PACKAGE_PIN B25 [get_ports {sel_out[5]}]

set_property PACKAGE_PIN B26 [get_ports {sel_out[4]}]

set_property PACKAGE_PIN C24 [get_ports {sel_out[3]}]

set_property PACKAGE_PIN D21 [get_ports {sel_out[2]}]

set_property PACKAGE_PIN C22 [get_ports {sel_out[1]}]

set_property PACKAGE_PIN B20 [get_ports {sel_out[0]}]3.阵列乘法器设计

源码:

顶层:

----------------------------------------------------------------------------------

-- Engineer: switch_swq

-- Create Date: 2024/04/18 13:02:24

----------------------------------------------------------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity array_multiplier_seg is

Port (

rst,clk:in std_logic;

a_in,b_in:in std_logic_vector(7 downto 0);

seg_dig:out std_logic_vector(15 downto 0);

seg_data:out std_logic_vector(7 downto 0)

);

end array_multiplier_seg;

architecture Behavioral of array_multiplier_seg is

component clk_div

generic(

DIV_NUM:integer:=10000

);

Port (

clk_in:in std_logic;

clk_out:out std_logic

);

end component;

component array_multiplier

Port (

clk:in std_logic;

a_in,b_in:in std_logic_vector(7 downto 0);

sum_out:out std_logic_vector(15 downto 0)

);

end component;

component seg_dis

port(

rst,clk:in std_logic;

data_in_A,data_in_B,data_in_C,data_in_D:in std_logic_vector(15 downto 0);

seg_sel:out std_logic_vector(3 downto 0);

seg_data:out std_logic_vector(7 downto 0)

);

end component;

component decoder4_16

Port (

sel_in:in std_logic_vector(3 downto 0);

sel_out:out std_logic_vector(15 downto 0)

);

end component;

signal clk_out_line:std_logic;

signal sum_out_line:std_logic_vector(15 downto 0);

signal seg_dig_line:std_logic_vector(3 downto 0);

begin

clk_div_inst:clk_div generic map(10000)port map(clk,clk_out_line);

array_multiplier_inst:array_multiplier port map(clk_out_line,a_in,b_in,sum_out_line);

seg_dis_inst:seg_dis port map(rst,clk_out_line,sum_out_line,"0000000000000000","0000000000000000","0000000000000000",seg_dig_line,seg_data);

decoder4_16_inst:decoder4_16 port map(seg_dig_line,seg_dig);

end Behavioral;

----------------------------------------------------------------------------------

-- Engineer: switch_swq

-- Create Date: 2024/04/18 13:02:24

----------------------------------------------------------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity array_multiplier is

Port (

clk:in std_logic;

a_in,b_in:in std_logic_vector(7 downto 0);

sum_out:out std_logic_vector(15 downto 0)

);

end array_multiplier;

architecture Behavioral of array_multiplier is

component array_multiplier_top

Port (

a_in:in std_logic;

b_in:in std_logic_vector(7 downto 0);

s:out std_logic_vector(7 downto 0)

);

end component;

component array_multiplier_unit

Port (

x_in:in std_logic;

y_in:in std_logic_vector(7 downto 0);

c_in:in std_logic_vector(6 downto 0);

z_in:in std_logic_vector(7 downto 0);

c_out:out std_logic_vector(6 downto 0);

z_out:out std_logic_vector(7 downto 0)

);

end component;

component array_multiplier_low

Port (

z_in,c_in:in std_logic_vector(6 downto 0);

s_out:out std_logic_vector(7 downto 0)

);

end component;

signal z_in0:std_logic_vector(7 downto 0);

signal z_in1:std_logic_vector(7 downto 0);

signal z_in2:std_logic_vector(7 downto 0);

signal z_in3:std_logic_vector(7 downto 0);

signal z_in4:std_logic_vector(7 downto 0);

signal z_in5:std_logic_vector(7 downto 0);

signal z_in6:std_logic_vector(7 downto 0);

signal z_in7:std_logic_vector(7 downto 0);

signal c_in1:std_logic_vector(6 downto 0);

signal c_in2:std_logic_vector(6 downto 0);

signal c_in3:std_logic_vector(6 downto 0);

signal c_in4:std_logic_vector(6 downto 0);

signal c_in5:std_logic_vector(6 downto 0);

signal c_in6:std_logic_vector(6 downto 0);

signal c_in7:std_logic_vector(6 downto 0);

begin

array_multiplier_top_inst:array_multiplier_top port map(a_in(0),b_in,z_in0);

array_multiplier_unit_inst1:array_multiplier_unit port map(a_in(1),b_in,"0000000",z_in0,c_in1,z_in1);

array_multiplier_unit_inst2:array_multiplier_unit port map(a_in(2),b_in,c_in1,z_in1,c_in2,z_in2);

array_multiplier_unit_inst3:array_multiplier_unit port map(a_in(3),b_in,c_in2,z_in2,c_in3,z_in3);

array_multiplier_unit_inst4:array_multiplier_unit port map(a_in(4),b_in,c_in3,z_in3,c_in4,z_in4);

array_multiplier_unit_inst5:array_multiplier_unit port map(a_in(5),b_in,c_in4,z_in4,c_in5,z_in5);

array_multiplier_unit_inst6:array_multiplier_unit port map(a_in(6),b_in,c_in5,z_in5,c_in6,z_in6);

array_multiplier_unit_inst7:array_multiplier_unit port map(a_in(7),b_in,c_in6,z_in6,c_in7,z_in7);

array_multiplier_low_inst:array_multiplier_low port map(z_in7(7 downto 1),c_in7,sum_out(15 downto 8));

process(clk,a_in,b_in)

begin

sum_out(0)<=z_in0(0);

sum_out(1)<=z_in1(0);

sum_out(2)<=z_in2(0);

sum_out(3)<=z_in3(0);

sum_out(4)<=z_in4(0);

sum_out(5)<=z_in5(0);

sum_out(6)<=z_in6(0);

sum_out(7)<=z_in7(0);

end process;

end Behavioral;

模块:

----------------------------------------------------------------------------------

-- Engineer: switch_swq

-- Create Date: 2024/04/18 13:02:24

----------------------------------------------------------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity array_multiplier_top is

Port (

a_in:in std_logic;

b_in:in std_logic_vector(7 downto 0);

s:out std_logic_vector(7 downto 0)

);

end array_multiplier_top;

architecture Behavioral of array_multiplier_top is

begin

process(a_in,b_in)

begin

for i in 0 to 7 loop

s(i)<=a_in and b_in(i);

end loop;

end process;

end Behavioral;

----------------------------------------------------------------------------------

-- Engineer: switch_swq

-- Create Date: 2024/04/18 13:02:24

----------------------------------------------------------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity array_multiplier_unit is

Port (

x_in:in std_logic;

y_in:in std_logic_vector(7 downto 0);

c_in:in std_logic_vector(6 downto 0);

z_in:in std_logic_vector(7 downto 0);

c_out:out std_logic_vector(6 downto 0);

z_out:out std_logic_vector(7 downto 0)

);

end array_multiplier_unit;

architecture Behavioral of array_multiplier_unit is

component adder_1bit

Port (

a,b,c_in:in std_logic;

s,c_out:out std_logic

);

end component;

signal a_line:std_logic_vector(7 downto 0);

begin

adder_1bit_inst1:adder_1bit port map(a_line(0),c_in(0),z_in(1),z_out(0),c_out(0));

adder_1bit_inst2:adder_1bit port map(a_line(1),c_in(1),z_in(2),z_out(1),c_out(1));

adder_1bit_inst3:adder_1bit port map(a_line(2),c_in(2),z_in(3),z_out(2),c_out(2));

adder_1bit_inst4:adder_1bit port map(a_line(3),c_in(3),z_in(4),z_out(3),c_out(3));

adder_1bit_inst5:adder_1bit port map(a_line(4),c_in(4),z_in(5),z_out(4),c_out(4));

adder_1bit_inst6:adder_1bit port map(a_line(5),c_in(5),z_in(6),z_out(5),c_out(5));

adder_1bit_inst7:adder_1bit port map(a_line(6),c_in(6),z_in(7),z_out(6),c_out(6));

process(x_in,y_in)

begin

z_out(7)<=x_in and y_in(7);

for i in 0 to 7 loop

a_line(i)<=x_in and y_in(i);

end loop;

end process;

end Behavioral;

----------------------------------------------------------------------------------

-- Engineer: switch_swq

-- Create Date: 2024/04/18 13:02:24

----------------------------------------------------------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity array_multiplier_low is

Port (

z_in,c_in:in std_logic_vector(6 downto 0);

s_out:out std_logic_vector(7 downto 0)

);

end array_multiplier_low;

architecture Behavioral of array_multiplier_low is

component adder_1bit

Port (

a,b,c_in:in std_logic;

s,c_out:out std_logic

);

end component;

signal c_line:std_logic_vector(5 downto 0);

begin

adder_1bit_inst0:adder_1bit port map(z_in(0),c_in(0),'0',s_out(0),c_line(0));

adder_1bit_inst1:adder_1bit port map(z_in(1),c_in(1),c_line(0),s_out(1),c_line(1));

adder_1bit_inst2:adder_1bit port map(z_in(2),c_in(2),c_line(1),s_out(2),c_line(2));

adder_1bit_inst3:adder_1bit port map(z_in(3),c_in(3),c_line(2),s_out(3),c_line(3));

adder_1bit_inst4:adder_1bit port map(z_in(4),c_in(4),c_line(3),s_out(4),c_line(4));

adder_1bit_inst5:adder_1bit port map(z_in(5),c_in(5),c_line(4),s_out(5),c_line(5));

adder_1bit_inst6:adder_1bit port map(z_in(6),c_in(6),c_line(5),s_out(6),s_out(7));

end Behavioral;

----------------------------------------------------------------------------------

-- Engineer: switch_swq

-- Create Date: 2024/04/18 13:02:24

----------------------------------------------------------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity adder_1bit is

Port (

a,b,c_in:in std_logic;

s,c_out:out std_logic

);

end adder_1bit;

architecture Behavioral of adder_1bit is

begin

process(a,b,c_in)

begin

s<=a xor b xor c_in;

c_out<=(a and b)or((a xor b)and c_in);

end process;

end Behavioral;

testbench:

----------------------------------------------------------------------------------

-- Engineer: switch_swq

-- Create Date: 2024/04/18 13:02:24

----------------------------------------------------------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity array_multiplier_tb is

-- Port ( );

end array_multiplier_tb;

architecture Behavioral of array_multiplier_tb is

component array_multiplier_seg

Port (

rst,clk:in std_logic;

a_in,b_in:in std_logic_vector(7 downto 0);

seg_dig:out std_logic_vector(15 downto 0);

seg_data:out std_logic_vector(7 downto 0)

);

end component;

signal rst,clk:std_logic;

signal a_in,b_in:std_logic_vector(7 downto 0);

signal seg_dig:std_logic_vector(15 downto 0);

signal seg_data:std_logic_vector(7 downto 0);

begin

array_multiplier_seg_inst:array_multiplier_seg port map(rst,clk,a_in,b_in,seg_dig,seg_data);

clock:process

begin

clk<='1';

wait for 5ns;

clk<='0';

wait for 5ns;

end process;

restart:process

begin

rst<='1';

wait for 25ns;

rst<='0';

wait;

end process;

test:process

begin

a_in<="10111101";

b_in<="11001010";

wait;

end process;

end Behavioral;

xdc:

#----------------------------------------------------------------------------------

#-- Engineer: switch_swq

#-- Create Date: 2024/04/18 13:02:24

#----------------------------------------------------------------------------------

#CLK_100M

set_property PACKAGE_PIN E10 [get_ports clk]

set_property IOSTANDARD LVCMOS18 [get_ports clk]

#SW0~15

set_property IOSTANDARD LVCMOS18 [get_ports {a_in[0]}]

set_property IOSTANDARD LVCMOS18 [get_ports {a_in[1]}]

set_property IOSTANDARD LVCMOS18 [get_ports {a_in[2]}]

set_property IOSTANDARD LVCMOS18 [get_ports {a_in[3]}]

set_property IOSTANDARD LVCMOS18 [get_ports {a_in[4]}]

set_property IOSTANDARD LVCMOS18 [get_ports {a_in[5]}]

set_property IOSTANDARD LVCMOS18 [get_ports {a_in[6]}]

set_property IOSTANDARD LVCMOS18 [get_ports {a_in[7]}]

set_property PACKAGE_PIN C9 [get_ports {a_in[0]}]

set_property PACKAGE_PIN B9 [get_ports {a_in[1]}]

set_property PACKAGE_PIN G11 [get_ports {a_in[2]}]

set_property PACKAGE_PIN F10 [get_ports {a_in[3]}]

set_property PACKAGE_PIN D10 [get_ports {a_in[4]}]

set_property PACKAGE_PIN E11 [get_ports {a_in[5]}]

set_property PACKAGE_PIN D11 [get_ports {a_in[6]}]

set_property PACKAGE_PIN A14 [get_ports {a_in[7]}]

set_property IOSTANDARD LVCMOS18 [get_ports {b_in[0]}]

set_property IOSTANDARD LVCMOS18 [get_ports {b_in[1]}]

set_property IOSTANDARD LVCMOS18 [get_ports {b_in[2]}]

set_property IOSTANDARD LVCMOS18 [get_ports {b_in[3]}]

set_property IOSTANDARD LVCMOS18 [get_ports {b_in[4]}]

set_property IOSTANDARD LVCMOS18 [get_ports {b_in[5]}]

set_property IOSTANDARD LVCMOS18 [get_ports {b_in[6]}]

set_property IOSTANDARD LVCMOS18 [get_ports {b_in[7]}]

set_property PACKAGE_PIN B10 [get_ports {b_in[0]}]

set_property PACKAGE_PIN A10 [get_ports {b_in[1]}]

set_property PACKAGE_PIN B15 [get_ports {b_in[2]}]

set_property PACKAGE_PIN A15 [get_ports {b_in[3]}]

set_property PACKAGE_PIN A13 [get_ports {b_in[4]}]

set_property PACKAGE_PIN A12 [get_ports {b_in[5]}]

set_property PACKAGE_PIN D8 [get_ports {b_in[6]}]

set_property PACKAGE_PIN D9 [get_ports {b_in[7]}]

#SEG_DIG1~16

set_property IOSTANDARD LVCMOS33 [get_ports {seg_dig[15]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg_dig[14]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg_dig[13]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg_dig[12]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg_dig[11]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg_dig[10]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg_dig[9]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg_dig[8]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg_dig[7]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg_dig[6]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg_dig[5]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg_dig[4]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg_dig[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg_dig[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg_dig[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg_dig[0]}]

set_property PACKAGE_PIN A23 [get_ports {seg_dig[15]}]

set_property PACKAGE_PIN A24 [get_ports {seg_dig[14]}]

set_property PACKAGE_PIN D26 [get_ports {seg_dig[13]}]

set_property PACKAGE_PIN C26 [get_ports {seg_dig[12]}]

set_property PACKAGE_PIN A20 [get_ports {seg_dig[11]}]

set_property PACKAGE_PIN J25 [get_ports {seg_dig[10]}]

set_property PACKAGE_PIN J24 [get_ports {seg_dig[9]}]

set_property PACKAGE_PIN H22 [get_ports {seg_dig[8]}]

set_property PACKAGE_PIN K21 [get_ports {seg_dig[7]}]

set_property PACKAGE_PIN L23 [get_ports {seg_dig[6]}]

set_property PACKAGE_PIN B25 [get_ports {seg_dig[5]}]

set_property PACKAGE_PIN B26 [get_ports {seg_dig[4]}]

set_property PACKAGE_PIN C24 [get_ports {seg_dig[3]}]

set_property PACKAGE_PIN D21 [get_ports {seg_dig[2]}]

set_property PACKAGE_PIN C22 [get_ports {seg_dig[1]}]

set_property PACKAGE_PIN B20 [get_ports {seg_dig[0]}]

#seg_data

set_property PACKAGE_PIN E26 [get_ports {seg_data[7]}]

set_property PACKAGE_PIN J26 [get_ports {seg_data[6]}]

set_property PACKAGE_PIN H26 [get_ports {seg_data[5]}]

set_property PACKAGE_PIN H21 [get_ports {seg_data[4]}]

set_property PACKAGE_PIN G21 [get_ports {seg_data[3]}]

set_property PACKAGE_PIN H23 [get_ports {seg_data[2]}]

set_property PACKAGE_PIN H24 [get_ports {seg_data[1]}]

set_property PACKAGE_PIN J21 [get_ports {seg_data[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg_data[7]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg_data[6]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg_data[5]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg_data[4]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg_data[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg_data[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg_data[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg_data[0]}]

set_property PACKAGE_PIN J8 [get_ports rst]

set_property IOSTANDARD LVCMOS18 [get_ports rst]

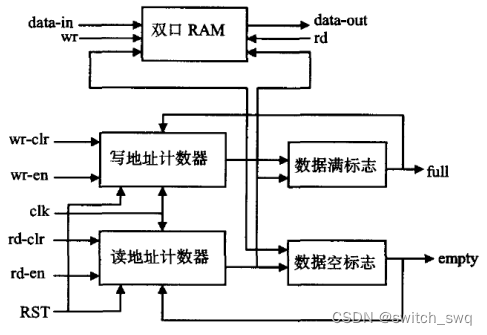

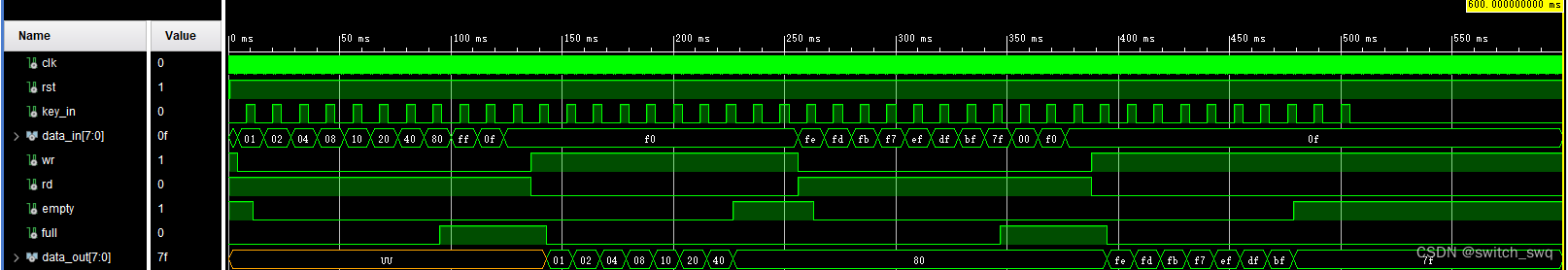

4.先进先出 FIFO 的设计

源码:

顶层:

----------------------------------------------------------------------------------

-- Engineer: switch_swq

-- Create Date: 2024/04/18 13:02:24

-- Module Name: FIFO_ring_test - Behavioral

----------------------------------------------------------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity FIFO_ring_test is

generic(

CLK_FRE:integer:=100000000;

cycle_max:positive:=3;--最大读写圈数

depth:positive:=3;

width:positive:=8

);

Port(

clk:in std_logic;

rst:in std_logic;

key_in:in std_logic;

data_in:in std_logic_vector(7 downto 0);

wr:in std_logic;

rd:in std_logic;

empty:out std_logic;

full:out std_logic;

data_out:out std_logic_vector(7 downto 0)

);

end FIFO_ring_test;

architecture Behavioral of FIFO_ring_test is

component key_stroke

generic(CLK_FRE:integer:=100000000);

Port (

clk:in std_logic;

reset:in std_logic;

key_in:in std_logic;

output:out std_logic

);

end component;

component FIFO_ring

generic(

cycle_max:positive:=3;--最大读写圈数

depth:positive:=3;

width:positive:=8

);

Port(

clk,clk_rd,clk_wr:in std_logic;

rst:in std_logic;

data_in:in std_logic_vector(7 downto 0);

wr:in std_logic;

rd:in std_logic;

empty:out std_logic;

full:out std_logic;

data_out:out std_logic_vector(7 downto 0)

);

end component;

signal out_put:std_logic;

begin

key_stroke_inst:key_stroke generic map(CLK_FRE)port map(clk=>clk,reset=>rst,key_in=>key_in,output=>out_put);

FIFO_ring_inst:FIFO_ring generic map(cycle_max,depth,width)port map(rst=>rst,clk=>clk,clk_rd=>out_put,clk_wr=>out_put,wr=>wr,rd=>rd,data_in=>data_in,full=>full,empty=>empty,data_out=>data_out);

end Behavioral;

----------------------------------------------------------------------------------

-- Engineer: switch_swq

-- Create Date: 2024/04/18 13:02:24

-- Module Name: FIFO_ring - Behavioral

----------------------------------------------------------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity FIFO_ring is

generic(

cycle_max:positive:=3;--最大读写圈数

depth:positive:=3;

width:positive:=8

);

Port(

clk,clk_rd,clk_wr:in std_logic;

rst:in std_logic;

data_in:in std_logic_vector(7 downto 0);

wr:in std_logic;

rd:in std_logic;

empty:out std_logic;

full:out std_logic;

data_out:out std_logic_vector(7 downto 0)

);

end FIFO_ring;

architecture Behavioral of FIFO_ring is

component duaram

generic(

depth:positive:=3;

width:positive:=8

);

Port(

clka:in std_logic;

wr:in std_logic;

wr_en:in std_logic;

addra:in std_logic_vector(depth-1 downto 0);

datain:in std_logic_vector(width-1 downto 0);

clkb:in std_logic;

rd:in std_logic;

rd_en:in std_logic;

addrb:in std_logic_vector(depth-1 downto 0);

dataout:out std_logic_vector(width-1 downto 0)

);

end component;

component FIFO_ring_duaram_controller

generic(

cycle_max:positive;--最大读写圈数

depth:positive

);

Port(

rst:in std_logic;

clk,clka,clkb:in std_logic;

wq:in std_logic;

rq:in std_logic;

full:out std_logic;

empty:out std_logic;

wr_pt:out std_logic_vector(depth-1 downto 0);

rd_pt:out std_logic_vector(depth-1 downto 0)

);

end component;

signal rp_line:std_logic_vector(depth-1 downto 0);

signal wp_line:std_logic_vector(depth-1 downto 0);

signal empty_line:std_logic;

signal full_line:std_logic;

begin

duaram_inst:duaram generic map(depth,width)port map(clka=>clk_wr,clkb=>clk_rd,datain=>data_in,dataout=>data_out,addra=>wp_line,addrb=>rp_line,rd=>rd,wr=>wr,rd_en=>empty_line,wr_en=>full_line);

FIFO_ring_duaram_controller_inst:FIFO_ring_duaram_controller generic map(cycle_max,depth)port map(rst=>rst,clk=>clk,clkb=>clk_rd,clka=>clk_wr,wq=>wr,rq=>rd,full=>full_line,empty=>empty_line,wr_pt=>wp_line,rd_pt=>rp_line);

process(empty_line,full_line)

begin

empty<=empty_line;

full<=full_line;

end process;

end Behavioral;

模块:

----------------------------------------------------------------------------------

-- Engineer: switch_swq

-- Create Date: 2024/04/18 13:02:24

-- Module Name: FIFO_ring - Behavioral

----------------------------------------------------------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity duaram is

generic(

depth:positive;

width:positive

);

Port(

clka:in std_logic;

wr:in std_logic;

wr_en:in std_logic;

addra:in std_logic_vector(depth-1 downto 0);

datain:in std_logic_vector(width-1 downto 0);

clkb:in std_logic;

rd:in std_logic;

rd_en:in std_logic;

addrb:in std_logic_vector(depth-1 downto 0);

dataout:out std_logic_vector(width-1 downto 0)

);

end duaram;

architecture Behavioral of duaram is

type ram is array(2**depth-1 downto 0)of std_logic_vector(width-1 downto 0);

signal dualram:ram;

begin

process(clka)

begin

if(clka'event and clka='1')then

if(wr='0'and wr_en='0')then dualram(conv_integer(addra))<=datain;end if;

end if;

end process;

process(clkb)

begin

if(clkb'event and clkb='1')then

if(rd='0'and rd_en='0')then dataout<=dualram(conv_integer(addrb));end if;

end if;

end process;

end Behavioral;

----------------------------------------------------------------------------------

-- Engineer: switch_swq

-- Create Date: 2024/04/18 13:02:24

-- Module Name: FIFO_ring_duaram_controller - Behavioral

----------------------------------------------------------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity FIFO_ring_duaram_controller is

generic(

cycle_max:positive;--最大读写圈数

depth:positive

);

Port(

rst:in std_logic;

clk,clka,clkb:in std_logic;

wq:in std_logic;

rq:in std_logic;

full:out std_logic;

empty:out std_logic;

wr_pt:out std_logic_vector(depth-1 downto 0);

rd_pt:out std_logic_vector(depth-1 downto 0)

);

end FIFO_ring_duaram_controller;

architecture Behavioral of FIFO_ring_duaram_controller is

signal wr_pt_t:std_logic_vector(depth+cycle_max-1 downto 0);

signal rd_pt_t:std_logic_vector(depth+cycle_max-1 downto 0);

signal full_line:std_logic;

signal empty_line:std_logic;

begin

--write_pointer

process(rst,clka)

begin

if(rst='0')then

wr_pt_t<=(others=>'0');

elsif(clka'event and clka='1')then

if (wq='0'and full_line='0')then wr_pt_t<=wr_pt_t+1;end if;

end if;

end process;

--read_pointer

process(rst,clkb)

begin

if(rst='0')then

rd_pt_t<=(others=>'0');

elsif(clkb'event and clkb='1')then

if (rq='0'and empty_line='0')then

rd_pt_t<=rd_pt_t+1;

end if;

end if;

end process;

--judge_status

process(rst,clk)

begin

if(rst='0')then empty_line<='1';full_line<='0';

elsif(clk'event and clk='1')then

if(wr_pt_t=rd_pt_t)then empty_line<='1';full_line<='0';

elsif(wr_pt_t=rd_pt_t+2**depth)then empty_line<='0';full_line<='1';

else empty_line<='0';full_line<='0';

end if;

end if;

end process;

process(wr_pt_t)

begin wr_pt<=wr_pt_t(depth-1 downto 0);

end process;

process(rd_pt_t)

begin rd_pt<=rd_pt_t(depth-1 downto 0);

end process;

process(empty_line)

begin empty<=empty_line;

end process;

process(full_line)

begin full<=full_line;

end process;

end Behavioral;

testbench:

----------------------------------------------------------------------------------

-- Engineer: switch_swq

-- Create Date: 2024/04/18 13:02:24

-- Module Name: FIFO_ring_tb - Behavioral

----------------------------------------------------------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity FIFO_ring_tb is

-- Port ( );

end FIFO_ring_tb;

architecture Behavioral of FIFO_ring_tb is

component FIFO_ring_test

generic(

CLK_FRE:integer:=100000000;

cycle_max:positive:=3;--最大读写圈数

depth:positive:=3;

width:positive:=8

);

Port(

clk:in std_logic;

rst:in std_logic;

key_in:in std_logic;

data_in:in std_logic_vector(7 downto 0);

wr:in std_logic;

rd:in std_logic;

empty:out std_logic;

full:out std_logic;

data_out:out std_logic_vector(7 downto 0)

);

end component;

signal clk:std_logic;

signal rst:std_logic;

signal key_in:std_logic;

signal data_in:std_logic_vector(7 downto 0);

signal wr:std_logic;

signal rd:std_logic;

signal empty:std_logic;

signal full:std_logic;

signal data_out:std_logic_vector(7 downto 0);

begin

FIFO_ring_test_inst:FIFO_ring_test generic map(100000000,3,8)port map(clk,rst,key_in,data_in,wr,rd,empty,full,data_out);

clock:process

begin

clk<='0';

wait for 5ns;

clk<='1';

wait for 5ns;

end process;

reset:process

begin

rst<='0';

wait for 25ns;

rst<='1';

wait;

end process;

test:process

begin

rd<='1';

wr<='1';

data_in<="00000000";

key_in<='0';

wait for 4ms;

rd<='1';

wr<='0';

data_in<="00000001";

wait for 4ms;

key_in<='1';

wait for 4ms;

key_in<='0';

wait for 4ms;

data_in<="00000010";

wait for 4ms;

key_in<='1';

wait for 4ms;

key_in<='0';

wait for 4ms;

data_in<="00000100";

wait for 4ms;

key_in<='1';

wait for 4ms;

key_in<='0';

wait for 4ms;

data_in<="00001000";

wait for 4ms;

key_in<='1';

wait for 4ms;

key_in<='0';

wait for 4ms;

data_in<="00010000";

wait for 4ms;

key_in<='1';

wait for 4ms;

key_in<='0';

wait for 4ms;

data_in<="00100000";

wait for 4ms;

key_in<='1';

wait for 4ms;

key_in<='0';

wait for 4ms;

data_in<="01000000";

wait for 4ms;

key_in<='1';

wait for 4ms;

key_in<='0';

wait for 4ms;

data_in<="10000000";

wait for 4ms;

key_in<='1';

wait for 4ms;

key_in<='0';

wait for 4ms;

data_in<="11111111";

wait for 4ms;

key_in<='1';

wait for 4ms;

key_in<='0';

wait for 4ms;

data_in<="00001111";

wait for 4ms;

key_in<='1';

wait for 4ms;

key_in<='0';

wait for 4ms;

data_in<="11110000";

wait for 4ms;

key_in<='1';

wait for 4ms;

key_in<='0';

wait for 4ms;

wr<='1';

rd<='0';

wait for 4ms;

key_in<='1';

wait for 4ms;

key_in<='0';

wait for 4ms;

wait for 4ms;

key_in<='1';

wait for 4ms;

key_in<='0';

wait for 4ms;

wait for 4ms;

key_in<='1';

wait for 4ms;

key_in<='0';

wait for 4ms;

wait for 4ms;

key_in<='1';

wait for 4ms;

key_in<='0';

wait for 4ms;

wait for 4ms;

key_in<='1';

wait for 4ms;

key_in<='0';

wait for 4ms;

wait for 4ms;

key_in<='1';

wait for 4ms;

key_in<='0';

wait for 4ms;

wait for 4ms;

key_in<='1';

wait for 4ms;

key_in<='0';

wait for 4ms;

wait for 4ms;

key_in<='1';

wait for 4ms;

key_in<='0';

wait for 4ms;

wait for 4ms;

key_in<='1';

wait for 4ms;

key_in<='0';

wait for 4ms;

wait for 4ms;

key_in<='1';

wait for 4ms;

key_in<='0';

wait for 4ms;

rd<='1';

wr<='0';

data_in<=not"00000001";

wait for 4ms;

key_in<='1';

wait for 4ms;

key_in<='0';

wait for 4ms;

data_in<=not"00000010";

wait for 4ms;

key_in<='1';

wait for 4ms;

key_in<='0';

wait for 4ms;

data_in<=not"00000100";

wait for 4ms;

key_in<='1';

wait for 4ms;

key_in<='0';

wait for 4ms;

data_in<=not"00001000";

wait for 4ms;

key_in<='1';

wait for 4ms;

key_in<='0';

wait for 4ms;

data_in<=not"00010000";

wait for 4ms;

key_in<='1';

wait for 4ms;

key_in<='0';

wait for 4ms;

data_in<=not"00100000";

wait for 4ms;

key_in<='1';

wait for 4ms;

key_in<='0';

wait for 4ms;

data_in<=not"01000000";

wait for 4ms;

key_in<='1';

wait for 4ms;

key_in<='0';

wait for 4ms;

data_in<=not"10000000";

wait for 4ms;

key_in<='1';

wait for 4ms;

key_in<='0';

wait for 4ms;

data_in<=not"11111111";

wait for 4ms;

key_in<='1';

wait for 4ms;

key_in<='0';

wait for 4ms;

data_in<=not"00001111";

wait for 4ms;

key_in<='1';

wait for 4ms;

key_in<='0';

wait for 4ms;

data_in<=not"11110000";

wait for 4ms;

key_in<='1';

wait for 4ms;

key_in<='0';

wait for 4ms;

wr<='1';

rd<='0';

wait for 4ms;

key_in<='1';

wait for 4ms;

key_in<='0';

wait for 4ms;

wait for 4ms;

key_in<='1';

wait for 4ms;

key_in<='0';

wait for 4ms;

wait for 4ms;

key_in<='1';

wait for 4ms;

key_in<='0';

wait for 4ms;

wait for 4ms;

key_in<='1';

wait for 4ms;

key_in<='0';

wait for 4ms;

wait for 4ms;

key_in<='1';

wait for 4ms;

key_in<='0';

wait for 4ms;

wait for 4ms;

key_in<='1';

wait for 4ms;

key_in<='0';

wait for 4ms;

wait for 4ms;

key_in<='1';

wait for 4ms;

key_in<='0';

wait for 4ms;

wait for 4ms;

key_in<='1';

wait for 4ms;

key_in<='0';

wait for 4ms;

wait for 4ms;

key_in<='1';

wait for 4ms;

key_in<='0';

wait for 4ms;

wait for 4ms;

key_in<='1';

wait for 4ms;

key_in<='0';

wait for 4ms;

wait;

end process;

end Behavioral;

xdc:

#----------------------------------------------------------------------------------

#-- Engineer: switch_swq

#-- Create Date: 2024/04/18 13:02:24

#----------------------------------------------------------------------------------

set_property IOSTANDARD LVCMOS18 [get_ports {data_in[0]}]

set_property IOSTANDARD LVCMOS18 [get_ports {data_in[1]}]

set_property IOSTANDARD LVCMOS18 [get_ports {data_in[2]}]

set_property IOSTANDARD LVCMOS18 [get_ports {data_in[3]}]

set_property IOSTANDARD LVCMOS18 [get_ports {data_in[4]}]

set_property IOSTANDARD LVCMOS18 [get_ports {data_in[5]}]

set_property IOSTANDARD LVCMOS18 [get_ports {data_in[6]}]

set_property IOSTANDARD LVCMOS18 [get_ports {data_in[7]}]

set_property PACKAGE_PIN C9 [get_ports {data_in[0]}]

set_property PACKAGE_PIN B9 [get_ports {data_in[1]}]

set_property PACKAGE_PIN G11 [get_ports {data_in[2]}]

set_property PACKAGE_PIN F10 [get_ports {data_in[3]}]

set_property PACKAGE_PIN D10 [get_ports {data_in[4]}]

set_property PACKAGE_PIN E11 [get_ports {data_in[5]}]

set_property PACKAGE_PIN D11 [get_ports {data_in[6]}]

set_property PACKAGE_PIN A14 [get_ports {data_in[7]}]

set_property PACKAGE_PIN E10 [get_ports clk]

set_property IOSTANDARD LVCMOS18 [get_ports clk]

#sw31

set_property PACKAGE_PIN J8 [get_ports rst]

set_property IOSTANDARD LVCMOS18 [get_ports rst]

#sw30

set_property PACKAGE_PIN J14 [get_ports key_in]

set_property IOSTANDARD LVCMOS18 [get_ports key_in]

#sw29

set_property PACKAGE_PIN H9 [get_ports wr]

set_property IOSTANDARD LVCMOS18 [get_ports wr]

#sw28

set_property PACKAGE_PIN H8 [get_ports rd]

set_property IOSTANDARD LVCMOS18 [get_ports rd]

#led15

set_property PACKAGE_PIN L20 [get_ports empty]

set_property IOSTANDARD LVCMOS33 [get_ports empty]

#led11

set_property PACKAGE_PIN J20 [get_ports full]

set_property IOSTANDARD LVCMOS33 [get_ports full]

#led0-7

set_property IOSTANDARD LVCMOS33 [get_ports {data_out[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {data_out[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {data_out[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {data_out[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {data_out[4]}]

set_property IOSTANDARD LVCMOS33 [get_ports {data_out[5]}]

set_property IOSTANDARD LVCMOS33 [get_ports {data_out[6]}]

set_property IOSTANDARD LVCMOS33 [get_ports {data_out[7]}]

set_property PACKAGE_PIN G16 [get_ports {data_out[0]}]

set_property PACKAGE_PIN H16 [get_ports {data_out[1]}]

set_property PACKAGE_PIN D16 [get_ports {data_out[2]}]

set_property PACKAGE_PIN D15 [get_ports {data_out[3]}]

set_property PACKAGE_PIN C18 [get_ports {data_out[4]}]

set_property PACKAGE_PIN C17 [get_ports {data_out[5]}]

set_property PACKAGE_PIN B19 [get_ports {data_out[6]}]

set_property PACKAGE_PIN C19 [get_ports {data_out[7]}]5.PC 程序计数器设计

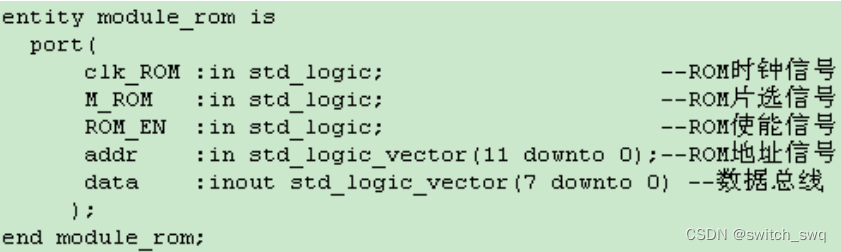

PC 功能分析 加 1 功能、更新地址功能、PC 数值送到数据总线

PC 功能实现

1)全局异步复位功能

ADDR<=“000000000000”;

数据总线高阻态;

2)加 1 功能

clk_PC 上升沿有效;

M_PC 高电平有效,PC+1=>ADDR;

3)地址更新功能

clk_PC 上升沿有效,nLD_PC 低电平有效,新的 PC=>ADDR;

PC 数值送到数据总线,nPCH 和 nPCL 低电平有效,注意分两次输出到总线上,先高 8 位后低 8 位。

注:自行添加按键消抖模块

源码:

----------------------------------------------------------------------------------

-- Engineer: switch_swq

-- Create Date: 2024/04/18 13:02:24

----------------------------------------------------------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity pc is

Port (

rst,clk_PC,M_PC,nLD_PC:in std_logic;

PC_in:in std_logic_vector(11 downto 0);

DATA_BUS:inout std_logic_vector(7 downto 0);

nPCH,nPCL:out std_logic

);

end pc;

architecture Behavioral of pc is

signal pc_count:std_logic_vector(11 downto 0);

signal ADDR:std_logic_vector(11 downto 0);

begin

process(rst,clk_PC)

variable addr_count:integer:=0;

begin

if(rst='1')then

pc_count<=PC_in;

ADDR<=pc_count;

DATA_BUS<="XXXXXXXX";

nPCH<='1';nPCL<='1';

elsif(clk_PC='1'and clk_PC'event)then

if(addr_count=0)then pc_count<=pc_count+1;end if;

if(M_PC='1')then ADDR<=pc_count;end if;

if(nLD_PC='0')then

if(addr_count=0)then DATA_BUS<="0000"& ADDR(11 downto 8);addr_count:=addr_count+1;nPCH<='0';nPCL<='1';

elsif(addr_count=1)then DATA_BUS<=ADDR(7 downto 0);addr_count:=addr_count-1;nPCH<='1';nPCL<='0';

end if;

end if;

end if;

end process;

end Behavioral;

xdc:

#----------------------------------------------------------------------------------

#-- Engineer: switch_swq

#-- Create Date: 2024/04/18 13:02:24

#----------------------------------------------------------------------------------

set_property IOSTANDARD LVCMOS18 [get_ports {PC_in[0]}]

set_property IOSTANDARD LVCMOS18 [get_ports {PC_in[1]}]

set_property IOSTANDARD LVCMOS18 [get_ports {PC_in[2]}]

set_property IOSTANDARD LVCMOS18 [get_ports {PC_in[3]}]

set_property IOSTANDARD LVCMOS18 [get_ports {PC_in[4]}]

set_property IOSTANDARD LVCMOS18 [get_ports {PC_in[5]}]

set_property IOSTANDARD LVCMOS18 [get_ports {PC_in[6]}]

set_property IOSTANDARD LVCMOS18 [get_ports {PC_in[7]}]

set_property PACKAGE_PIN C9 [get_ports {PC_in[0]}]

set_property PACKAGE_PIN B9 [get_ports {PC_in[1]}]

set_property PACKAGE_PIN G11 [get_ports {PC_in[2]}]

set_property PACKAGE_PIN F10 [get_ports {PC_in[3]}]

set_property PACKAGE_PIN D10 [get_ports {PC_in[4]}]

set_property PACKAGE_PIN E11 [get_ports {PC_in[5]}]

set_property PACKAGE_PIN D11 [get_ports {PC_in[6]}]

set_property PACKAGE_PIN A14 [get_ports {PC_in[7]}]

set_property IOSTANDARD LVCMOS18 [get_ports {PC_in[8]}]

set_property IOSTANDARD LVCMOS18 [get_ports {PC_in[9]}]

set_property IOSTANDARD LVCMOS18 [get_ports {PC_in[10]}]

set_property IOSTANDARD LVCMOS18 [get_ports {PC_in[11]}]

set_property PACKAGE_PIN B10 [get_ports {PC_in[8]}]

set_property PACKAGE_PIN A10 [get_ports {PC_in[9]}]

set_property PACKAGE_PIN B15 [get_ports {PC_in[10]}]

set_property PACKAGE_PIN A15 [get_ports {PC_in[11]}]

set_property IOSTANDARD LVCMOS33 [get_ports {DATA_BUS[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {DATA_BUS[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {DATA_BUS[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {DATA_BUS[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {DATA_BUS[4]}]

set_property IOSTANDARD LVCMOS33 [get_ports {DATA_BUS[5]}]

set_property IOSTANDARD LVCMOS33 [get_ports {DATA_BUS[6]}]

set_property IOSTANDARD LVCMOS33 [get_ports {DATA_BUS[7]}]

set_property PACKAGE_PIN G16 [get_ports {DATA_BUS[0]}]

set_property PACKAGE_PIN H16 [get_ports {DATA_BUS[1]}]

set_property PACKAGE_PIN D16 [get_ports {DATA_BUS[2]}]

set_property PACKAGE_PIN D15 [get_ports {DATA_BUS[3]}]

set_property PACKAGE_PIN C18 [get_ports {DATA_BUS[4]}]

set_property PACKAGE_PIN C17 [get_ports {DATA_BUS[5]}]

set_property PACKAGE_PIN B19 [get_ports {DATA_BUS[6]}]

set_property PACKAGE_PIN C19 [get_ports {DATA_BUS[7]}]

#sw31

set_property PACKAGE_PIN J8 [get_ports rst]

set_property IOSTANDARD LVCMOS18 [get_ports rst]

#sw30

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets clk_PC]

set_property PACKAGE_PIN J14 [get_ports clk_PC]

set_property IOSTANDARD LVCMOS18 [get_ports clk_PC]

#sw29

set_property PACKAGE_PIN H9 [get_ports M_PC]

set_property IOSTANDARD LVCMOS18 [get_ports M_PC]

#sw28

set_property PACKAGE_PIN H8 [get_ports nLD_PC]

set_property IOSTANDARD LVCMOS18 [get_ports nLD_PC]

#led15

set_property PACKAGE_PIN L20 [get_ports nPCH]

set_property IOSTANDARD LVCMOS33 [get_ports nPCH]

#led11

set_property PACKAGE_PIN J20 [get_ports nPCL]

set_property IOSTANDARD LVCMOS33 [get_ports nPCL]6.程序存储器 ROM 设计

源码:

----------------------------------------------------------------------------------

-- Engineer: switch_swq

-- Create Date: 2024/04/18 13:02:24

----------------------------------------------------------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_unsigned.ALL;

use IEEE.STD_LOGIC_textio.ALL;

use std.textio.all;

entity ROM is

generic(

depth:positive:=12;

width:positive:=8

);

Port (

clk_ROM,M_ROM,ROM_EN:in std_logic;

addr:in std_logic_vector(11 downto 0);

DATA_BUS:inout std_logic_vector(7 downto 0)

);

end ROM;

architecture Behavioral of ROM is

type matrix is array (integer range<>)of std_logic_vector(width-1 downto 0);

signal rom:matrix(0 to 2**depth-1);

procedure load_rom (signal data_word:out matrix)is

file romfile:text open read_mode is "romfile.dat";

variable lbuf:line;

variable i:integer:=0;

variable fdata:std_logic_vector(7 downto 0);

begin

while(not endfile(romfile)and i<2**depth)loop

readline(romfile,lbuf);

read(lbuf,fdata);

data_word(i)<=fdata;

i:=i+1;

end loop;

end procedure;

begin

load_rom(rom);

process(clk_ROM)

begin

if(clk_ROM='1'and clk_ROM'event)then

if(ROM_EN='0'and M_ROM='1')then

DATA_BUS<=rom(conv_integer(addr));

else DATA_BUS<=(others=>'Z');

end if;

end if;

end process;

end Behavioral;

testbench:

----------------------------------------------------------------------------------

-- Engineer: switch_swq

-- Create Date: 2024/04/18 13:02:24

----------------------------------------------------------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity ROM_tb is

-- Port ( );

end ROM_tb;

architecture Behavioral of ROM_tb is

component ROM

generic(

depth:positive:=12;

width:positive:=8

);

Port (

clk_ROM,M_ROM,ROM_EN:in std_logic;

addr:in std_logic_vector(11 downto 0);

DATA_BUS:inout std_logic_vector(7 downto 0)

);

end component;

signal rst:std_logic;

signal clk_ROM,M_ROM,ROM_EN:std_logic;

signal addr:std_logic_vector(11 downto 0);

signal DATA_BUS:std_logic_vector(7 downto 0);

begin

ROM_inst:ROM generic map(12,8)port map(clk_ROM,M_ROM,ROM_EN,addr,DATA_BUS);

clock:process

begin

clk_ROM<='1';

wait for 5ns;

clk_ROM<='0';

wait for 5ns;

end process;

test:process

begin

M_ROM<='0';

ROM_EN<='1';

addr<=(others=>'0');

wait for 25ns;

M_ROM<='1';

wait for 25ns;

ROM_EN<='0';

wait for 5ns;

addr<="000000000000";

wait for 20ns;

wait for 5ns;

addr<="000000000001";

wait for 20ns;

wait for 5ns;

addr<="000000000010";

wait for 20ns;

wait for 5ns;

addr<="000000000011";

wait for 20ns;

wait;

end process;

end Behavioral;