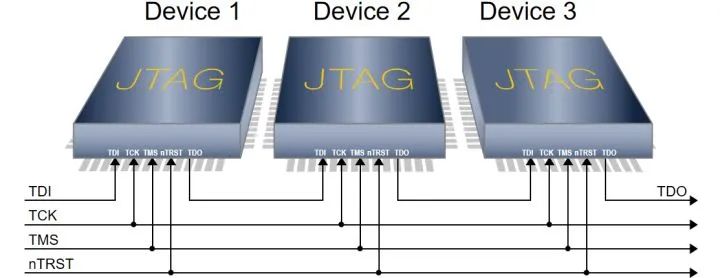

我们控制JTAG设备(无论是 FPGA 还是微处理器)内部的方式是使用测试访问端口TAP,它由四个主要信号组成:测试数据输入TDI、测试数据输出TDO、测试时钟TCK,测试模式选择TMS。

在特定情况下,还有一个测试复位信号,这用于保持设备处于复位状态以停止激活。

图1

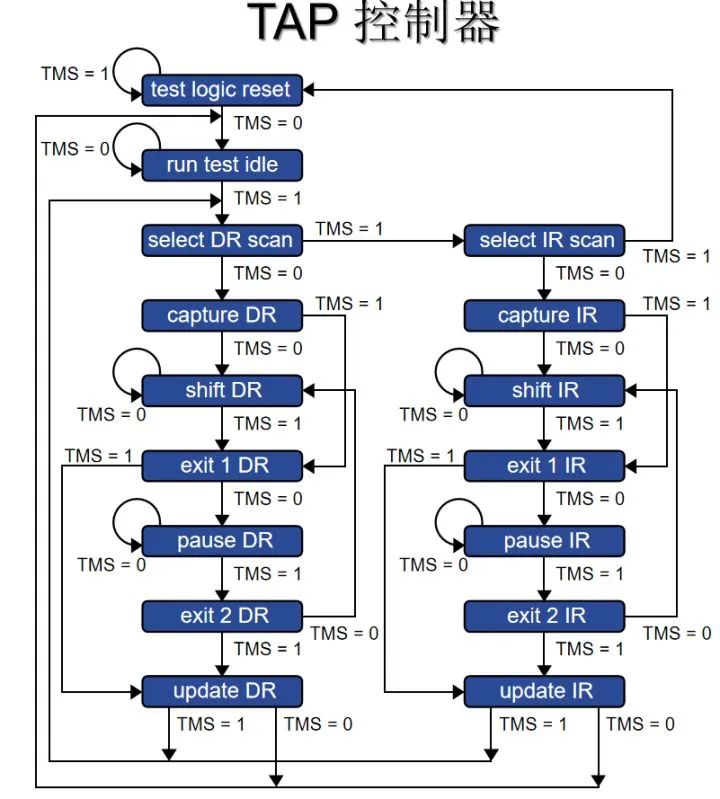

设备内部的 TAP 端口控制着这些信号,如下图

图2

从图2中能看到有两条主要路线通过此 TAP端口。TAP 端口中不同状态之间的转换由应用 TCK 时 TMS 引脚的状态控制。

因此,如果 TMS 引脚为高电平,您可以从一种状态转换到另一种状态,如果 TCK 发生时它为低电平,它将进入不同的状态。

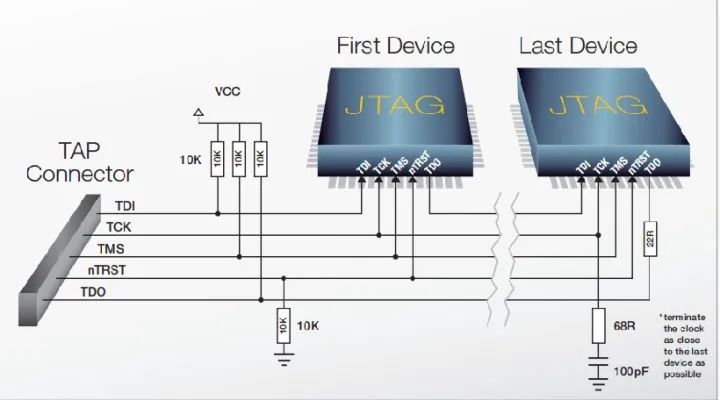

图3

TAP端口还可以访问设备内部与电路板测试无关的功能。

芯片供应商可以使用该端口连接到其他寄存器,这些寄存器可用于诸如 FPGA 或 CPLD 编程、访问调试器、设置断点和监控处理器中的数值等功能,有时实际上是对处理器中的内部闪存进行编程 ,但有时也可以通过访问设备内部的嵌入式仪器将其用作测试制度的一部分。

对于许多 FPGA,可以监控核心温度和内核在任何特定时间点的功耗。

使用 TAP 端口向设备发出指令,该指令将选择一个数据寄存器,然后您从该寄存器中读取数据或将数据放入以控制设备内部发生的情况。

所以,XJTAG测试电路板的原理,就是将受测器件(DUT)返回的数据与构建该板的设计进行比较。

406

406

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?