1.UVM phase 概览

UVM采用phase机制来自动化运行testbench各个仿真过程。UVM phase支持显示或隐式的同步方案,运行过程中的线程控制和跳转。用户只要把代码填入对应的phase,这些代码就会自动在正确的时间执行。各个phase执行顺序如下图所示:

相较于OVM,UVM新增了12个小的task phase,如下图:

其中run_phase和uvm新增加的12个小phase是并行执行的。

2 按是否消耗仿真时间,所有phase可以分成两大类

<1> function phase:不消耗仿真时间,而其也可分成两大类:

a. 继承自uvm_bottomup_phase, 在UVM component树中,自下而上的执行, 如connect_phase

b. 继承自uvm_topdown_phase, 在UVM component树中,自上而下执行, 如build_phase

<2> task phase:消耗仿真时间的,也称动态运行(run-time)phase.

下图是各个phase的继承关系,从中可以看出

自上而下(top-down) function phase:build和final phase。

自下而上(bottom-up)f unction phase: connect, end_of_elaboration,start_of_simulation, extract, check, report。

task phase: run_phase以及其他12个小phase: pre_reset, reset_phase, post_reset, pre_configure, configure, post_configure,

pre_main, main, post_main, pre_shutdown, shutdown, post_shutdown, 如下图:

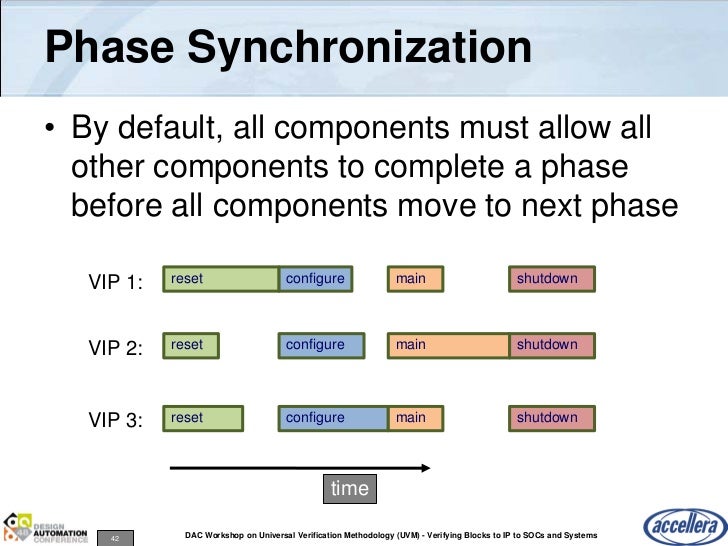

3 task phase的同步

一个UVM验证平台有许多component组成,每个component都有自己的run_phase,以及从pre_reset 到post_shuddown的12个小phase。只有所有component的一个小task phase 完成,整个仿真平台才开始下一个小task phase的执行。 各个component的run_phase之间,以及run_phase于最后一个小phase--post_shutdown_phase之间,都有这样的同步。

4. super.xxx_phase

除了super.build_phase,其他super.xxx_phase几乎没做任何事情,因此,除了build_phase,其他phase可不必加super.xxx_phase.

在super.build_phase中,主要完成自动获取config_db中参数的功能,如果自定义的component无需获取任何参数,也可省略。

5. phase的跳转

默认情况下各phase是从上到下按时间顺序执行,但可以自定义做必要的跳转,如在main_phase执行过程中,突然遇到reset信号被置起,可以用jump()实现从mian_phase到reset_phase的跳转:

phase.jump(uvm_reset_phase::get())

task my_driver::main_phase(uvm_phase phase);

`uvm_info("driver", "main phase", UVM_LOW)

fork

while(1) begin

seq_item_port.get_next_item(req);

drive_one_pkt(req);

seq_item_port.item_done();

end

begin

@(negedge vif.rst_n);

phase.jump(uvm_reset_phase::get());

end

join

endtask跳转的限制

不能跳转到build到start_of_function的function phase, 也不能跳转到run_phase. 从pre_reset_phase后的所有phase都可以作为jump()的参数。 除了向前跳转,也可向后跳转。除了向run-time phase跳转,甚至可以向final_phase等function phase跳转。

phase的调试

- 在命令行加UVM_PHASE_TRACE,可以将进入和退出个phase的信息打印到log中。

<sim command> +UVM_PHASE_TRACE

- 在指定phase设置verbosity:

<sim command> +uvm_set_verbosity=<comp>,<id>,<verbosity>,<phase>

例如:simv +uvm_set_verbosity=uvm_test_top.env.mdl,my_model,UVM_NONE,main +UVM_TESTNAME=my_case0 +UVM_PHASE_TRACE -l tmp.log

注意,其中参数<phase> 不需要phase后缀,如上面例子将uvm_test_top.env.mdl的main_phase中打印的信息屏蔽掉,命令行里用的是+uvm_set_verbosity=uvm_test_top.env.mdl,my_model,UVM_NONE,main 。

- 设置timeout时间

1. 通过命令行:<sim command> +UVM_TIMEOUT=<timeout>,<overridable>

如<sim command> +UVM_TIMEOUT="300ns, YES"

2.通过在base test中使用set_timeout(): uvm_top.set_timeout(500ns,0);

必要时需要修改宏定义:`define UVM_DEFAULT_TIMEOUT 9200s

参考:

UVM实战(卷1) (张强 著)

UVM Phasing page from www.learnuvmverification.com

本文介绍了UVM phase机制,它能自动化运行testbench仿真过程,支持同步、线程控制和跳转。按是否消耗仿真时间,phase分为function phase和task phase。还阐述了task phase的同步、super.xxx_phase的使用、phase的跳转规则及调试方法,如命令行加参数等。

本文介绍了UVM phase机制,它能自动化运行testbench仿真过程,支持同步、线程控制和跳转。按是否消耗仿真时间,phase分为function phase和task phase。还阐述了task phase的同步、super.xxx_phase的使用、phase的跳转规则及调试方法,如命令行加参数等。

994

994

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?