这期我们继续探讨了解一下LDMOS的缺点:

LDMOS 截断时可耐较高电压,导通时具有较低阻抗,开关速度快,与CMOS工艺能良好兼容等优点使其在BCD 工艺中得到广泛应用。但随着开发的电源管理芯片设计中,由于应用的关系,将LDNMOS 大面积的集成在同一个版图上的结构具有天生缺陷。

首先我们了解下 BUCK 电路的工作原理。

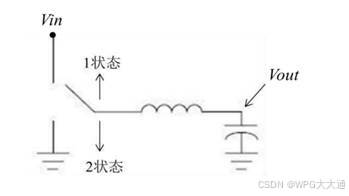

如图1所示,在BUCK 电路中,电感一端接到直流输出电压 Vout,另外一端通过开关切换连接到输入电压 Vin 或零电位 GND上。现在考虑一下在不同开关状态下电感电流的变化情况:在1状态,电感一端接入输入电压 Vin,另一端接到输出电压 Vout。对于一个 BUCK 电路,输入电压必须高于输出电压,因此电感上形成正向压降(由左至右);反之,在2状态下,电感接输入电压的一端被重置到接地,此时输出电压端必然为正端,则电感上形成负向压降。

当电感电压为正向时,电感电流就会增加;当电感电压负向时电感电流就会减少并最终反向流动。

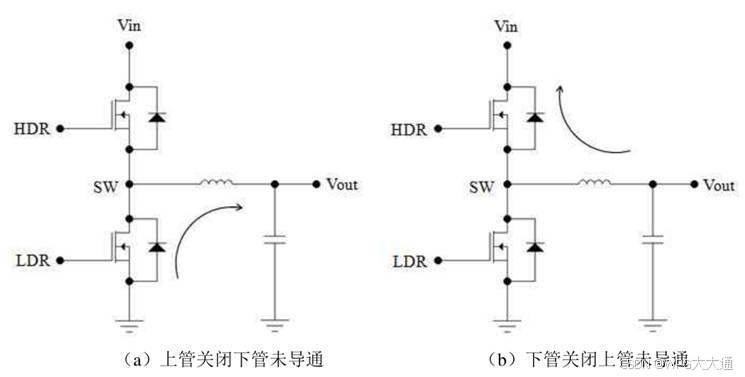

芯片中BUCK电路的开关管即由2个内置 LDNMOS 组成,上管开通下管关闭后,电感电压正向,电感激磁,电流从 Vin 经过SW 流向电感,向电容充电,当上管关断下管仍未打开的时段(死区时间),由于电感电流不能瞬变,下管的体二极管正向导通续流使得电感正向电流得以维持,此时SW电位比地电位低一个 PN结正向压降(-0.7V);下管导通后,电感电压由左至右负向,电感正向电流减小并最终形成负向电流,当下管关断上管仍未打开的时段,电感电流不能瞬变,只能通过上管的体二极管流向输入电压Vin 端,此时SW 电位比 Vin 电位高一个 PN结正向压降(+0.7V)。

经过以上分析得到一个重要的信息,即芯片工作时随着上、下管的交替开关,在SW 节点会出现高于输入电源电压和低于地电位的情况,从而导致部分PN结在某些时间段导通。

LDNMOS 的寄生PNP管在电路工作时随上下管的开启周期性导通,通过垂直方向的寄生PNP 对衬底注入大量载流子形成噪声,干扰了模拟部分电路的精度,使基准电压波动超出许可范围。而版图绘制只能改变横向结构和尺寸,并无法影响此纵向寄生 NPN结构;理论上可以调节工艺条件,譬如在 LDNMOS 下做高掺杂 NBL 埋层,减小寄生 BJT 的Beta值,但要求工厂改变工艺会带来高昂成本。据此看来如需继续集成LDNMOS,这会是一个后端无法解决的问题。

NOVATEK的PMIC有很好的抗干扰能力,尤其在EMI测试时表现良好。

Q&A:

1、 Q:LDMOS在截断时的特性是什么?

A: LDMOS 截断时可耐较高电压,导通时具有较低阻抗,开关速度快。

2、 Q:BUCK电路中电感处于什么状态?

A:输入电压必须高于输出电压,因此电感上形成正向压降,反之则形成反向压降。

3、 Q:芯片工作时,LDMOS处于什么状态?

A:芯片工作时随着上、下管的交替开关,在SW 节点会出现高于输入电源电压和低于地电位的情况,从而导致部分PN结在某些时间段导通。

4、 Q:PN结的导通有什么危害?

A:LDNMOS 的寄生PNP管在电路工作时随上下管的开启周期性导通,通过垂直方向的寄生PNP 对衬底注入大量载流子形成噪声,干扰了模拟部分电路的精度。

5、 Q:工厂设计时,用什么方法规避上述问题?

A:调节工艺条件,譬如在 LDNMOS 下做高掺杂 NBL 埋层,减小寄生 BJT 的Beta值,但要求工厂改变工艺会带来高昂成本 。

更多PMIC系列博文可在大大通观看,大胆点开链接前往吧!

4374

4374

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?