项目场景:

Altium Designer 22.7.1

问题描述

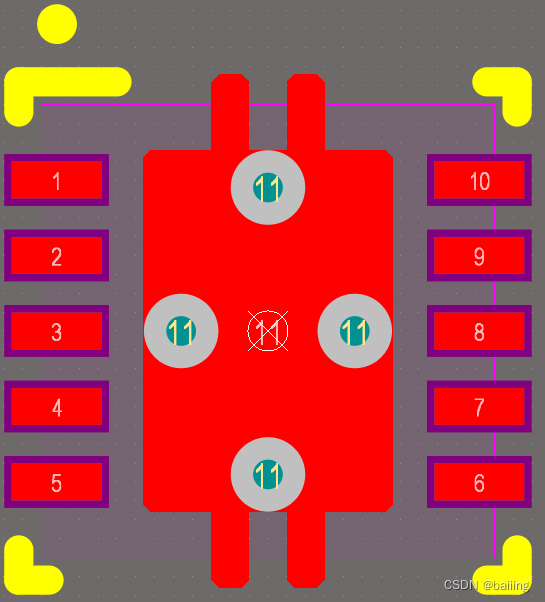

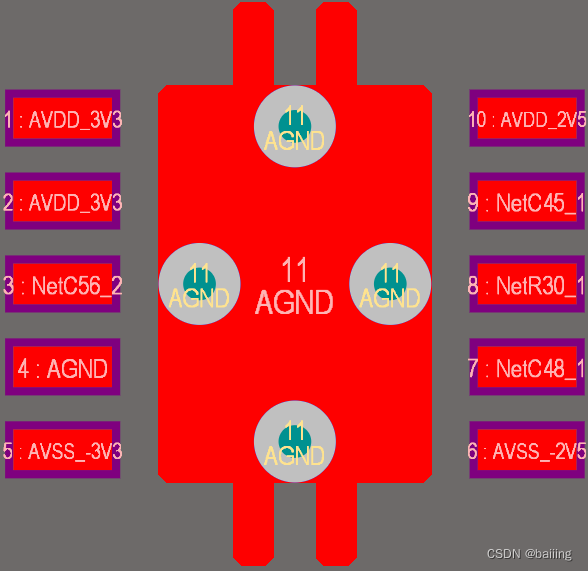

从TI官网使用Ultra Librarian转换封装到AD中。有些器件会有不规则形状焊盘,例如TPS7A39,其中不规则焊盘为UL软件自动创建的Solid Region对象,无法赋予引脚标号及网络,如下图所示。

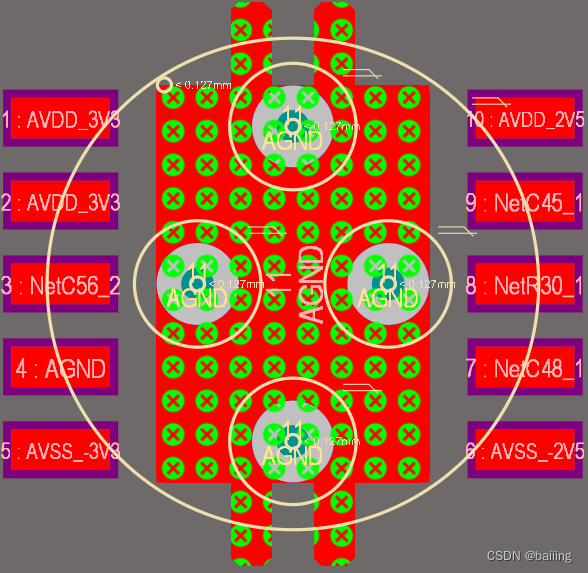

在将封装导入PCB中后,会有如下报错。

Clearance Constraint: (Collision < 0.127mm) Between Pad on Multi-Layer And Region Bottom Layer

Short-Circuit Constraint: Between Pad on Multi-Layer And Region Bottom Layer Location

原因分析:

根据在互联网中检索的信息可知,这是AD软件的BUG。

具体原因:具有引脚数字的Pad尺寸太大,而AD无法自动将其下的Solid Region识别为同一个Pad,导致错误。

解决方案:

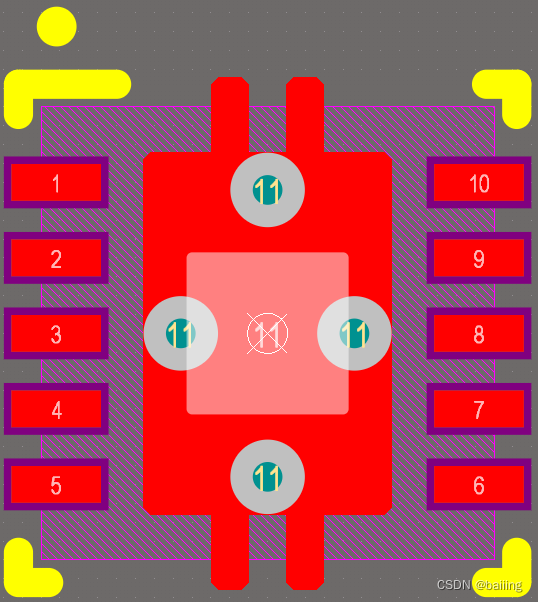

修改Solid Region中焊盘的尺寸,将尺寸修改小之后,DRC的错误自动消失。

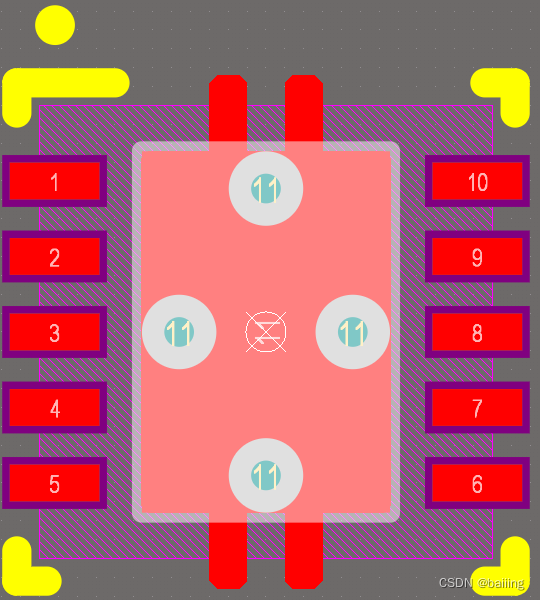

例如:将默认焊盘尺寸

修改为

(其中周围红色的区域为Solid Region区域)

最后使用 Design → Import Changes From *** 更新PCB中的元器件封装。

问题解决了。

参考:

Altium - Custom pads creating short circuit violation - Page 1 (eevblog.com)

3827

3827

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?