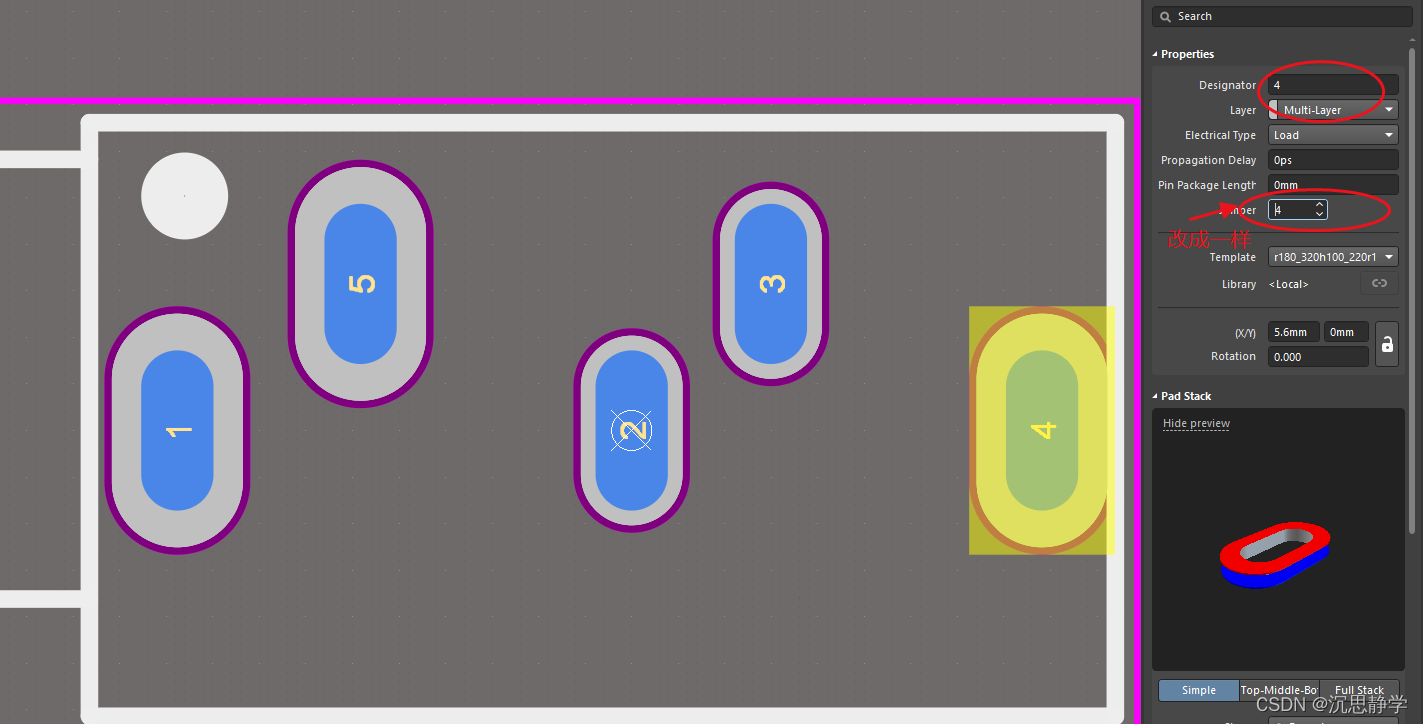

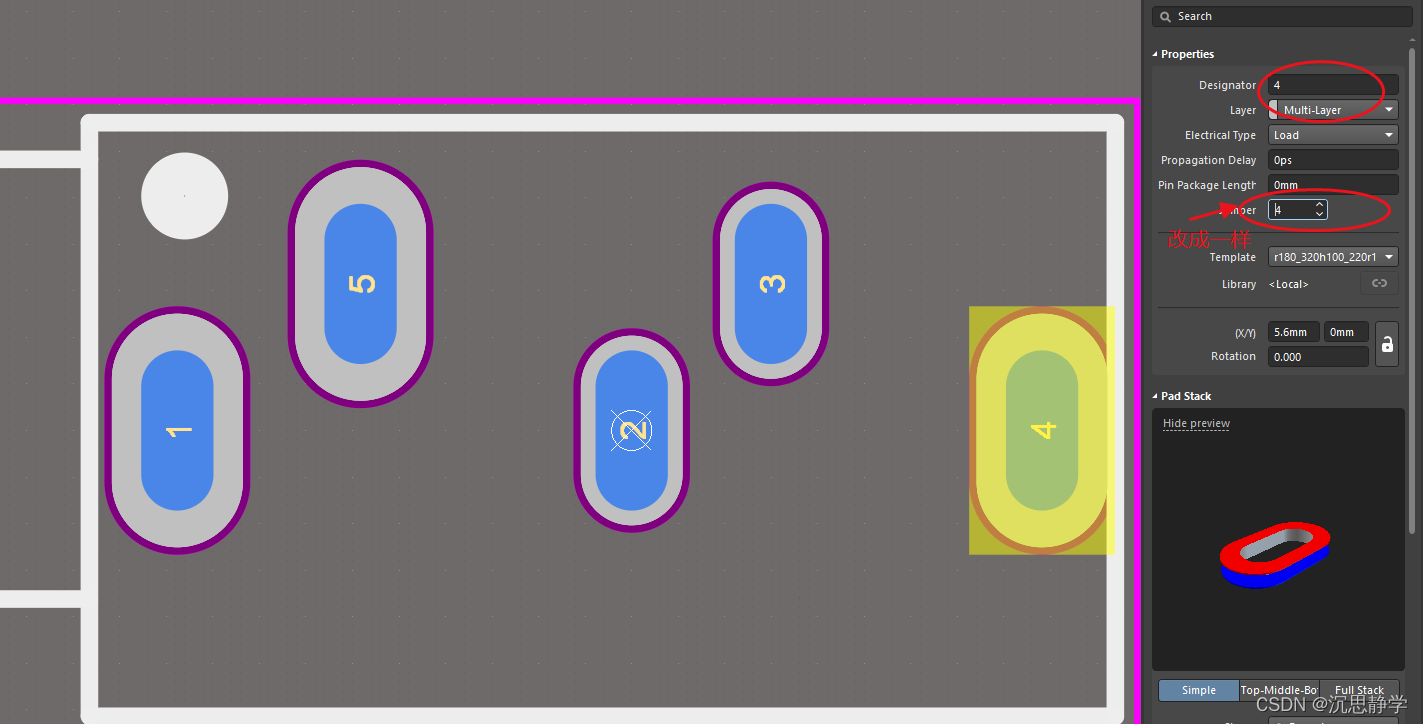

Short-Circuit Constraint: Between Pad J3-4(5549.469mil,574.842mil) on Multi-Layer And Pad J3-5(5915.611mil,496.102mil) on Multi-Layer Pads have the same JumperID: 1 but different Nets: (No Net) and NetD12_2

Short-Circuit Constraint: Between Pad J3-4(5549.469mil,574.842mil) on Multi-Layer And Pad J3-5(5915.611mil,496.102mil) on Multi-Layer Pads have the same JumperID: 1 but different Nets: (No Net) and NetD12_2

1万+

1万+

2万+

2万+

4412

4412

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?