名称:8位流水灯设计Verilog代码Quartus仿真(文末获取)

软件:Quartus

语言:Verilog

代码功能:

8位流水灯设计要求:

1.设计能带8个LED发光管发光,并按照要求轮流发光,产生流水灯的流动效果。

2.应具有5种以上不同风格的流动闪亮效果。

3.有起动、停止控制键。

4.有流动闪亮效果选择设置键,流动风格分手动选择和自动循环两种模式

流水灯设计报告

1. EDA简介

EDA是Electronic design automation的缩写,意为电子设计自动化。EDA技术是以计算机为工具,设计者在EDA软件平台上,融合应用电子技术、计算机技术、信息处理及智能化技术的最新成果,进行电子产品的自动设计。EDA技术的出现,极大地提高了电路设计的效率和可操作性。

利用EDA工具,电子设计师可以从概念、算法、协议等开始设计电子系统,大量工作可以通过计算机完成,并可以将电子产品从电路设计、性能分析到设计出IC版图或PCB版图的整个过程的计算机上自动处理完成。随着集成电路规模越来越大,EDA的应用不仅仅限于布线和数值仿真,高层次的数字设计又催生了硬件描述语言Verilog和VHDL。在本设计中,我们使用的EDA软件为QuartusII,使用的硬件描述语言为Verilog。Quartus II 是Altera公司推出的综合性CPLD/FPGA开发软件,软件支持原理图、VHDL、VerilogHDL等多种设计输入形式,内嵌自有的综合器以及仿真器,可以完成从设计输入到硬件配置的完整PLD设计流程。

2. 流水灯功能

流水灯指一组灯在控制系统的控制下按照设定的顺序和时间来发亮和熄灭,形成一定的视觉效果。本设计的流水灯功能为:使用8个LED发光,并按照要求轮流发光,产生流水灯的流动效果;流水灯具有5种以上不同风格的流动闪亮效果;有起动、停止控制键;有流动闪亮效果选择设置键,流动风格分手动选择和自动循环两种模式。

3. LED简介

发光二极管,简称为LED,是一种常用的发光器件,通过电子与空穴复合释放能量发光。发光二极管与普通二极管一样是由一个PN结组成,也具有单向导电性。当给发光二极管加上正向电压后,从P区注入到N区的空穴和由N区注入到P区的电子,在PN结附近数微米内分别与N区的电子和P区的空穴复合,产生自发辐射的荧光。不同的半导体材料中电子和空穴所处的能量状态不同。当电子和空穴复合时释放出的能量多少不同,释放出的能量越多,则发出的光的波长越短。常用的是发红光、绿光或黄光的二极管。发光二极管可高效地将电能转化为光能,在现代社会具有广泛的用途,如照明、平板显示、医疗器件等。

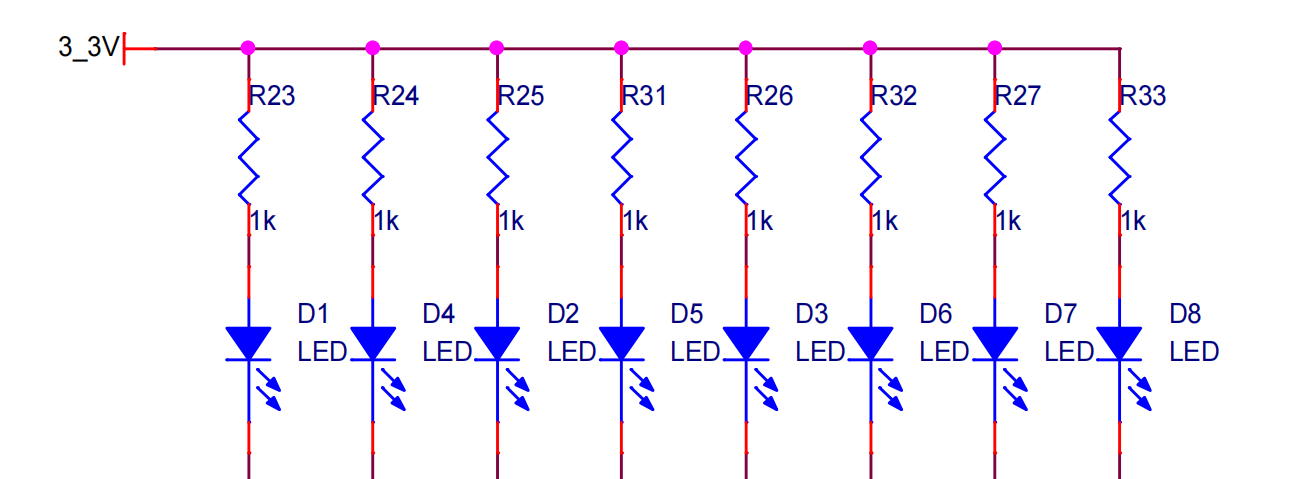

4. LED的硬件电路设计

下图为LED的电路设计,一共8个LED,采用共阳极设计,LED的阴极接FPGA芯片,阳极通过一个1K欧姆的电阻连接到3.3V的电源上,电阻的作用是限流,防止流经LED的电流过大将LED损坏。当FPGA接口输出低电平时,LED导通,灯亮,当FPGA输出高电平时,LED灯灭。

5. 程序设计

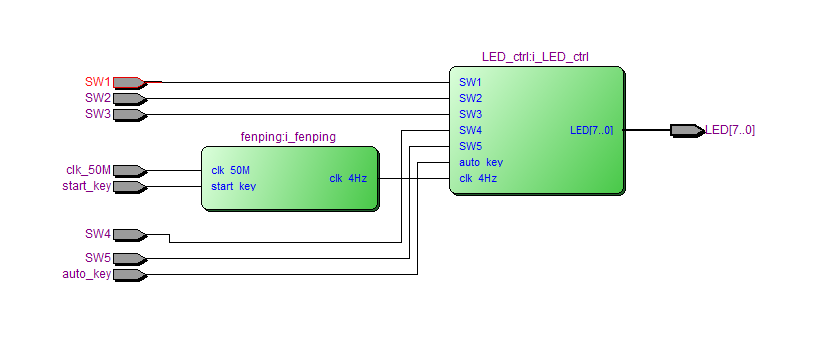

根据功能要求,代码分为2个模块设计,一个是分频模块,一个是LED控制模块。分频模块实现将系统时钟50MHz分频到4Hz的功能。LED控制模块实现流水灯控制的功能,其中LED控制模块的时钟来源于分频模块输出的4Hz。两个模块连接图如下所示:

上图中,fenping为分频模块,LED_ctrl为LED控制模块,左侧灰色箭头为系统输入信号。右侧灰色箭头为LED输出信号。

分频模块使用系统时钟50M,通过计数进行分频,50MHz计数6250000后信号翻转一次,就可以得到4Hz信号,具体代码如下:

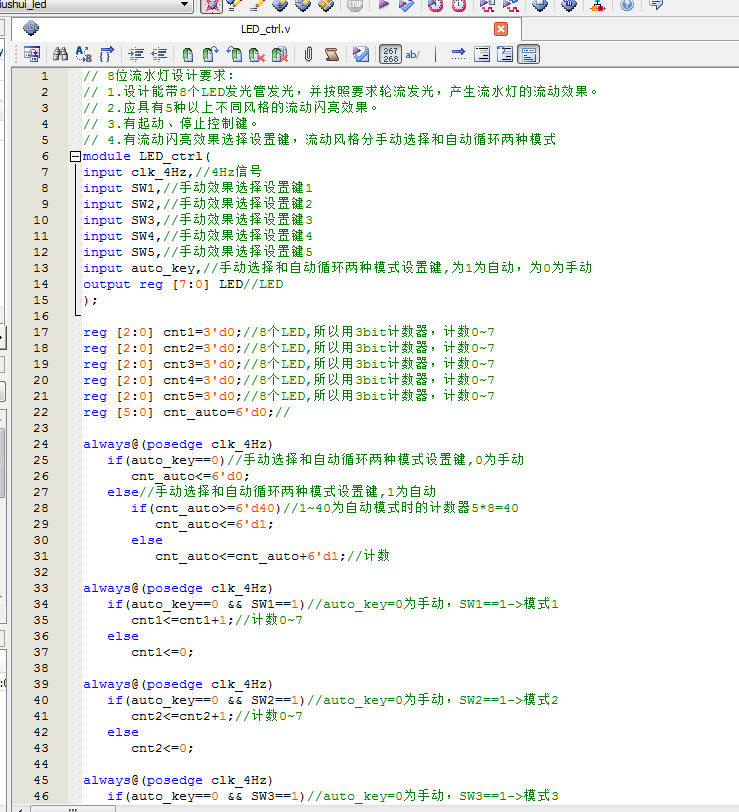

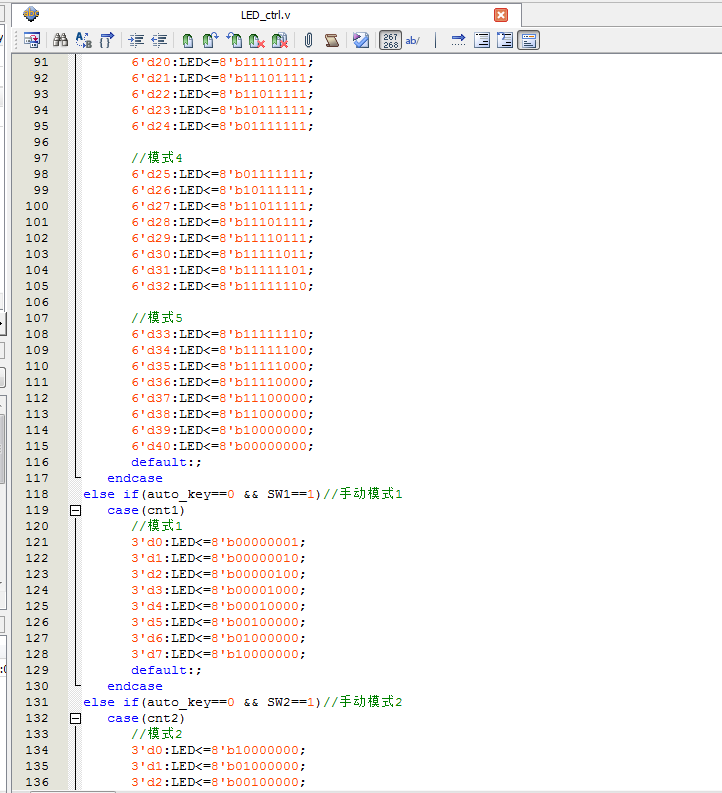

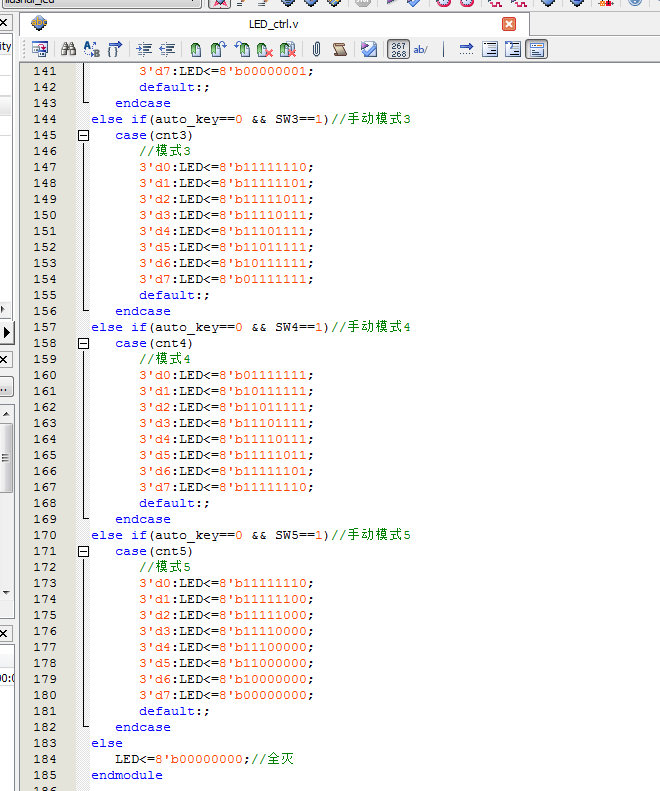

LED控制模块完成LED的主要控制功能,首先设计一个计数器,计数1~40,这是因为8个LED灯,一共5种不同模式,因此计数40,作为自动控制时的计数信号。然后再通过5个拨码开关(SW1~SW5)分别控制5个不同的计数器,作为手动控制时的计数信号。LED手动或者自动控制通过auto_key按键切换。最后根据计数值控制每个模式下LED的变化方式即可。具体代码如下:

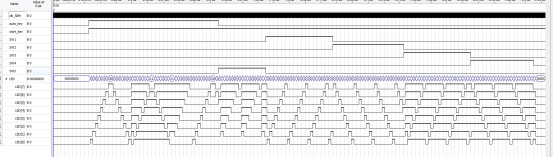

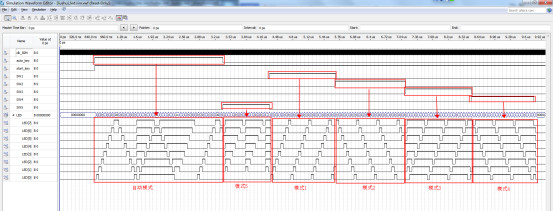

程序编译无误后新建WVF仿真文件进行仿真,仿真图如下所示:

上图可以看到,自动和手动模式切换功能正确,5种流水灯模式变化正确。因此流水灯功能正确。

6. 总结

通过这次LED流水灯设计,我掌握了QuartusII软件的基本功能,学会了在QuartusII软件下进行Verilog代码编写、调试和仿真的过程。并且通过这次实验,我也更加了解了Verilog代码的设计方法,对语法有了更深入的了解。当然,我也知道我设计的这个LED流水灯功能比较简单,在实际工程设计中,功能远远比这个复杂,我还要多多学习软件的使用的代码的设计方法,为今后的学习和工作打下基础。

部分代码展示:

// 8位流水灯设计要求: // 1.设计能带8个LED发光管发光,并按照要求轮流发光,产生流水灯的流动效果。 // 2.应具有5种以上不同风格的流动闪亮效果。 // 3.有起动、停止控制键。 // 4.有流动闪亮效果选择设置键,流动风格分手动选择和自动循环两种模式 module liushui_led( input clk_50M,//50M信号 input start_key,//起动、停止控制键 input SW1,//手动效果选择设置键1 input SW2,//手动效果选择设置键2 input SW3,//手动效果选择设置键3 input SW4,//手动效果选择设置键4 input SW5,//手动效果选择设置键5 input auto_key,//手动选择和自动循环两种模式设置键,为1为自动,为0为手动 output [7:0] LED//LED ); wire clk_4Hz;//4Hz //分频模块,50MHz分频到4Hz fenping i_fenping( . clk_50M(clk_50M), . start_key(start_key),//起动、停止控制键 . clk_4Hz(clk_4Hz) );

源代码

扫描文章末尾的公众号二维码

本文介绍了如何使用Verilog语言在QuartusII软件中设计一个8位流水灯,包括LED控制、多种闪亮模式、启动/停止控制和手动/自动模式选择。作者通过详细步骤展示了设计过程、代码实现和仿真结果,强调了EDA技术和硬件描述语言在现代电子设计中的应用。

本文介绍了如何使用Verilog语言在QuartusII软件中设计一个8位流水灯,包括LED控制、多种闪亮模式、启动/停止控制和手动/自动模式选择。作者通过详细步骤展示了设计过程、代码实现和仿真结果,强调了EDA技术和硬件描述语言在现代电子设计中的应用。

1835

1835

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?