名称:八位数码管动态显示控制电路设计VHDL代码Quartus 开发板(文末获取)

软件:Quartus

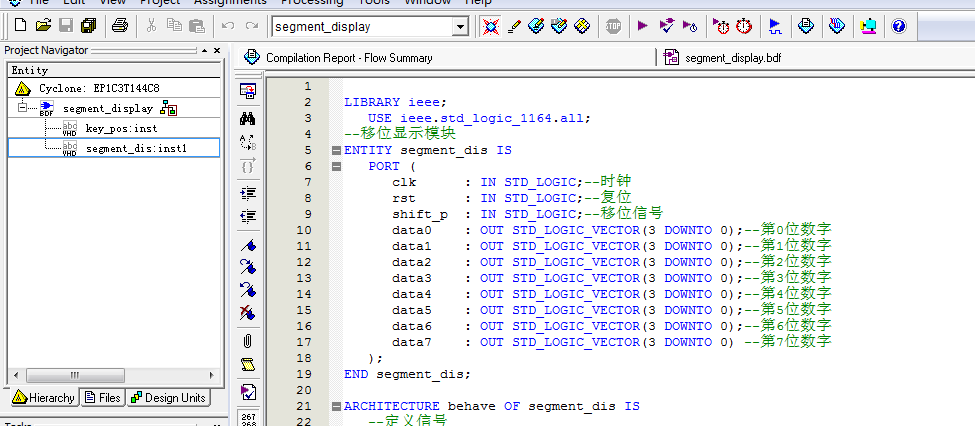

语言:VHDL

代码功能:

设计内容

运用EDA技术,设计一个八位数码管动态显示控制电路。该控制器

能够按照控制要求进行显示

主要任务:

(1)·确定总体方案

(2)运用EDA技术完成各模块的软件设计,运用所学的电路及电子技

术知识完成硬件模块设计仿真

(3)完成全部流程:设计规范文档、模块设计、代码输入、功能仿真、约束与综合、布局布线、时序仿真、下载验证等

拟达到的要求:

(1)恰当地运用所学理论知识,对总体方案进行必要的技术、经济比较,然后选定较佳的设计方案

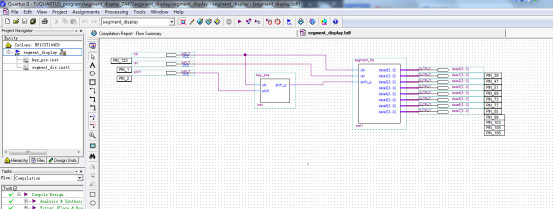

(2)编写各模块VDL源程序,绘制原理框图、顶层电路模块划分图

系统总原理图电路图、流程图釆用规范的标准绘制,要求设计参数正确布局合理。

技术指标

1、数码管为8个共阴数码管组成,初始值设置为20221903

2、设置一个左移按键,每按一次左移按钮(KEY)数码管显示的内容

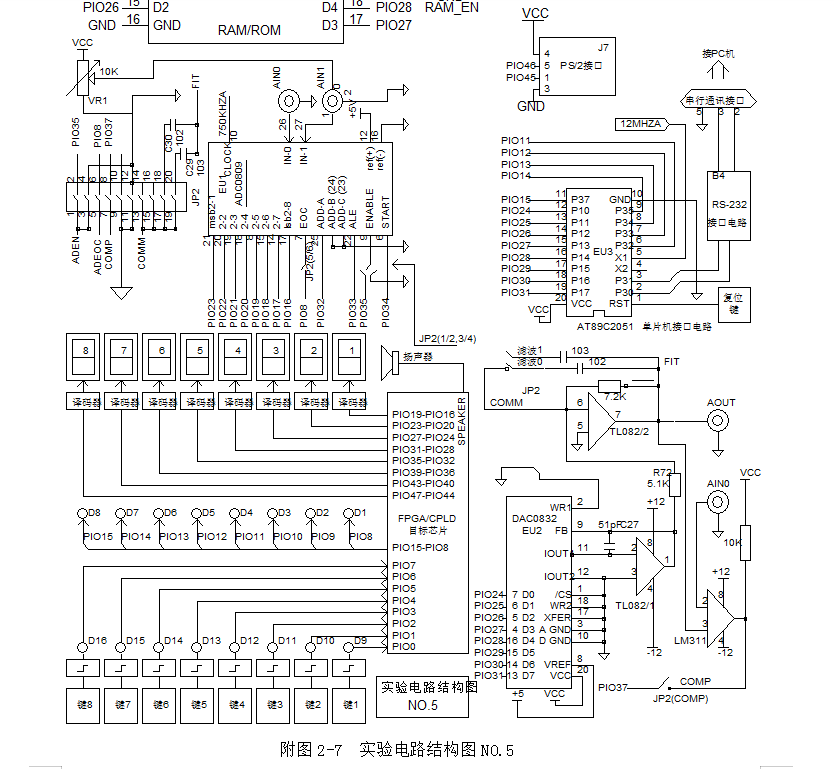

本代码已在开发板验证,开发板如下,其他开发板可以修改管脚适配:

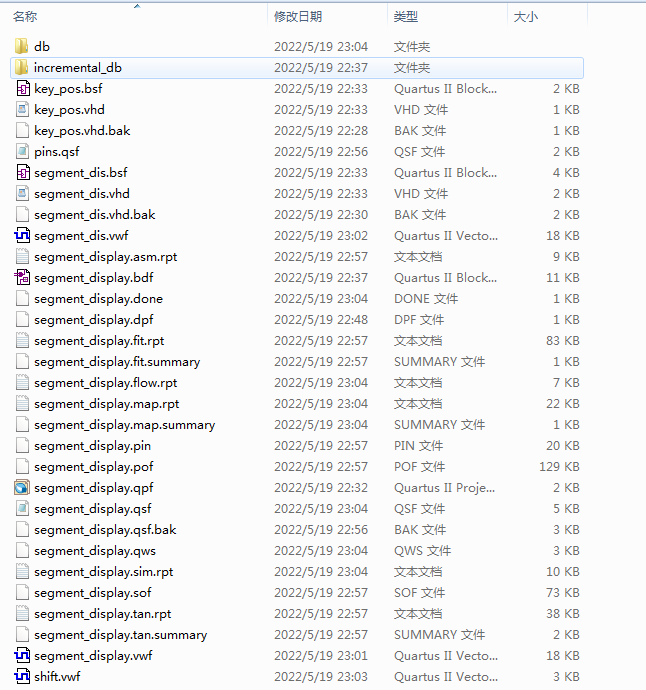

1. 工程文件

2. 程序文件

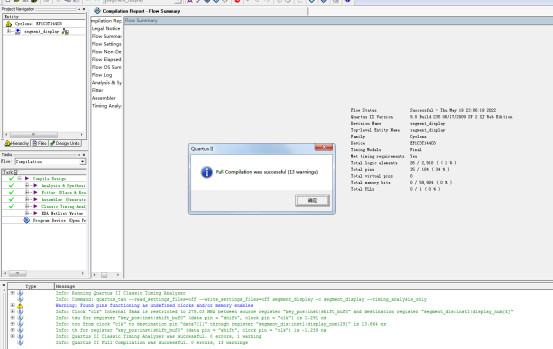

3. 程序编译

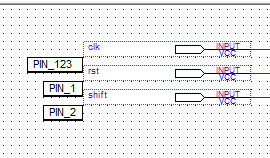

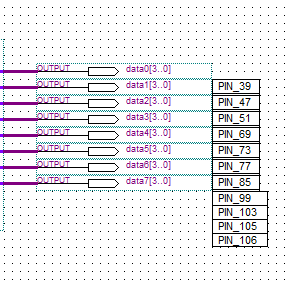

4. 管脚分配

5. 仿真图

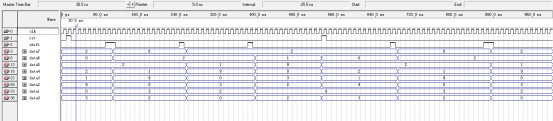

整体仿真图

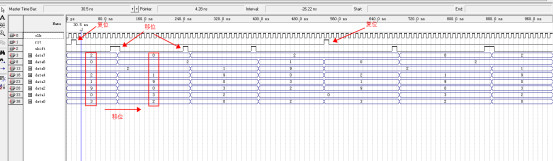

按键检测模块

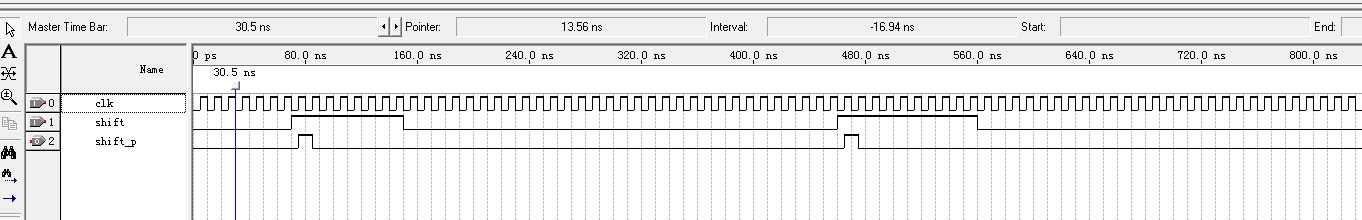

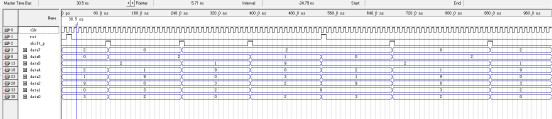

移位显示模块

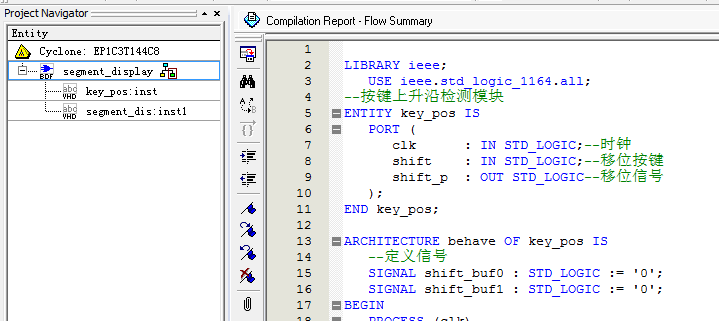

部分代码展示:

LIBRARY ieee; USE ieee.std_logic_1164.all; --移位显示模块 ENTITY segment_dis IS PORT ( clk : IN STD_LOGIC;--时钟 rst : IN STD_LOGIC;--复位 shift_p : IN STD_LOGIC;--移位信号 data0 : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);--第0位数字 data1 : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);--第1位数字 data2 : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);--第2位数字 data3 : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);--第3位数字 data4 : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);--第4位数字 data5 : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);--第5位数字 data6 : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);--第6位数字 data7 : OUT STD_LOGIC_VECTOR(3 DOWNTO 0) --第7位数字 ); END segment_dis; ARCHITECTURE behave OF segment_dis IS --定义信号 SIGNAL display_num : STD_LOGIC_VECTOR(31 DOWNTO 0) := x"20221903"; BEGIN PROCESS (clk, rst) BEGIN IF (rst = '1') THEN display_num <= x"20221903"; ELSIF (clk'EVENT AND clk = '1') THEN IF (shift_p = '1') THEN--移位信号 display_num <= (display_num(27 DOWNTO 0) & display_num(31 DOWNTO 28));--循环移位信号 END IF; END IF; END PROCESS; --输出8位数据 data7 <= display_num(31 DOWNTO 28); data6 <= display_num(27 DOWNTO 24); data5 <= display_num(23 DOWNTO 20); data4 <= display_num(19 DOWNTO 16); data3 <= display_num(15 DOWNTO 12); data2 <= display_num(11 DOWNTO 8); data1 <= display_num(7 DOWNTO 4); data0 <= display_num(3 DOWNTO 0);

源代码

扫描文章末尾的公众号二维码

1961

1961

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?