名称:基于FPGA的实验、并行高速ADC和高速DAC实验VHDL代码Quartus仿真 实验箱(文末获取)

软件:Quartus

语言:VHDL

代码功能:

实验、并行高速ADC和高速DAC实验

1、实验前的准备

打开实验箱开关,连接好JTAG下载线,将开发平台上的 MODUL SEL组合开关上的1、2、6、8拨上,3、4、5、7拨下,使两个共阳极数码管显示为C5,此时可选中适合本实验的模块组合(也可选择其它含有本实验模块的组合,其管脚分配请参考附录)该实验的硬件工程对应D:\ GX CIDE_SOPC\EP3C55\ projects\CIDE_C5;

2、实验目的

熟悉并行高速模数转换芯片ADC1175-50和高速数模转换芯片AD9708的使用方法

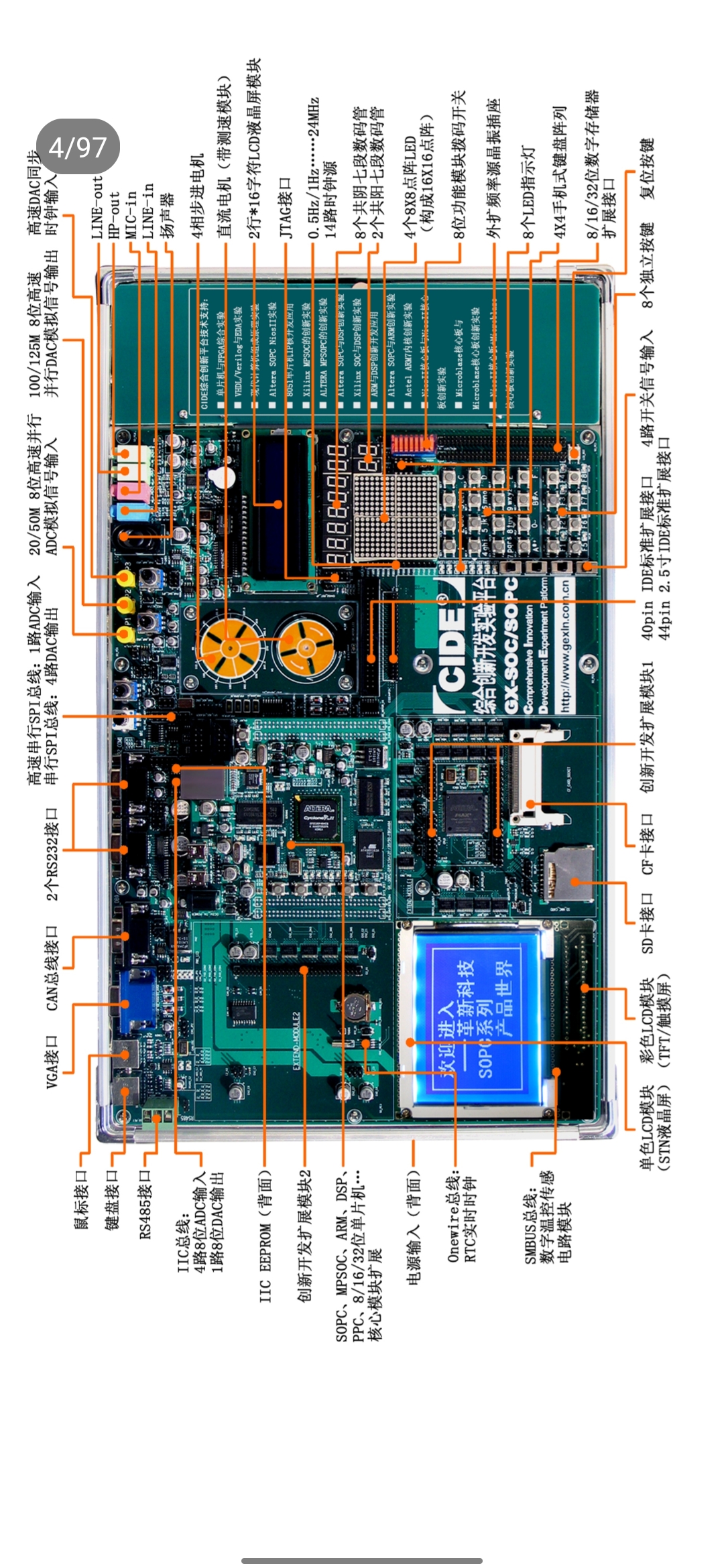

本代码已在实验箱验证,实验箱如下,其他开发板可以修改管脚适配:

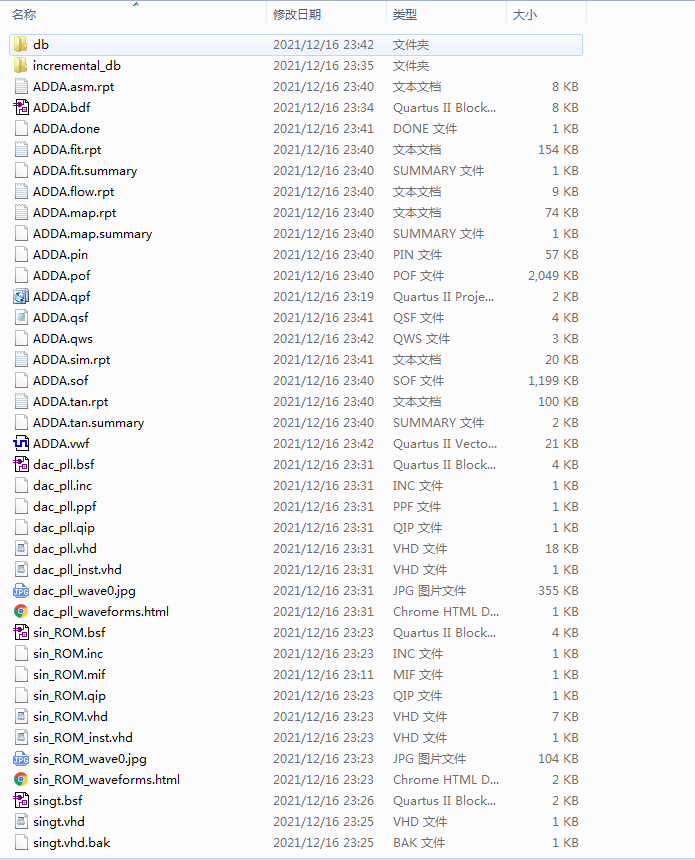

1. 工程文件

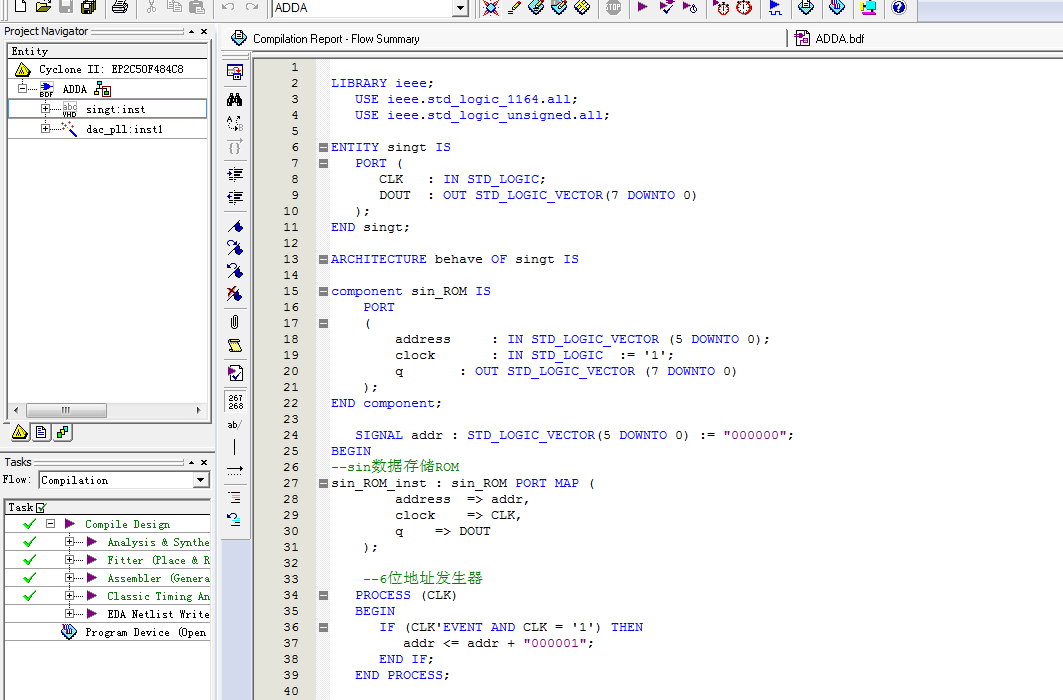

2. 程序文件

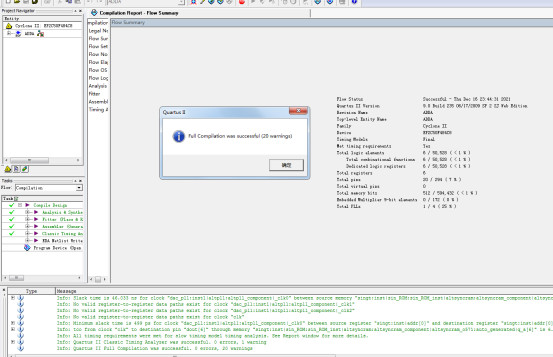

3. 程序编译

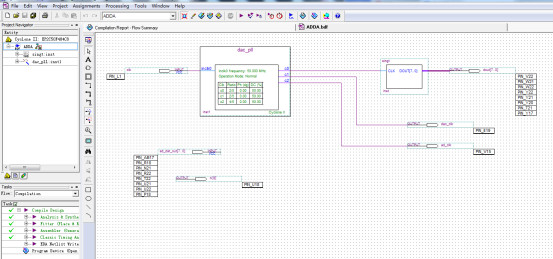

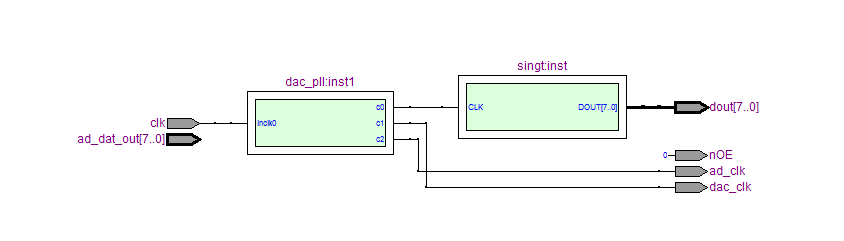

4. RTL图

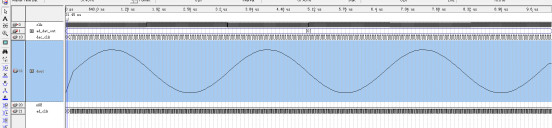

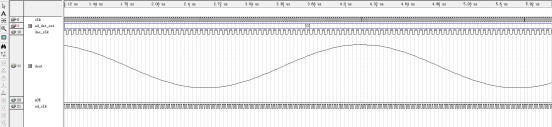

5. 仿真图

部分代码展示:

-- megafunction wizard: %ROM: 1-PORT% -- GENERATION: STANDARD -- VERSION: WM1.0 -- MODULE: altsyncram -- ============================================================ -- File Name: sin_ROM.vhd -- Megafunction Name(s): -- altsyncram -- -- Simulation Library Files(s): -- altera_mf -- ============================================================ -- ************************************************************ -- THIS IS A WIZARD-GENERATED FILE. DO NOT EDIT THIS FILE! -- -- 9.0 Build 235 06/17/2009 SP 2 SJ Web Edition -- ************************************************************ --Copyright (C) 1991-2009 Altera Corporation --Your use of Altera Corporation's design tools, logic functions --and other software and tools, and its AMPP partner logic --functions, and any output files from any of the foregoing --(including device programming or simulation files), and any --associated documentation or information are expressly subject --to the terms and conditions of the Altera Program License --Subscription Agreement, Altera MegaCore Function License --Agreement, or other applicable license agreement, including, --without limitation, that your use is for the sole purpose of --programming logic devices manufactured by Altera and sold by --Altera or its authorized distributors. Please refer to the --applicable agreement for further details. LIBRARY ieee; USE ieee.std_logic_1164.all; LIBRARY altera_mf; USE altera_mf.all; ENTITY sin_ROM IS PORT

源代码

扫描文章末尾的公众号二维码

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?