- 创建时间(setup time)是指数据在被采样时钟边沿采样到之前,需保持稳定的最小时间。

- 维持时间(hold time)是指数据在被采样时钟边沿采样到之后,需保持稳定的最小时间。

在触发器的数据手册一般会标示组件的创建时间(tsu)及维持时间(th),一般会是以奈秒(ns)为单位,有些先进的触发器可以到数百皮秒(ps)。若数据及控制输入从采样时钟边沿之前就维持定值,且时间超过创建时间,在采样时钟边沿之后也维持定值,且时间也超过维持时间,可以避免触发器的亚稳态现象。

- 时钟周期:计算机主频决定的基本时间计量单位;

- 指令周期:从取指令到执行指令完毕所需的时间;

- 总线周期:从外部存储器或端口存取一次数据所需的时间;

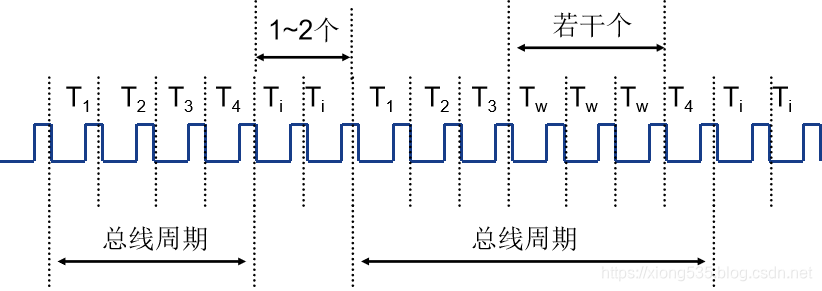

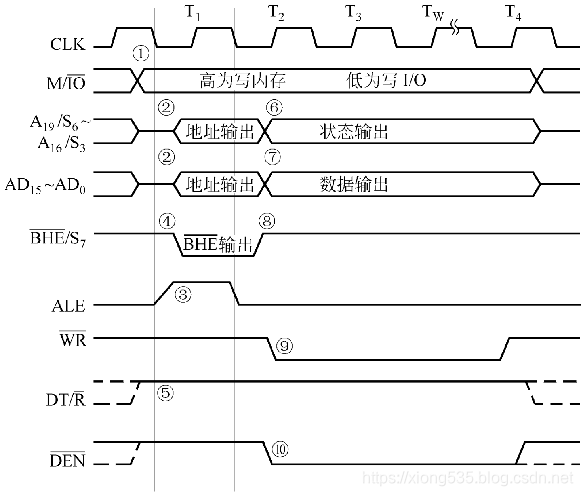

8086总线周期由4个时钟周期组成,对应总线的4个状态分别为T1、T2、T3、T4;有时会插入等待状态Tw和空闲状态Ti

- T1状态:CPU往地址/数据复用总线(AD)上发送地址信息,指出要寻址的存储单元或端口地址;

- T2状态:CPU从总线上撤销地址,而使总线的低16位成高阻状态,为传输数据做准备。总线的高4位用来输出本总线周期状态信息;

- T3状态:地址/数据复用总线上出现CPU写出或从存储器、断口读入的数据;

- T4状态:总线周期结束;

- Tw状态:对于速度较慢的外设或存储器,不能及时配合CPU传送数据,这是外设可通过”READY”信号线在T3状态启动之前向CPU发一个”数据未准备好”信号,CPU会在T3之后插入一个或多个附加的时钟周期Tw,直到外设或存储器完成数据传输时,在”READY”上发出”准备好”信号。CPU据此信号自动脱离Tw状态,进入T4状态;

- Ti状态:CPU不执行总线周期时,总线处于空闲状态;

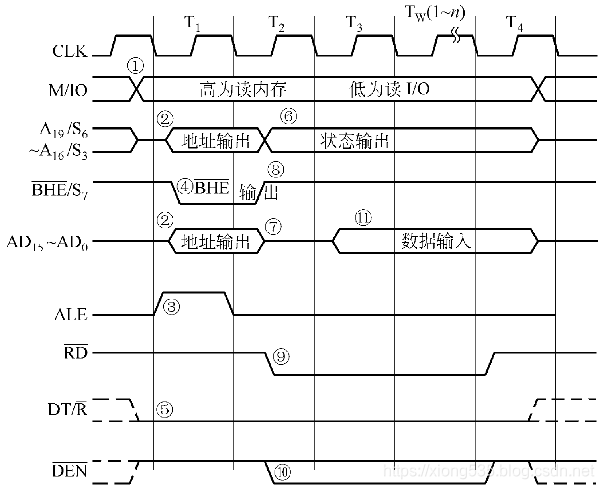

总线读操作——最小模式

-

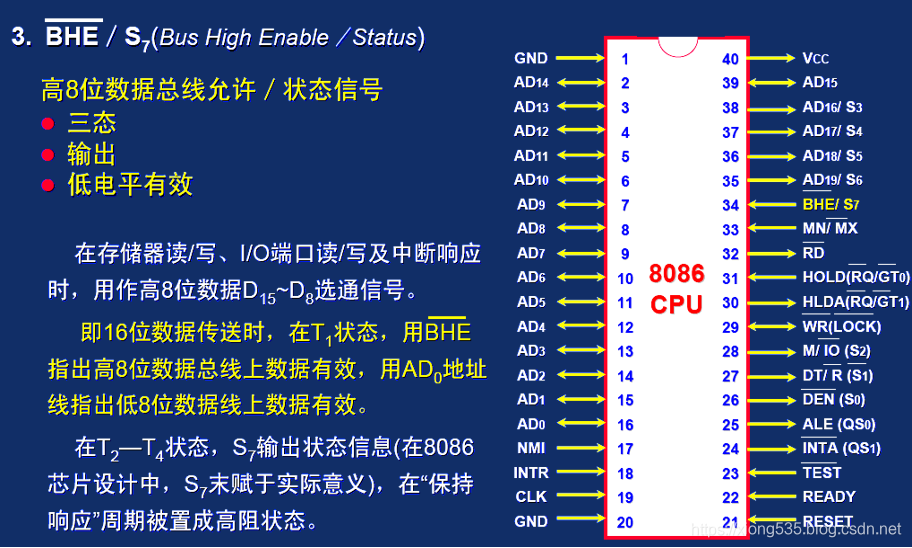

T 1 T_1 T1开始使M/IO, D T / R ‾ DT/\overline{R} DT/R有效,输出地址信号 A 19 A_{19} A19 ~ A 16 A_{16} A16、 A 15 A_{15} A15~ A 0 A_0 A0和BHE信号,ALE有效(高电平)。

-

T 1 T_1 T1上升沿,锁存地址和 B H E ‾ \overline{BHE} BHE。

-

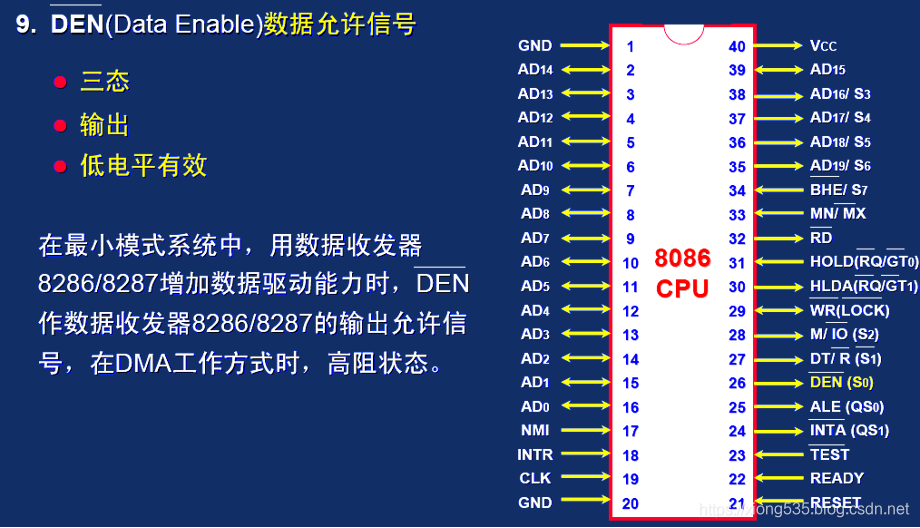

T 1 T_1 T1下降沿( T 2 T_2 T2开始)输出状态 S 3 S_3 S3~ S 6 S_6 S6, A 15 A_{15} A15~ A 0 A_0 A0浮空,BHE无效,输出 S 7 S_7 S7。RD和DEN信号有效,打开三态门读取数据。

-

T 3 T_3 T3上升沿检测READY信号,若READY为高电平,则下一个为 T 4 T_4 T4状态;否则插入等待时钟周期 T w T_w Tw 。

-

T 3 T_3 T3下降沿RD和DEN无效,数据总线浮空。

-

T 4 T_4 T4上升沿DT/R无效。

总线写操作——最小模式

-

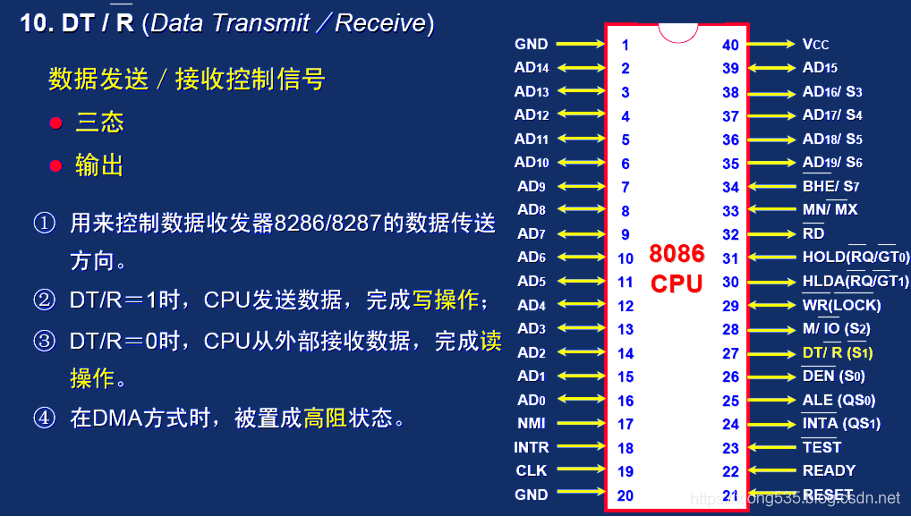

D T / R ‾ DT/\overline{R} DT/R为高电平。

-

AD15~AD0输出地址后,紧接着输出数据,T4上升沿浮空。

-

T1下降沿输出写信号WR。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?