维基百科:http://zh.wikipedia.org/wiki/%E9%94%81%E7%9B%B8%E7%8E%AF

锁相环(PLL: Phase-locked loops)是一种利用反馈(Feedback)控制原理实现的频率及相位的同步技术,其作用是将电路输出的时钟与其外部的参考时钟保持同步。当参考时钟的频率或相位发生改变时,锁相环会检测到这种变化,并且通过其内部的反馈系统来调节输出频率,直到两者重新同步,这种同步又称为“锁相”(Phase-locked)。

应用领域

锁相环在众多领域有应用,如无线通信、数字电视、广播等。具体的应用范围包括但不限于:

- 无线通信系统收发模块 (Transceiver)

- 数据及时钟恢复电路 (Clock and Data Recovery - CDR)

- 频率综合电路 (Frequency synthesizer)

- 跳频通信 (Frequency-hopping spread spectrum - FHSS)

- 数字电视接收机

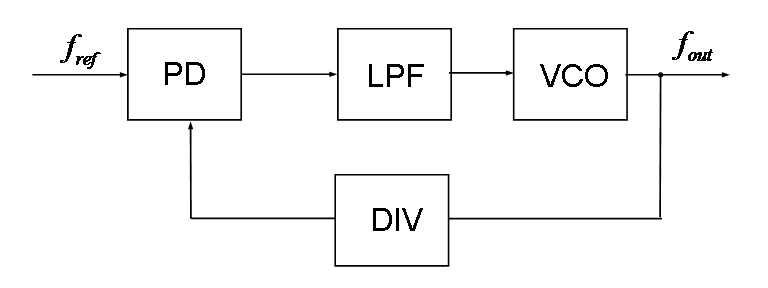

一个锁相环电路通常由以下模块构成:

每个模块的简单原理描述如下:

- 鉴频鉴相器: 对输入的参考信号信号和反馈回路的信号进行频率和相位的比较,输出一个代表两者差异的信号至低通滤波器。

- 低通滤波器: 将输入信号中的高频成分滤除,保留直流部分送至压控振荡器。

- 压控振荡器: 输出一个周期信号,其频率由输入电压所控制。

- 反馈回路 : 将压控振荡器输出的信号送回至鉴频鉴相器。通常压控振荡器的输出信号的频率大于参考信号的频率,因此需在此加入分频器以降低频率。

878

878

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?