时钟

I.MX6U 系列标准的工作频率为 528MHz.

Boot ROM的默认配置为 396MHz.

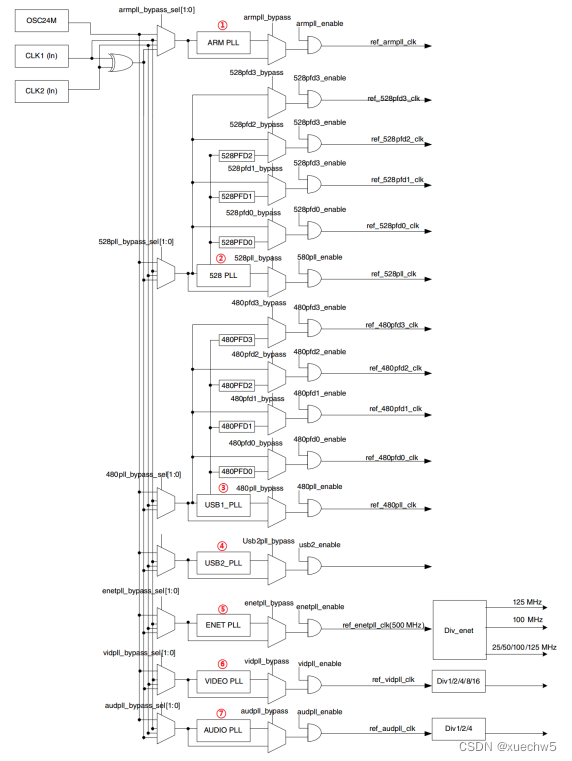

1. 时钟来源

24MHz 晶振是 I.MX6U 内核和其它外设的时钟源

32.768KHz 晶振是 I.MX6U 的 RTC 时钟源

2. 7路PLL时钟源

- ARM_PLL (PLL1):

ARM内核使用, 可通过寄存器CCM_ANALOG_PLL_ARMn控制. - 528_PLL(PLL2):

固定的22倍频, 不可修改. 分出了4路PFD, PLL2_PFD0~PLL2_PFD3. 528_PLL 和 4路PFD 作为内部系统总线的时钟源: 内处理逻辑单元、 DDR 接口、 NAND/NOR 接口等等. - USB1_PLL(PLL3):

固定的 20 倍频(480MHz), 有4路PFD也可以作为其他外设的时钟源. - USB2_PLL(PLL7):

给 USB2PHY 使用的。固定为 20倍频. - ENET_PLL(PLL6):

固定为 20+5/6 倍频, 生成网络所需的时钟. - VIDEO_PLL(PLL5):

用于显示相关的外设, PLL 的倍频可以调整 - AUDIO_PLL(PLL4)

音频相关的外设, 倍频可以调整,

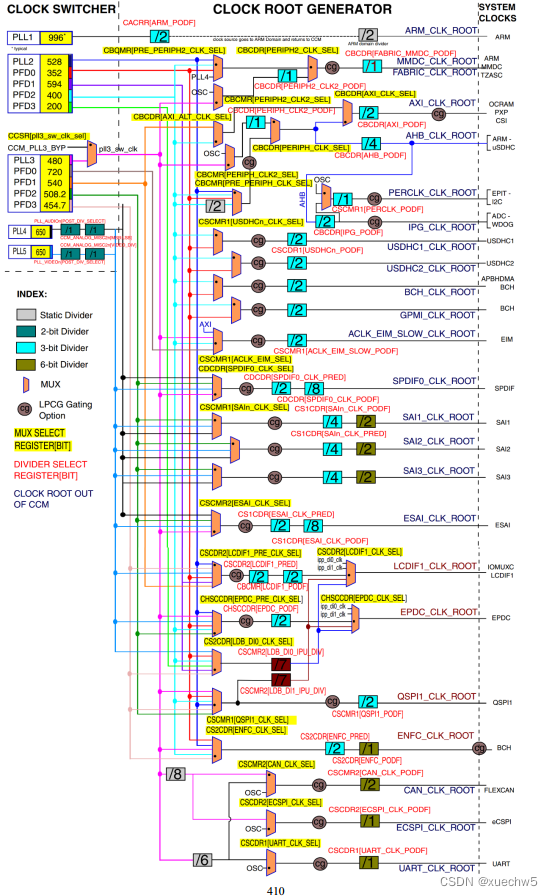

3. 时钟树简介

时钟树分为3个部分: CLOCK_SWITCHER、 CLOCK ROOT GENERATOR 和

SYSTEM CLOCKS.

CLOCK_SWITCHER: 7 路 PLL 和8 路 PFD

SYSTEM CLOCKS: 直接提供给外设的时钟.

CLOCK ROOT GENERATOR: 选择时钟源, 控制开关, 配置分频.

4. 内核时钟设置

将 I.MX6U 的主频设置为 528MHz

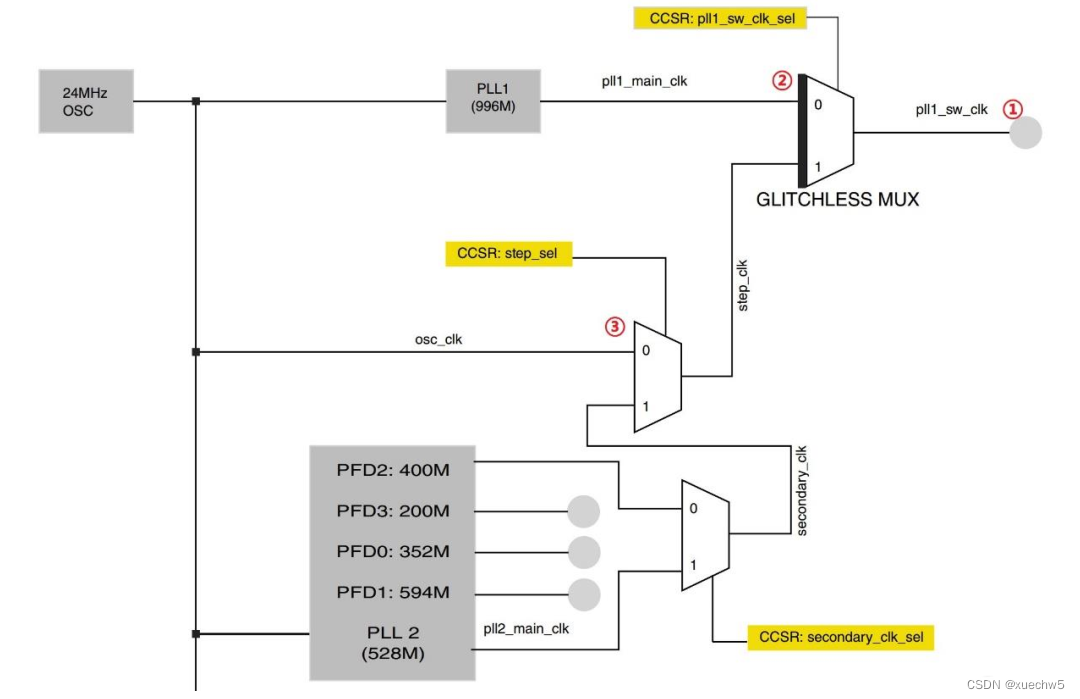

(1) 时钟树的配置

<1> 时钟源为 PLL1, 可以修改PLL1的频率.

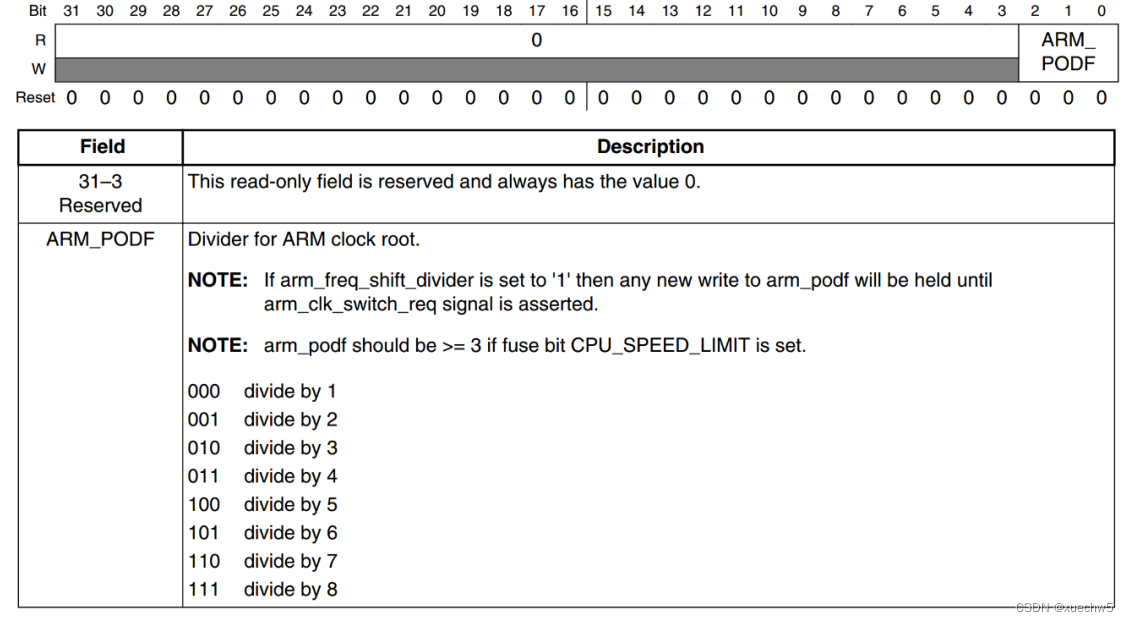

<2> 2分频: CCM_CACRR[ARM_PODF]: 可以选择 1/2/4/8 分频.

<3> 此处没有进行 2 分频

<4> ARM_CLK_ROOT: 直接输出给ARM内核的时钟.

PLL1 可配置为1056MHz, ARM_PODF配置为2分频, 最终的输出为 528MHz.

关于寄存器: CCM_CACRR

(2) ARM PLL频率的配置

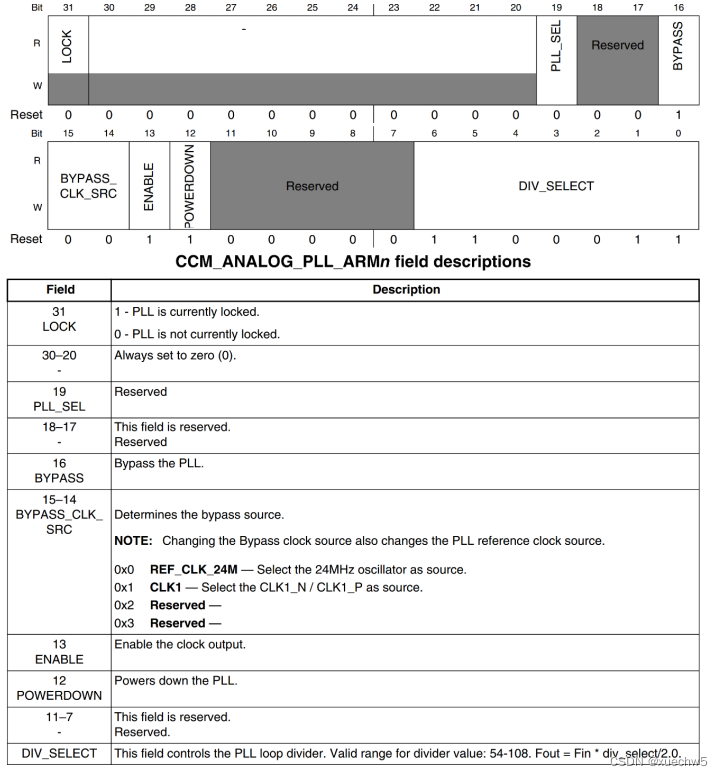

PLL1 的频率可以通过寄存器 CCM_ANALOG_PLL_ARMn 来设置:

ENABLE: 时钟输出使能位,此位设置为 1 使能 PLL1 输出,

DIV_SELECT: PLL1 CLK = Fin * div_seclec/2.0 (Fin=24MHz), 54~108(648M-1296M). 1056MHz对用88.

(3) ARM PLL备用时钟源

PLL1配置过程中, 需要把PLL1的时钟源配置为备用的时钟: OSC_CLK(24MHz).

<1> pll1_sw_clk: PLL1 的最终输出频率

<2> CCM_CCSR [PLL1_SW_CLK_SEL]: 用来配置源: pll1_main_clk 或 step_clk

<3> CCM_CCSR[STEP_SEL]: step_clk 选择 备用时钟osc_clk(24MHz)

(4) ARM PLL配置的流程

- CCSR 的 STEP_SEL 位,设置 step_clk 的时钟源为 24M 的晶振

- CCSR 的 PLL1_SW_CLK_SEL, pll1_sw_clk 的时钟源为step_clk

- CCM_ANALOG_PLL_ARMn, pll1_main_clk(PLL1)设置为 1056MHz

- CCSR的 PLL1_SW_CLK_SEL, pll1_sw_clk 的时钟源切换回 pll1_main_clk(1056MHz)

- CCM_CACRR 的 ARM_PODF 为 2 分频

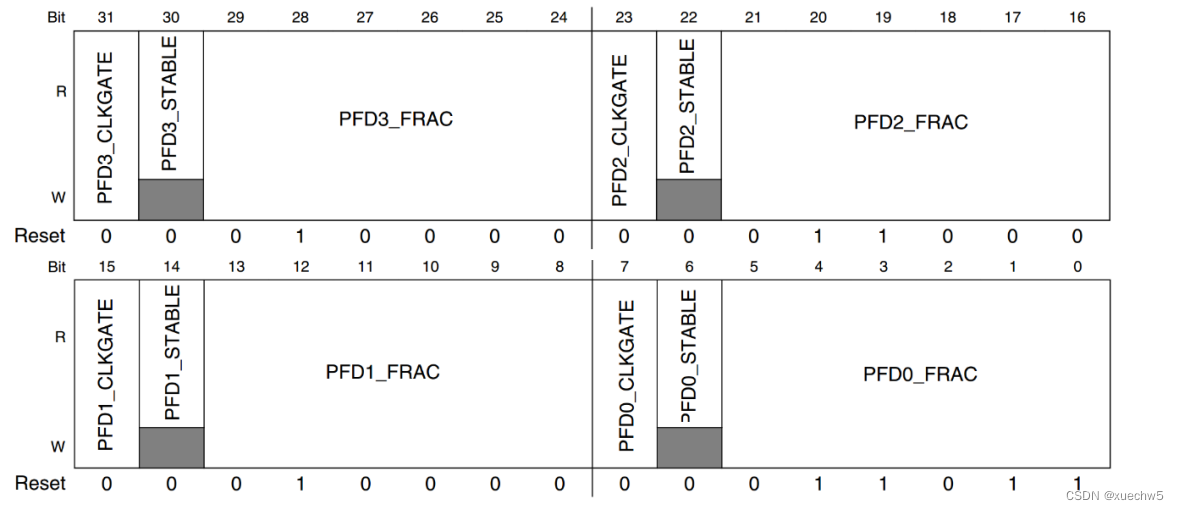

5. PFD 时钟设置

PLL2、 PLL3为固定的时钟, 可以配置4 路 PFD的频率, 寄存器分别是:

CCM_ANALOG_PFD_528n 和 CCM_ANALOG_PFD_480n

PFD0_FRAC: PLL2_PFD0 的分频数: 528*18/PFDX_FRAC(X=1~3), 范围:12 - 35

PFD0_STABLE: 只读, 判断 PLL2_PFD0 是否稳定

PFD0_CLKGATE: 输出使能位,为 1 的时候关闭 PLL2_PFD0 的输出.

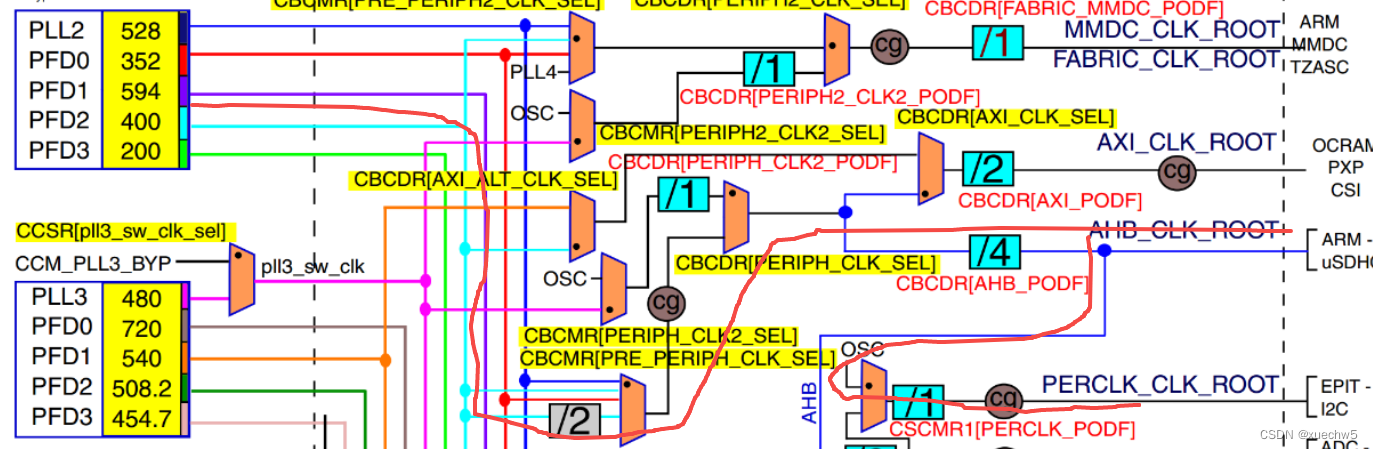

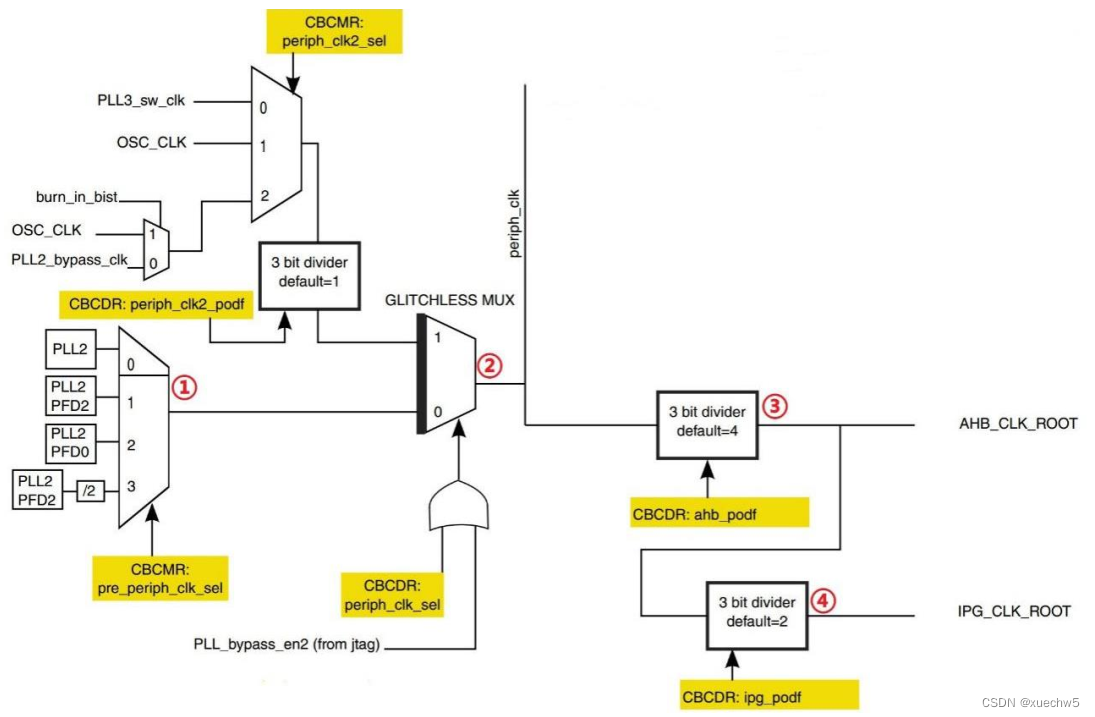

6. AHB、 IPG 和 PERCLK 根时钟设置

时钟的选择路径入上图红线所示,

<1> CBCMR[PRE_PERIPH_CLK_SEL]: PLL2、 PLL2_PFD2、 PLL2_PFD0 和 PLL2_PFD2/2, 默认 PLL2_PFD2

<2> CBCDR[PERIPH_CLK_SEL]: 0 的时候periph_clk=pr_periph_clk

<3> CBCDR[AHB_PODF]: HB_CLK_ROOT 的分频值 1 - 8

<4> CBCDR[IPG_PODF]: IPG_CLK_ROOT 的分频值, 1 - 4(默认2)

4217

4217

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?