原文链接(相关文章合集):OFDM 802.11a的xilinx FPGA实现

目录

1.前言

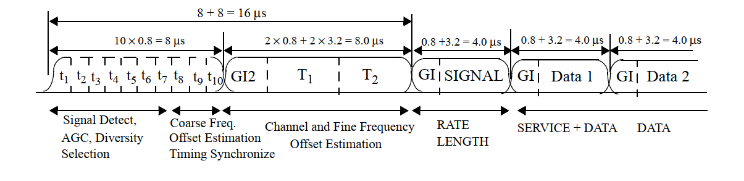

PLCP的前导部分由一组重复10次的短训练序列和一组加了一个长型保护间隔与重复2次的有效OFDM符号组成的长训练序列组成。前面两篇文章分别实现了短训练序列和长训练序列,这节将它们组合起来,成为前导码,共计12个OFDM符号。

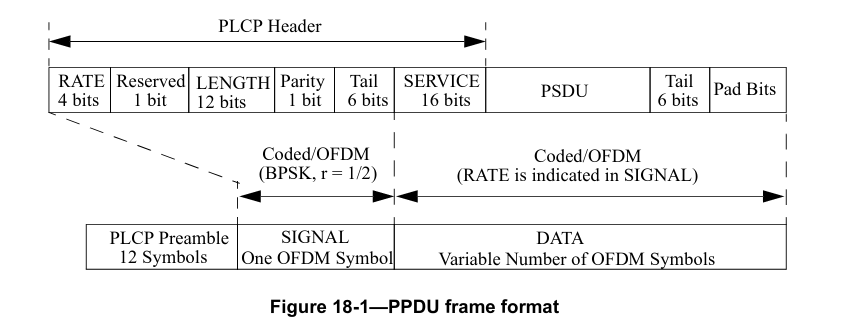

PPDU帧结构

PPDU帧结构

2.原理

前面两篇文章分别实现了短训练序列和长训练序列,在实现短训练序列的时候,输出了161个样值,即多输出了一个样值,是为了在进行长短训练组合的时候加窗使用。PLCP前导部分,前160个数据输出短训练序列的样值,第161个数据输出短训练序列的最后一个输出和长训练序列的第一个输出的和,后续依次输出长训练序列的样值。

3.Matlab 仿真

preamble = [sts_rom(1:(end-1)),sts_rom(end)+lts_rom(1),lts_rom(2:end)]; %帧头加窗

4.硬件实现

always @(posedge clk or negedge rst_n)

if (!rst_n)begin

train_dout <= 16'd0;

train_dout_vld <= 1'b0;

end

else if(STS_dout_last & STS_dout_vld)begin

train_dout <= {STS_dout[15:8] + LTS_dout[15:8],STS_dout[7:0] + LTS_dout[7:0]};

train_dout_vld <= STS_dout_vld;

end

else if(STS_dout_vld)begin

train_dout <= STS_dout;

train_dout_vld <= STS_dout_vld;

end

else if(LTS_dout_vld)begin

train_dout <= LTS_dout;

train_dout_vld <= LTS_dout_vld;

end

else

train_dout_vld <= 1'b0;

assign STS_din_rdy = train_din_rdy;

assign LTS_din_rdy = STS_dout_last | STS_dout_Index == 8'd159 & train_din_rdy;

always @(posedge clk)begin

train_dout_last <= LTS_dout_last;

train_dout_Index <= STS_dout_Index + LTS_dout_Index;

end

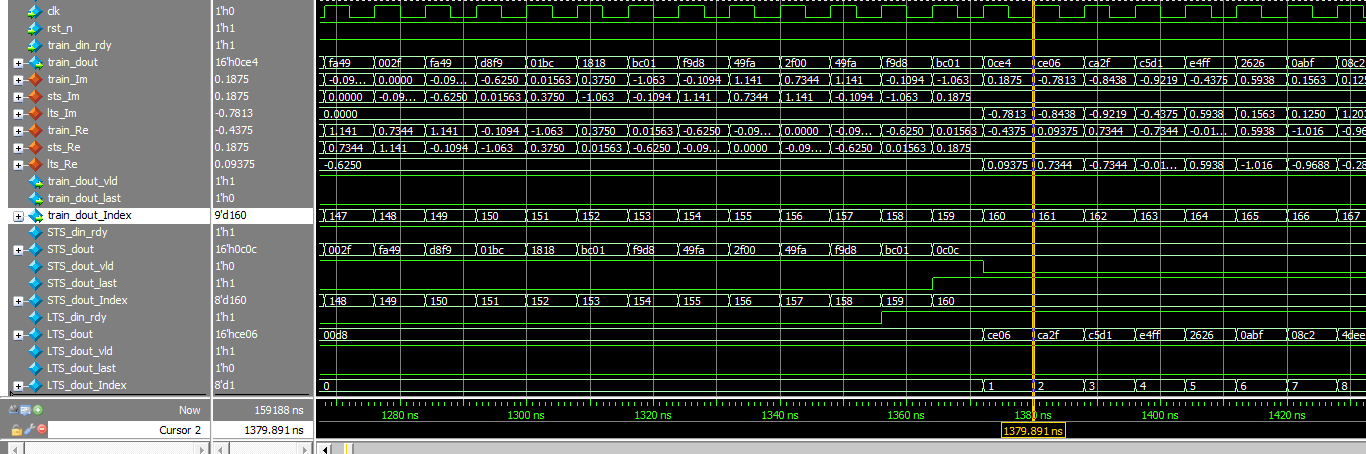

5.ModelSim仿真

ModelSim仿真

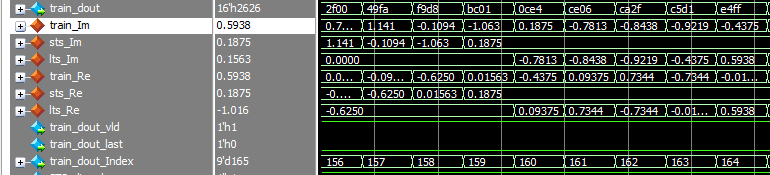

第161个数据处局部放大

6.用Matlab自动化对比仿真结果

%% symbol_train

FPGA_train_dout = readlines('D:/FPGA/OFDM_802.11a_my/TX/matlab/train_data_out.txt','EmptyLineRule','skip')';

display(FPGA_train_dout);

FPGA_Im_train_dout = extractBefore(FPGA_train_dout,9);

FPGA_Re_train_dout = extractAfter(FPGA_train_dout,8);

q = quantizer('fixed','round','saturate',[8,6]);

FPGA_Re_train_dout = bin2num(q,FPGA_Re_train_dout);

FPGA_Im_train_dout = bin2num(q,FPGA_Im_train_dout);

FPGA_Re_train_dout = cell2mat(FPGA_Re_train_dout);

FPGA_Im_train_dout = cell2mat(FPGA_Im_train_dout);

FPGA_train_dout = FPGA_Re_train_dout + 1j*FPGA_Im_train_dout;

preamble_q = num2bin(q,preamble);%量化

preamble = bin2num(q,preamble_q);%反量化

check_train = FPGA_train_dout == preamble.';

display(check_train);

验证结果如下:

check_train =

1×321 logical 数组

列 1 至 40

1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

列 41 至 80

1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

列 81 至 120

1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

列 121 至 160

1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

列 161 至 200

1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

列 201 至 240

1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

列 241 至 280

1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

列 281 至 320

1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

列 321

1

原文链接(相关文章合集):OFDM 802.11a的xilinx FPGA实现OFDM 802.11a的xilinx FPGA实现OFDM 802.11a的xilinx FPGA实现

1943

1943

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?