PLC 与“软件PLC“

早期的PLC 是使用继电器实现逻辑控制的。也就是说,它们完全是硬件实现的。当微处理器出现之后,PLC 内部使用了CPU和程序来实现控制逻辑。现代PLC中也使用了实时操作系统以及各种网络协议。自动控制行业的专家总是将在通用操作系统上运行的PLC控制程序成为“软件PLC”,普遍认为软件PLC 没有PLC 设备可靠,实时性没有PLC设备强。这其实是一种误解。某种意义上讲,现代的PLC 都是软件PLC。它们之间的唯一差别是PLC设备是在特定硬件平台上实现的实时操作系统和程序具有更高的实时性,确定性和稳定性。它们经过了厂商预先反复的测试。确保了软硬件匹配的的更好。如果重视软硬件的相互匹配,在通用硬件平台上,同样能够实现可靠运行的PLC 系统。比如倍福公司的工业电脑就是在微软公司为其定制的windows 下运行。同样非常的可靠。

在实时性方面,大多数PLC 使用实时操作系统(RTOS),比如VxWorks OS。这是一个可靠性,实时性极强的实时操作系统。不过,RTOS的处理能力也是有限的,设想编写一个“巨大”的程序在PLC上运行, 也会出现性能下降问题。只是PLC 设备预留了足够的资源来保证在特定的应用中的需要,通俗地讲,“就是杀鸡用牛刀”。

实时操作系统本质上是操作系统,只是内部调度算法上考虑了对外部事件的响应事件而已。但是令人遗憾的是,几乎所有的OS 调度算法都只是“尽力而为”。PLC 的做法是预留了足够的硬件算力,来确保应用程序满足实时性的要求。为了提高PLC 的算力,高性能的PLC内部采用了FPGA 来实现实时性要求高的功能,例如产生高速PWM 和脉冲输出,运动控制模块,脉冲计数,电机编解码器等。

开放性的挑战

现代控制系统对PLC 提出了越来越高的要求,例如导入更复杂的控制算法,AI模块和云端交互功能,它们对PLC 内部CPU/FPGA 提出更高的算力需求,另一方面,控制系统朝着开放性方向发展。第三方开发者和最终用户参与PLC 功能块的开发。在PLC 的生命周期内会变更程序和功能块升级。如此一来,PLC厂商其实能难预估应用程序对算力的预估。并且难以承诺产品的实时性。而是又第三方开发者和用户能够更高效地方式来保证系统的实时性能。

IEC61499 的实时性

目前大多数的IEC61499 功能块和运行时是软件实现,并且在PC或者Linux 设备上运行。因此IEC61499 目前是一个典型的“软”控制器。

问题的确是存在的,IEC61499 运行时的实时性和确定性的确令人担心的。为了解决这个问题,可以吸取PLC 的方式

- 提高设备内部的SOC算力的富余量

- 采取FPGA 对功能块加速

- 硬件实现实时功能块网络。

采取FPGA 对功能块加速

通过对一些对算力比较大的功能块使用FPGA 实现,能够缩短功能块的执行时间。提高功能块网络的实时性。

功能块内部的算法由FPGA IP来实现。FB实现PS/PL 之间的数据交换。类似的FB包括:

- 高速PWM 发生器

- 高速脉冲计数器

- FFT 快速傅里叶

- 数字滤波器

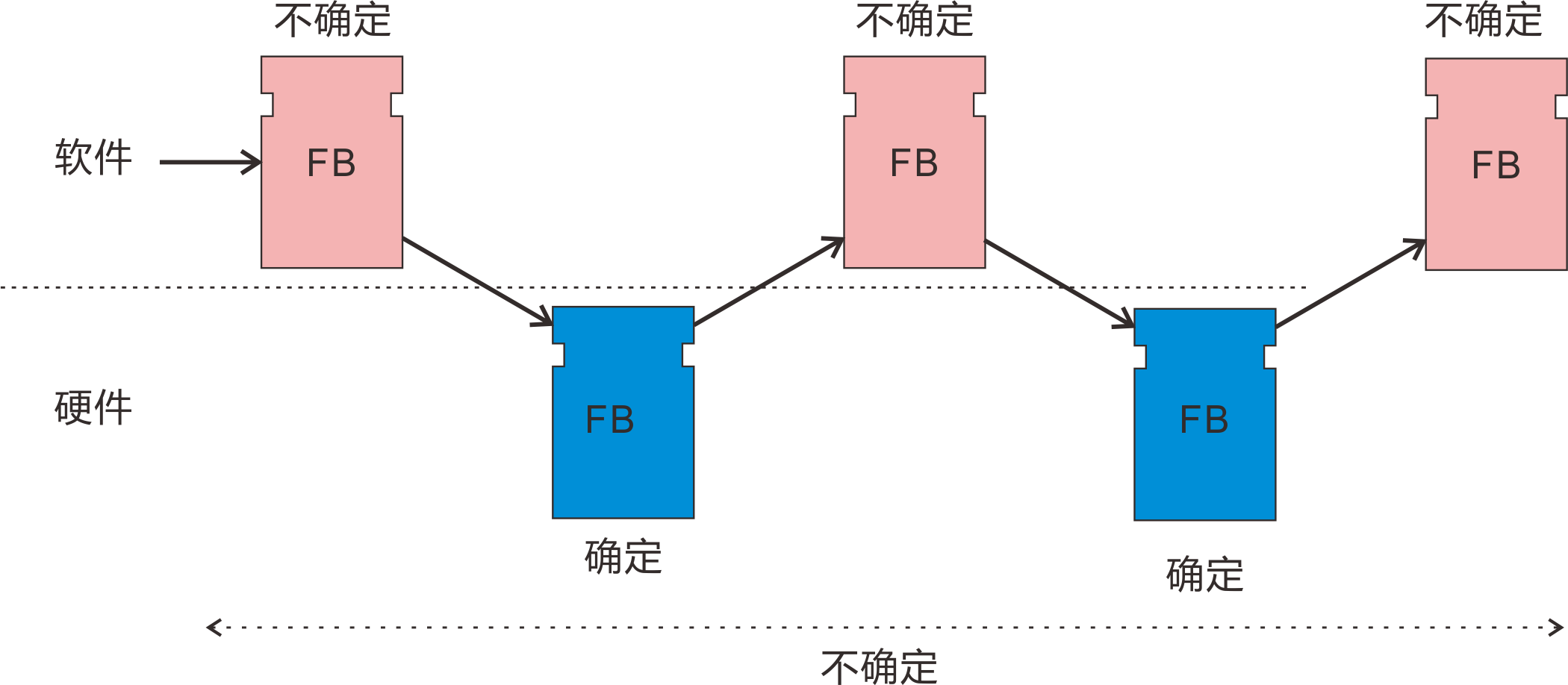

不过这种方式具有局限性,功能块之间的数据和事件的传递和功能块的调度仍然是由软件实现的,存在着非确定性。对于像高速电机控制中,控制环由多个功能块构造而成,如果由软件实现功能块之间的数据传递,整个系统的实时性,确定性难以保证。

硬件实现实时功能块网络

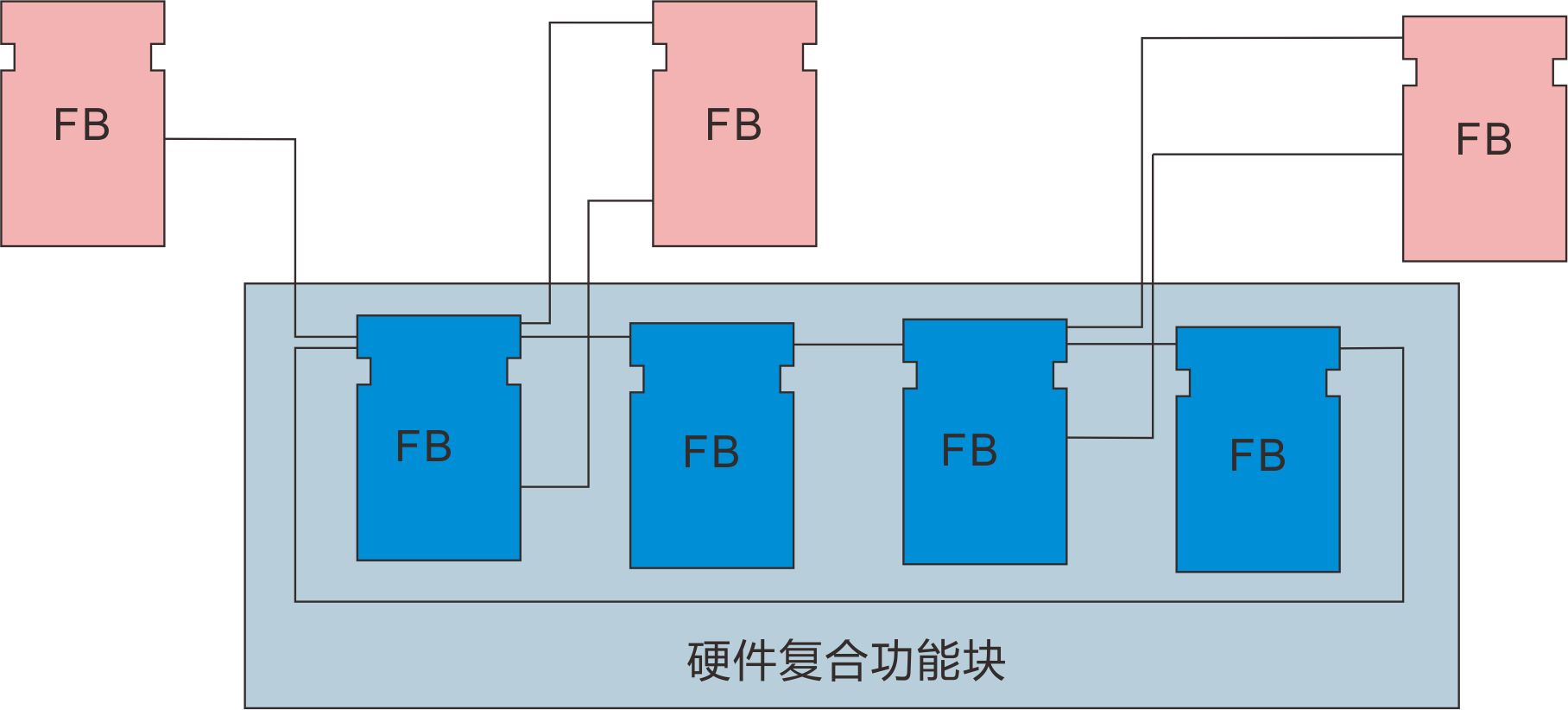

将实时处理要求高的一端功能块网络(譬如一个PID 环控制)使用FPGA来实现,而配置,监控和事务交互功能块仍然由软件实现。这样完整的硬件实现,避免了软件的干预而造成不确定性和实时性。并且能够高速地处理控制算法和信号处理。

某一段功能块网络的硬件实现最好的方法是将这些硬件功能块网封装成为复合功能块。通过工具软件将这个复合功能块转换成为FPGA 硬件语言(HDL,verilog等)。由FPGA开发工具vivado 转换成FPGA 比特流。

IEC61499 硬件功能块的实现

笔者初步开始尝试FPGA 实现IEC61499 的方法,使用xilinx zynq 作为SOC平台。由于IEC61499 并不普及,网络上相关的文章非常少。也只能自己慢慢摸索

在IEC61499 运行时的实现中,功能块大多数采用了C++ 类实现,因此我们希望采用HLS 来实现C++类为基础的IEC61499 功能块,但是发现HLS 几乎是为复杂算法而准备的,使用C++类的介绍非常少,如果去实现与数字逻辑非常接近的功能块,好像不如verilog 语言更简单。

verilog 语言以module 为一个编程单元,相当于C语言中的一个函数(function),但是由于硬件的特殊性,所有的变量都是静态分配的,所以与C++的类又有几分相似,内部实现ECC状态机和算法十分方便。与此同时,verlog 的功能块能够实例化。在另外的模块中实现实例。与IEC61499 功能块实例化十分相像。使用verilog 语言编写IEC61499 硬件功能块更加合适。

例子1-E_CTD 功能块

下面是笔者使用verilog 实现的一个E_CTD 计数器

`timescale 10ns / 1ns

module e_ctd(cd,ld,cdo,ldo,pv,cv,q);

input cd,ld;

input [15:0] pv;

output reg q,cdo,ldo;

output reg [15:0] cv;

reg [15:0] v;

always@(posedge cd)

begin

if (cv==0)begin

cv <= v;

#5 q=1;

end else

begin

cv <= cv - 1;

#5 q=0;

end

#5 cdo=1;

#5 cdo=0;

end

always@(posedge ld)

begin

v <= pv;

cv <= pv;

ldo=1;

#10 ldo=0;

end

endmodule

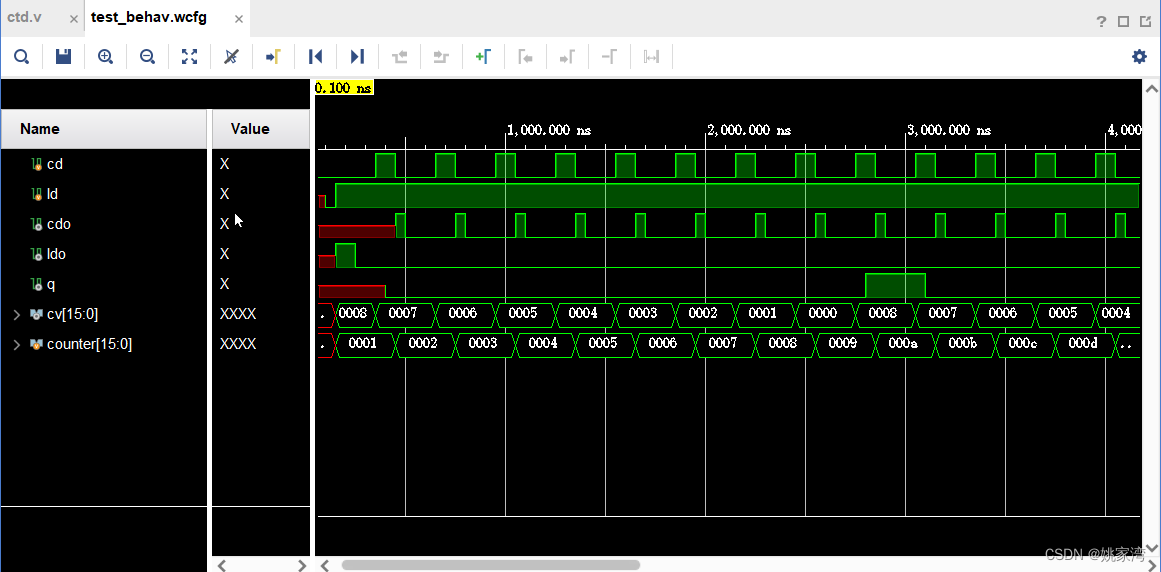

在上面的程序中,忽略了ECC 的实现。module e_ctd是功能块,下面的test 是仿真程序

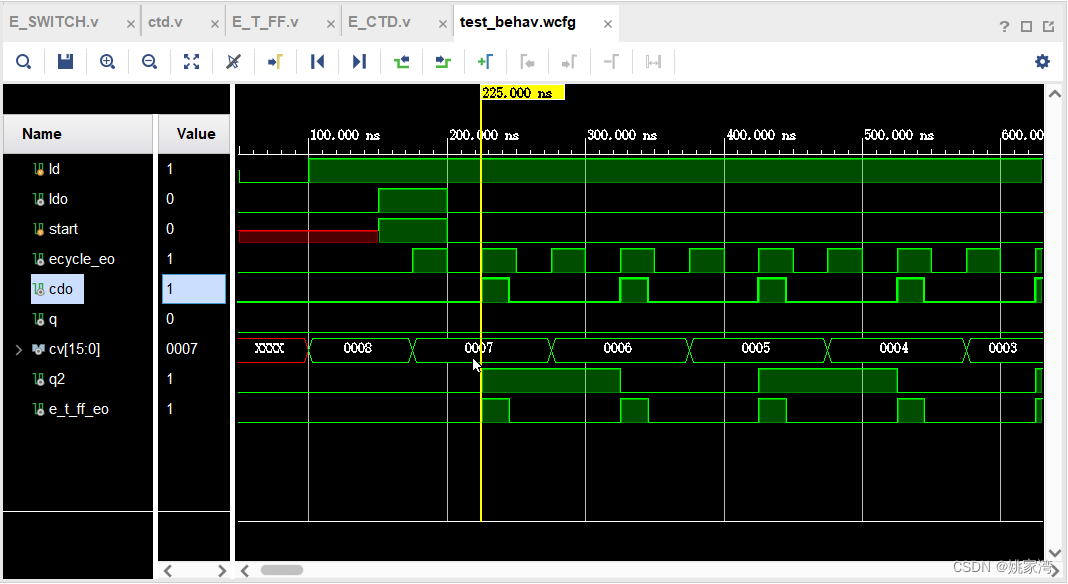

仿真的结果

IEC61499 基本功能块都是底层逻辑构建得,使用verilog 语言描写非常合适,如果要深入研究IEC61499 功能块硬件化得课题,需要开发 hardware function block 库。在这个基础上开发一些构建工具(XML->verilog)

例2 -E_CYCLE 功能块

`timescale 10ns / 1ns

module e_cycle(start,stop,eo);

input start,stop;

output reg eo;

parameter FREQ = 100000; // in constraint_mode

parameter DUTY = 50; // in percentage

parameter clk_pd = 1.0/(FREQ * 1e3) * 1e9;

parameter clk_on = DUTY/100.0 * clk_pd;

parameter clk_off = (100.0 - DUTY)/100.0 * clk_pd;

reg start_clk;

initial begin

eo <= 0;

start_clk <= 0;

end

always @(posedge start) begin

if (start)

start_clk=1;

end

always @(posedge stop) begin

if (stop)

start_clk=0;

end

always @(posedge start_clk) begin

if (start_clk) begin

while (start_clk) begin

#(clk_on) eo=1;

#(clk_off) eo=0;

end

end

end

endmodule

例3 -E_T_FF

`timescale 10ns / 1ns

module E_T_FF(clk,eo,q);

input clk;

output reg eo,q;

initial

begin

q=0;

eo=0;

end

always @(posedge clk) begin

if (clk)

begin

q <=~q;

eo=1;

#2 eo=0;

end

end

endmodule测试程序

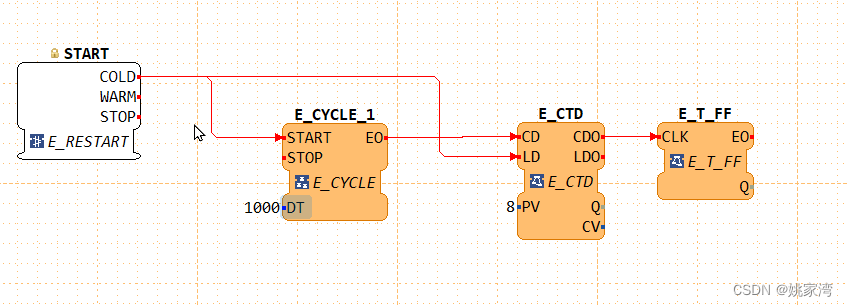

测试程序完成IEC61499 功能块网络。

`timescale 10ns / 1ns

module test();

reg cd,ld;

wire cdo,ldo,q,q2;

wire [15:0] cv;

wire ecycle_eo,e_t_ff_eo;

reg start,stop;

E_CYCLE #(.FREQ(200000)) ecycle1(start,stop,ecycle_eo);

E_CTD #(.PV(8)) etcd1(ecycle_eo,ld,cdo,ldo,cv,q);

E_T_FF e_t_ff(cdo,e_t_ff_eo,q2);

initial

begin

#5 ld =0;

#5 ld=1;

#5 start=1;

#5 start=0;

end

initial

$monitor("at time %t ,",$time,"CDO=%b,LDO=%b,Q=%b,CV=%b",ecycle_eo,ldo, q,q2);

endmodule 仿真结果

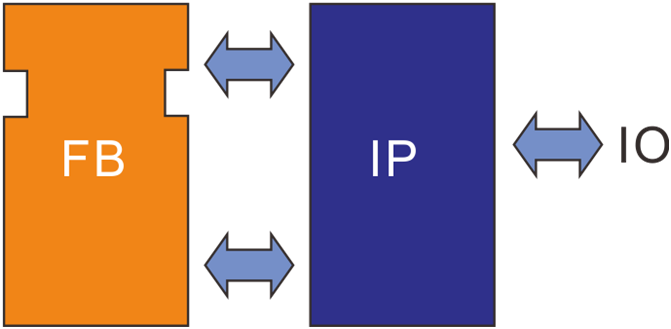

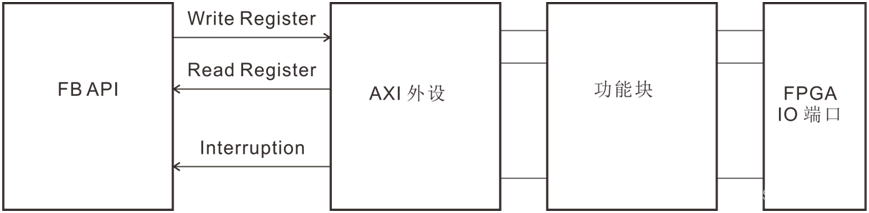

软硬件接口

实现IEC61499 硬件功能块,需要设计一个统一的软硬件接口。如下图所示。

- IEC61499 运行时通过HFB API 访问硬件功能块

API 包括:

Event_Action() 向硬件FB 发送事件

Put_Data 向FB 发送数据

Get_Data读取FB数据

Event_Notify() 处理FB 输出的事件中断。(也可以是查询方式)

- ARM 处理器通过AXI-lite 接口与PL 端的AXI 外设IP 通信

write Register

readRegister

interrupt processing

AXI 外设寄存器

输入事件寄存器(Input Event register)

输出事件寄存器(Output Event register)

输入数据寄存器(Input Data Register)

输出数据寄存器(Output Data Register)

操作过程

事件输入

当需要向功能块注入事件时,运行时向输入事件寄存器对应的bit 位置 1,硬件FB 检测输入事件寄存器的状态,一旦发现变化,转向事件处理。完成后,清除对应的状态位。

事件输出

当功能块输出一个事件时,在输出事件寄存器相关位置1,并产生一个中断信号。由运行时软件读取事件寄存器,并且清零。

数据输入/输出

由软件直接写入或读取数据输入寄存器。这一点与软件实现有所不同,软件FB 处理时是通过 getDataIn根据connection 去数据源功能块中读取的。对于硬件FB,当事件来临时,API要根据事件-数据关联性,调用getDataIn 读取数据后需要写入数据输入寄存器中。

结束语

这只是一个开头,还有许多工作要做

1 软件功能块与硬件功能块的接口的实现方式

2 如何将IEC61499 复合功能块的XML 描述转换成verilog 的模块。

3 如何调用HLS 产生的IP

欢迎感兴趣的读者共同交流。这些技术同样可以应用到IEC61131-3 PLC 的高性能实现中。笔者认为作为后来者,国产控制设备需要提高更强大的性能,才可能让用户砰然心动。

242

242

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?